国際特許分類[H01L23/532]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814) | 半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851) | 材料に特徴のあるもの (313)

国際特許分類[H01L23/532]に分類される特許

311 - 313 / 313

スルーシリコンビア(TSV)内にチップ−チップ間、チップ−ウェハー間及びウェハー−ウェハー間の銅インターコネクトを電着するプロセス

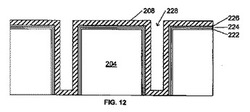

シリコン基板内のビア内に高純度の銅を電着し、スルーシリコンビア(TSV)を形成するプロセスである。本プロセスは、電解銅めっきシステム内の電解槽内にシリコン基板を浸漬するステップと、高純度の銅を電着してTSVを形成するのに十分な時間の間、電圧を印加するステップとを含み、電解槽が酸、銅イオンの発生源、第一鉄イオン及び/又は第二鉄イオンの発生源、及び析出した銅の物理−機械的特性を制御するための少なくとも1つの添加剤とを含み、銅金属の発生源からの銅イオンを溶解することによって電着されることになる付加的な銅イオンを提供するために、前記槽内でFe2+/Fe3+レドックス系が、確立される。 (もっと読む)

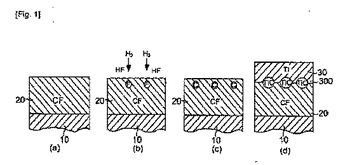

フッ化炭素膜の表面処理

半導体デバイスの製造方法は、絶縁性層をアニーリングする工程と、金属元素を含んだ障壁層を前記絶縁性層上に形成する工程とを含んでいる。前記絶縁性層は、フッ化炭素(CFx)膜を含んでいる。前記障壁層は、前記アニーリング工程後に、高温スパッタリングプロセスによって形成される。  (もっと読む)

(もっと読む)

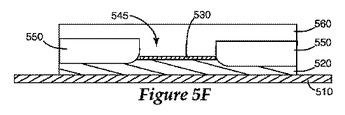

陽極酸化された薄膜構造用の電気的接続

第1の薄膜メタライゼーション層と第2の薄膜メタライゼーション層とを電気的に接続する回路ビアの形成のための手法が述べられる。ビアの形成では、第1のメタライゼーション層の陽極酸化に先立って、ビア接続領域に配置される陽極酸化バリア及び/又は補助パッドを使用する。バリアを形成するために使用される材料は、陽極酸化の際に陽極酸化液を実質的に透過せず、導電層とバリアとの間に酸化物が形成されることを阻止するものである。補助パッドは非陽極酸化性であり、陽極酸化の際に、パッドを通じて電流が流れることを実質的に防止するためにバリアによって覆われる。陽極酸化の後に、バリアは除去される。補助パッドが充分な導電性を有する場合には、バリアの除去後に第1のメタライゼーション層上に残存されてもよい。第2のメタライゼーション層が陽極酸化層上に配置され、ビア接続領域において第1の導電層と電気的に接触する。  (もっと読む)

(もっと読む)

311 - 313 / 313

[ Back to top ]