国際特許分類[H03F3/217]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 電力増幅器,例.B級増幅器,C級増幅器 (2,000) | 半導体装置のみをもつもの (844) | D級電力増幅器;スイッチング増幅器 (612)

国際特許分類[H03F3/217]に分類される特許

1 - 10 / 612

スイッチングアンプの制御回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

D級増幅器

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

全差動型帰還増幅回路および電気機器

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

スイッチングアンプ

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

パルス幅変調回路およびスイッチングアンプ

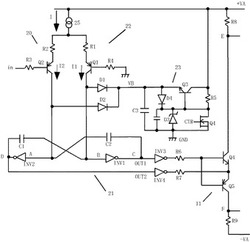

【課題】 電源オフ状態に移行する際に、漏れ電流によって蓄積手段が充電され、2つの出力素子の入力が共にハイレベルになり、出力が共にローレベルになり、次に電源オン状態に移行する際に、パルス幅変調動作を開始することができないとい問題を解決でき、かつ、入力信号に正確に対応したパルス幅変調信号を出力することができるパルス幅変調回路を提供する。

【解決手段】 パルス幅変調回路20は、電源オン状態から電源オフ状態に移行する際に、オン状態に制御されることにより、漏れ電流の原因となる電源電圧V2を接地電位に瞬時に放電させ、0Vにさせるスイッチ手段Q4を備える。スイッチ手段Q4は、ダイオードD1、D2の各カソード側に接続されているので、電流I1、I2によってコンデンサC1、C2を充電する際に、コンデンサC1、C2から電気的に分離された状態になるので、C1、C2の充電に誤差を与えない。

(もっと読む)

オーディオ装置

【課題】本発明は、オーディオ装置において、スピーカの劣化を防止することを目的とするものである。

【解決手段】本発明は、音声入力端子4と、この音声入力端子4に接続されたPWM変調器7と、このPWM変調器7の出力側に接続された増幅器8と、この増幅器8の出力側に接続されたLCフィルタ9と、このLCフィルタ9の出力側に接続された音声出力端子10とを備え、前記LCフィルタ9にフィルタ電流検出器12、あるいは、スピーカ電流検出器を接続し、これらのフィルタ電流検出器、あるいは、スピーカ電流検出器に制御器13を接続し、この制御器13により前記増幅器8を制御する構成とした。

(もっと読む)

電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

スイッチング回路及び包絡線信号増幅器

【課題】複数のスイッチング素子にて増幅したPWM信号を低損失で合成し、変調信号を復調することが可能なスイッチング回路、及び該スイッチング回路を備える包絡線信号増幅器を提供する。

【解決手段】本発明の一実施形態のスイッチング回路33は、N個(Nは2以上の整数)のトランジスタM1〜Mnのスイッチングを制御するための各制御端子をN−1個のコイルL1を介して縦続接続する接続回路と、一端が直流電源に電気的に接続されるコイルL2の他端及びトランジスタM1〜Mnの各一端の間に各別に接続されたコイルL3とを備え、接続回路の入力端子に入力されるPWM信号にて、スイッチング素子M1〜Mnを順次スイッチングさせるようにしてある。また、スイッチング回路33は、コイルL2の一端側又は他端側に縦続接続されるように挿入されたトランジスタM0を更に備える。

(もっと読む)

1 - 10 / 612

[ Back to top ]