国際特許分類[H03F3/42]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 二つ以上の増幅素子が負荷に直列で直流通路をなし,かつ各素子の制御電極が少くとも入力信号の一部で励振される増幅器,例.いわゆるトーテムポール増幅器 (12)

国際特許分類[H03F3/42]の下位に属する分類

電子管のみをもつもの

国際特許分類[H03F3/42]に分類される特許

1 - 10 / 12

半導体装置

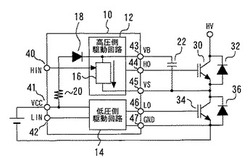

【課題】本発明は、ブートストラップダイオードを備える半導体装置の省エネルギー化ができる半導体装置を提供することを目的とする。

【解決手段】トーテムポール接続された高圧側パワーデバイスと低圧側パワーデバイスの駆動を制御する半導体装置であって、回路負荷を有し、該高圧側パワーデバイスを制御する高圧側駆動回路と、該低圧側パワーデバイスを制御する低圧側駆動回路と、該低圧側駆動回路と接続され該低圧側駆動回路の電源電位であるVCC電位を該低圧側駆動回路に与えるVCC端子と、アノードが該VCC端子と接続されカソードが該高圧側駆動回路と接続され、該高圧側駆動回路の電源電位であるVB電位の充電に用いられるブートストラップダイオードと、該VB電位が該VCC電位よりも小さくなる前に該回路負荷を遮断する手段とを備えたことを特徴とする。

(もっと読む)

出力駆動回路

【課題】出力信号が不安定になる可能性があった。

【解決手段】第1、第2の電源間に直列接続される第1、第2のトランジスタを備えた出力部と、入力パルス信号に応じて、前記第1のトランジスタがオン状態となるとき、前記第1の電源端子と前記第1のトランジスタの制御端子を導通させオン状態に駆動させる第1の駆動部と、一端が第1のノードとの間に接続されるインダクタと、前記第1のスイッチング素子の少なくともオフ後にオン状態となることで、前記第1のノードと前記第1のトランジスタの制御端子を導通し、前記第1の所定の期間後に前記第1のノードに供給される前記インダクタの逆起電力を、前記第1のトランジスタの制御端子に伝達する第2のスイッチング素子と、を有する出力駆動回路。

(もっと読む)

出力駆動回路

【課題】従来の出力駆動回路では、出力電圧が不安定になることがあった。

【解決手段】本発明は、出力段電源電圧をドレインに印加されソースが第1のノードと接続されるハイサイドトランジスタと、接地電圧をソースに印加されドレインが第1のノードと接続されるロウサイドトランジスタを備えるトーテムポール型の出力部と、第1のノードに一端を接続され、ハイサイドトランジスタのオフ時の充電電荷を、オン時にゲートに供給する容量素子を備えるブートストラップ部を有する出力駆動回路であって、駆動回路電源電圧とハイサイドトランジスタのゲート間に接続され、ハイサイドトランジスタをオンする場合に導通状態となる第1のトランジスタと、容量素子の他端とハイサイドトランジスタのゲート間に接続され、ハイサイドトランジスタをオンする場合に導通状態となる第2のトランジスタを有する出力駆動回路である。

(もっと読む)

低歪率増幅器

【課題】低歪みと大出力電圧を両立することができる低歪率増幅器を提供する。

【解決手段】増幅回路として、2つの増幅素子Q1、Q2をトーテムポール接続してなるSRPP回路を備える。その出力回路からはコンデンサが除かれている。当該出力回路には、予め定められた電流を供給する定電流回路Q3、VR2と、前記出力回路にフォールデッドカスコード接続されているトランジスタQ4と、トランジスタQ4のベース端子の電位を予め定められた値に保持する定電圧回路D、R3と、トランジスタQ4の出力電流を電圧に変換する負荷抵抗RLと、が設けられている。

(もっと読む)

ドライバー出力回路

【課題】ドライブ能力の向上と共に、消費電流の低減を図る。

【解決手段】出力段を構成する第2及び第3のトランジスタ2,3のベース電流をそれぞれ補償するため第1及び第2のベース電流補償回路31,32が設けられ、第2及び第3のトランジスタ2,3のベース電流が十分確保されることによるドライブ能力の向上が図られると共に、第1の定電流源21の出力電流と第1のトランジスタ1へ流れる電流をそれぞれ減らすことができ、それに伴う低電流化が可能となっている。

(もっと読む)

演算増幅器

【課題】消費電流の増大、および、安定性を損なうことなくスルーレートを向上させること。

【解決手段】M17のドレインをM5のドレインに接続し、M17のドレインとゲートをM18のゲートに接続することで構成したP型カレントミラー回路6と、M24のドレインとゲートをM18のドレインに接続し、M25のドレインを位相補償容量C1に接続し、M26のドレインを位相補償容量C2に接続したN型カレントミラー回路9と、M19のドレインをM3のドレインに接続し、M19のドレインとゲートをM20のゲートに接続することで構成したN型MOSカレントミラー回路7と、M21のドレインとゲートをM20のドレインに接続し、トランジスタM22のドレインを位相補償容量C1に接続し、M23のドレインを位相補償容量C2に接続したP型カレントミラー回路8とを具備する。

(もっと読む)

駆動回路

【課題】回路の電圧変動を1個のトランジスタで補償するようにした低電流回路では許容されるコレクタ損失の大きい高価なトランジスタを適用する必要があり、さらに発熱対策のために装置が大型化する。

【解決手段】負荷(発光ダイオードD5〜D34)にDC電源からの直流出力Vinを供給する駆動回路であって、前記直流出力をベース電流に用いて前記負荷の回路電流を制御する第1のトランジスタQ1に加えて、Q1のコレクタ電圧をベース電圧として作動する第2のトランジスタQ2と、Q2のコレクタ電圧によってベース電圧が変化し、前記直流出力から負荷への供給電流を制御する第3のトランジスタQ3とを備え、Q3のベース端子から接地側に流す電流をQ2により制御することにより、電源電圧の変動に伴う回路電圧の変化を、Q1とQ3とで分散して補償させる。

(もっと読む)

フィードバックバイアス回路

【課題】定電圧源Vccの消耗又は交換による変動や、温度変動やウエハ間やロット間の素子特性が変動してもトランジスタのバイアス電流をフィードバック制御すること。

【解決手段】制御対象である増幅器のトランジスタのコレクタ電流又はドレイン電流を、第1の電位差ΔV1として検出する。これを基準電位Vrefと比較して、第2の電位差ΔV2として検出する。増幅器のコレクタ電流又はドレイン電流自体を、第1の電位差ΔV1として検出するので、フィードバック制御においてもベース電位又はゲート電位は定電圧源Vccの変動を受けない。更に基準電位Vrefとして温度変化に対して変動の小さい又は変動がほとんど無いものを用いれば、以降のフィードバック制御においてもベース電位又はゲート電位は温度変化による影響を受けない。これは言わば絶対比較により、コレクタのバイアス電流を一定とするものである。

(もっと読む)

アナログバッファ回路

【課題】 線形の入出力電圧特性と高入力インピーダンスとを持ち、簡単な構成のアナログバッファ回路を提供する。

【解決手段】 第1のPMOS11,NMOS12及び第2のPMOS13を、VDDとGNDとの間に、この順で直列に接続する。全てのMOS11〜13のゲートに入力端子を共通接続し、NMOS12と第2のPMOS13の接続点に出力端子を接続する。所定範囲の入力電圧Vinが入力端子に与えら得ると、入力電圧に等しい出力電圧Voutが得られる。

(もっと読む)

増幅器出力ステージを制御する制御回路を備える集積回路装置及びそのドライビング方法

【課題】出力電圧を発生させる増幅回路を備える集積回路装置を提供する。

【解決手段】バイアス制御回路(215,216)は、制御信号(SW)の状態に基づいてその出力からバイアス制御電圧(VB1,VB2)または出力電圧(VOUT+,VOUT−)を選択的に発生させる。出力ステージドライバー回路(213)は、バイアス制御回路の出力から発生した電圧に応答して動作する。

(もっと読む)

1 - 10 / 12

[ Back to top ]