国際特許分類[H03J7/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 同調共振回路;選択共振回路 (388) | 自動周波数制御;全帯域にわたる自動周波数掃引 (137) | 自動周波数制御 (48) | 周波数制御が非機械的調整素子の電気特性の変化によって達成されるもの,または周波数制御素子の性質が重要でないもの (17) | 計数器または周波数分割器を用いるもの (7)

国際特許分類[H03J7/06]に分類される特許

1 - 7 / 7

周波数補正回路

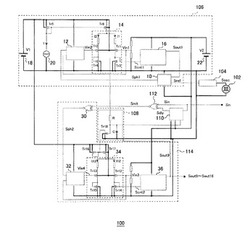

【課題】送信波の周波数に同期された周波数又はその逓倍波を容易かつ正確に出力できる周波数補正回路を提供する。

【解決手段】第1電圧制御発振器16の出力信号と基準発振信号との位相差に応じた位相差信号を第1位相比較器10により生成し、第1ループフィルタ12を介して第1位相差信号に応じた第1発振制御信号により第1制御発振器16の発振をフィードバック制御する第1フェーズロックループ回路106と、第2電圧制御発振器36の出力信号と比較対象信号との位相差に応じた位相差信号を第2位相比較器30により生成し、第2ループフィルタ32を介して第2位相差信号に応じた第2発振制御信号により第2制御発振器36の発振をフィードバック制御する第2フェーズロックループ回路114とを備え、第1発振制御信号に応じて第2発振制御信号を変動させることによって比較対象信号に応じて出力信号をロックする。

(もっと読む)

GPSを含む多機能セルラーアプリケーションにおける基準ソースの必要数を最小限に抑えるシステムおよび送受信機のクロック方式

【解決手段】 自動周波数訂正(AFC)を利用した訂正が実施されていない第1のクロック基準を生成する第1のクロックモジュールを備えるシステムを開示する。グローバルポジショニングシステム(GPS)モジュールは、第1のクロック基準を受信する。セルラー方式送受信機のための集積回路は、第1のクロック基準を受信して、AFCを実行して、AFCを利用した訂正が実施された第2のクロック基準を生成するシステムフェーズロックループを有する。 (もっと読む)

受信機システム

【課題】MCUの負荷を軽減しつつ、局部発振回路の発振周波数の所望の受信周波数からのずれを自動的に修正する。

【解決手段】選局動作時、キャパシタバンク107およびバリキャップVR1の調整に応じた発振周波数により、OSC106が発振する。この際、IF信号の周波数が得られるとAFC動作が開始され、ゲート制御回路121は、発振制御回路122を介してクリスタル発振器131から供給されるクロックCKをカウントすることにより、選局情報などに応じたゲート時間を生成する。このゲート時間にしたがってゲート回路109を制御し、カウンタ回路110により擬似的に計測されたOSC106の発振周波数を、比較回路115により、規格値保持回路114で保持された規格値と比較する。OSC106の発振周波数が規定の周波数範囲内にあると判定されると、その発振周波数を維持すべく、VR2制御回路117がバリキャップVR2を微調整する。

(もっと読む)

受信機システム

【課題】FMラジオ受信機において、妨害信号を受信した場合にも、局部発振回路の発振周波数の所望の受信周波数からのずれを自動的に修正できるようにする。

【解決手段】たとえば、キャパシタバンク107およびバリキャップVR1の調整に応じた発振周波数により、OSC106が発振する。すると、ミキサー103により生成された受信信号が、IF回路104によりIF信号に変換される。この際、IF信号の周波数が得られないと、カウンタ回路110により擬似的に計測されたOSC106の発振周波数を、比較回路115により、N値および規格幅設定値をもとに演算回路113にて規格化され、規格値保持回路114で保持された規格値と比較する。この結果から、判定回路116により、OSC106の発振周波数が規定の周波数範囲内にないと判定されると、そのずれを修正すべく、VR2制御回路117がバリキャップVR2を微調整する。

(もっと読む)

受信機及びそのプログラム

【課題】短時間で精度の高い自動周波数調整を行うこと。

【解決手段】受信した高周波信号の中央周波数と受信周波数の差を検出する周波数誤差検出手段105を備え間欠受信を行う受信機101において、受信時に周波数誤差検出手段105により周波数誤差値を検出し、n回目の受信開始時においてn−1回目以前の受信時に検出された周波数誤差値を用いて受信周波数補正手段108により受信周波数を前記受信信号の中央周波数に合わせる。

(もっと読む)

自動周波数制御方法及びその装置

【目的】受信端の複雑度を減少させながらも受信性能が向上できる自動周波数制御方法及び前記方法を遂行する装置を提供する。

【構成】等化器301から出力される2進データ列をチャネル特性値と通信システムの送信側の変調器の伝達関数とのコンボリューション値を利用して再変調しそこから基準位相を得てこれを受信位相と比べ位相エラー値を算出する。位相エラー値は周波数エラー値に変換された後再びアナログ形の制御電圧に変換され前記電圧制御発振器に印加されるようにする。このような方法を遂行するために自動周波数制御装置は等化器301、チャネル特性推定部302、再変調器303、位相比較器304、周波数エラー推定部305及びディジタルアナログコンバーター306等を含んで構成される。

【効果】これにより、受信側の受信性能を向上させる利点を有し、ディジタルに具現するのが可能であって単一チップで構成できる。

(もっと読む)

映像中間周波回路

1 - 7 / 7

[ Back to top ]