国際特許分類[H03K17/62]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114) | 装置がバイポーラトランジスタであるもの (134) | いくつかの入力または出力端子をもつスイッチング装置,例.マルチプレクサ,分配器 (17)

国際特許分類[H03K17/62]に分類される特許

1 - 10 / 17

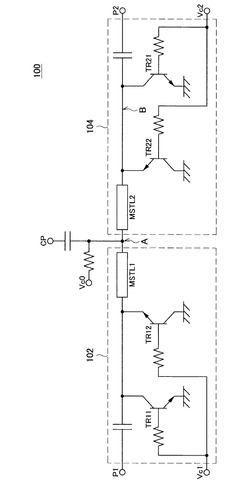

スイッチ

【課題】高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することが可能なスイッチを提供する。

【解決手段】高周波信号が入力される入力端子と、高周波信号が出力される第1出力端子との間に接続され、入力される高周波信号を第1出力端子から選択的に出力させる第1スイッチング部と、入力端子と、入力された高周波信号が出力される第2出力端子との間に接続され、入力端子に入力される高周波信号を第2出力端子から選択的に出力させる第2スイッチング部とを備え、第1スイッチング部、第2スイッチング部それぞれは、信号線上に設けられるインピーダンス変成器と、エミッタが接地され、コレクタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタと、コレクタが接地され、エミッタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタとを備えるスイッチが提供される。

(もっと読む)

RFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器

【課題】スイッチング素子の個数を減らし、スイッチング素子を送受信時共有して、RFアンテナスイッチのサイズを減らすと共に、小型化及びワンチップ化にさらに応じるRFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器を提供する。

【解決手段】アンテナ1と、少なくとも一つの送信段2及び少なくとも一つの受信段3を備える複数の入出力段と、少なくとも一つの送信段2とアンテナ1側の共通ノード4、5との間の送信経路上に配置され、制御信号によって信号を伝達する少なくとも一つの送信スイッチブロック10と、受信段3と共通ノード4、5との間の受信経路上に配置され、制御信号によって伝達する少なくとも一つの受信スイッチブロック30、30a、30bと、スイッチング素子を共有して各々の送信及び受信動作と同期してオン動作する共用送受信スイッチブロック50とを含む。

(もっと読む)

高速多重化回路

【課題】高速動作時の出力波形品質を改善する。

【解決手段】高速多重化回路は、データ信号列(D1P,D1N),(D2P,D2N)毎に設けられ、入力されたデータ信号列を共通に接続された信号出力端子に選択的に出力する第1のトランジスタQ1P,Q1N,Q2P,Q2Nと、トランジスタQ1P,Q1Nから構成される差動対またはトランジスタQ2P,Q2Nから構成される差動対のいずれか一方をクロック信号CK1,CK2に応じてオンにする第2のトランジスタQ3,Q4と、トランジスタQ1P,Q1N,Q2P,Q2N,Q3,Q4にコレクタ電流を流す電流源となる第3のトランジスタQ6,Q7と、第3のトランジスタQ6,Q7のコレクタとエミッタ側の電源電圧VEEとの間に挿入されたコンデンサC1とを備える。

(もっと読む)

FETスイッチ

【課題】1入力多出力スイッチおよび多入力1出力スイッチとして、広帯域化ならびに小型化・低コスト化が可能なFETスイッチを提供する。

【解決手段】第1の端子とn個(n:正整数、図1の場合n=4)の第2の端子との間の切替制御を行うSPnTスイッチとして、第1の端子と接続した配線210を分岐点Aにてn分岐した配線211〜214に、それぞれ、n個のFET41〜44のソースまたはドレインを接続し、n個のFET41〜44のドレインまたはソースには、それぞれ、配線221〜224を介して第2の端子を接続するとともに、少なくとも、配線211〜214を、それぞれ、直線で形成し、かつ、それぞれの長さを互いに等しくする。

(もっと読む)

昇圧回路に用いられる電流制御回路

【課題】昇圧回路から供給される電流を制御するエンハンスメント型及びディプレッション型FETで構成される回路で、昇圧回路からの不要な電流供給を無くし、電圧昇圧効率を高める。

【解決手段】入力端子INにLowレベルの電圧が入力された場合、トランジスタEF1は遮断状態に、第1のスイッチ回路SW1は導通状態に、第2のスイッチ回路SW2は遮断状態になる。よって、負荷Rには、昇圧回路CPから出力される昇圧電圧が印加される。入力端子INにHighレベルの電圧が入力された場合、トランジスタEF1は導通状態に、第1のスイッチ回路SW1は遮断状態に、第2のスイッチ回路SW2は導通状態になる。よって、負荷Rには、外部電源供給端子VDDと同等の電圧が印加される。従って、昇圧電圧が不要な時にトランジスタEF1で常に電流が流れていても、昇圧回路CPからの供給電流に影響を及ぼさない。

(もっと読む)

容量性負荷駆動回路

【課題】本発明は、印加電圧の変化幅に応じた放電制御を行って容量性負荷に印加する多値の電圧を高速に可変制御できる容量性負荷駆動回路を提供することを目的とする。

【解決手段】容量性負荷に多値の電圧を印加して駆動する容量性負荷駆動回路において、電圧制御信号を生成して出力する電圧制御信号生成手段と、前記電圧制御信号を電圧増幅する電圧増幅手段と、前記電圧増幅手段の出力を電流増幅して前記容量性負荷の充電を行う電流増幅手段と、前記電圧制御信号の立ち下がりの幅が所定値を超えるとき所定パルス幅の立ち下がりパルスを発生する立ち下がり制御信号発生手段と、前記立ち下がりパルスの供給により前記容量性負荷の放電を行うスイッチ手段とを有する。

(もっと読む)

差動論理回路

【課題】動作電流を電源電圧に依存しないようにすると共にバイアス配線をなくして回路の物理的配線を容易にすることが可能な差動論理回路を実現する。

【解決手段】定電流で動作する差動論理回路において、出力電圧が一定の供給用電源及びバイアス用電源を発生する電源電圧発生部と、供給用電源及びバイアス用電源が供給され、差動入力信号が入力されると共に第1の差動出力信号を出力する信号レベルレギュレータ部と、供給用電源が供給されると共に第1の差動出力信号が入力され、動作電流が第1の差動出力信号若しくは出力信号の電圧レベルにより決定される定電流動作ロジック部と

を備える。

(もっと読む)

マルチプレクサ回路

【課題】 動作に必要な電源電圧を低くすることが可能なマルチプレクサ回路を実現する。

【解決手段】 複数の入力信号のうち一つの入力信号を選択して出力するマルチプレクサ回路において、第1及び第2の差動入力信号がそれぞれ印加され回路内にコモンモード電流が流れるとコモンモード電流が流れなかった場合のローレベルの出力電圧よりもハイレベルの出力電圧が小さくなる第1及び第2のバッファ回路と、差動選択信号により第1のバッファ回路に流れるコモンモード電流を制御する第1のコモンモード制御回路と、差動選択信号により第2のバッファ回路に流れるコモンモード電流を制御する第2のコモンモード制御回路と、第1のバッファ回路の出力電圧若しくは第2のバッファ回路の出力電圧の内、出力電圧の大きいバッファ回路の出力電圧を差動出力信号として出力する出力段回路とを設ける。

(もっと読む)

切替制御回路及び半導体集積回路装置

【課題】入力信号線の数が少なく且つ極力低い電源電圧で動作可能な切替制御回路、及びその切替制御回路を有して構成される半導体集積回路装置を提供する。

【解決手段】ソレノイド駆動ICに、主回路トランジスタ、主回路トランジスタのオンオフを制御する制御回路、及びソレノイドユニットの駆動方式に基づいて制御回路の制御方式を切り替えるための切替制御回路18などを形成する。切替制御回路18は、電源ライン30a及びグランド30bから+5Vの電源電圧Vccの供給を受けて動作し、入力ノードNaに入力される切替指令信号Sinの状態に応じて、出力ノードNb、Ncから切替状態信号So1、So2を出力する。

(もっと読む)

スイッチ回路装置

【課題】 HBTでスイッチング素子を構成したスイッチ回路装置では、大きなベース電流を必要とするため、各RF端子を高周波信号の分離素子30を介してDCバイアスポイントに接続すると、HBTに十分なバイアスを印加できず、HBTを十分動作させることができない。

【解決手段】 複数の単位HBTを並列接続して集合素子を構成し、1つの集合素子の共通エミッタおよび共通コレクタ毎に1つの分離素子を介して1つのバイアスポイントに接続し、バイアス電位を印加する。単位HBTをグループ分けすることによりベース電流を分散できるため、分離素子に流れるベース電流が小さくなり電圧ドロップが小さくなる。従って、単位HBTに十分なバイアスが印加でき、動作させることができる。

(もっと読む)

1 - 10 / 17

[ Back to top ]