国際特許分類[H03K19/18]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 電流磁気効果装置を用いるもの,例.ホール効果装置 (17)

国際特許分類[H03K19/18]に分類される特許

1 - 10 / 17

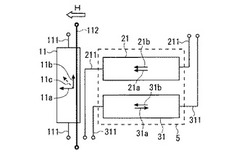

磁気レベルシフタ

【課題】多チャンネル化しても形成面積の増大を抑えることができる磁気レベルシフタを提供する。

【解決手段】レベルシフタは、入力信号が印加される磁界発生用配線112と、磁界発生用配線112が発生した磁界に対応した値をとる検出信号を出力する検出用磁気抵抗効果素子11と、一定の値をとる参照信号を出力する参照用磁気抵抗効果素子21,31を備える。当該レベルシフタは、検出信号と参照電圧の差に基づいて出力信号を生成する。

(もっと読む)

スピントランジスタ及び集積回路

【課題】消費電力を抑制し、占有面積の増大を抑制したスピントランジスタ及び集積回路を提供する。

【解決手段】実施形態のスピントランジスタは、第1の入力端子を有し、第1の入力端子から入力される第1の信号により第1の磁化方向に偏極する第1の磁性体領域と、第2の入力端子を有し、第2の入力端子から入力される第1の信号とは異なる第2の信号により第1の磁化方向とは逆向きの第2の磁化方向に偏極する第2の磁性体領域と、第3の入力端子と、第1の出力端子とを有し、第3の入力端子から入力される第3の信号により第1の磁化方向に偏極して第1の磁性体領域から供給される第1の信号を第1の出力端子から出力し、第3の入力端子から入力される第3の信号とは異なる第4の信号により第2の磁化方向に偏極して第2の磁性体領域から供給される第2の信号を第1の出力端子から出力する第3の磁性体領域と、を備える。

(もっと読む)

スピントルク磁気集積回路、及びそのためのデバイス

スピントルク磁気集積回路及びそのためのデバイスが開示される。スピントルク磁気集積回路は、基板上に配設された第1のフリー強磁性層を含む。非磁性層が第1のフリー強磁性層上に配設される。複数の書込ピラー及び複数の読出ピラーが含められ、各ピラーは、前記非磁性層上に配設され、且つ固定強磁性層を有する。  (もっと読む)

(もっと読む)

スピントロニクス装置及び論理演算素子

【課題】 電流−スピン流変換効率が高く、高強度のスピン流が得られるスピントロニクス装置を提供する。

【解決手段】 対向する第1端面及び第2端面を有し、正孔と電子とが同程度のキャリア密度と移動度を有し、ホール係数がゼロである非磁性の両極性伝導金属からなるスピン流生成領域30と、第1端面に設けられ、スピン偏極された正孔をスピン流生成領域30に注入する強磁性体からなる第1主電極20と、第2端面に設けられ、電子をスピン流生成領域30に注入する第2主電極40とを備える。ローレンツ力により、正孔と電子とを同一方向に輸送されるようにして、正孔と電子の電荷を互いに相殺してスピン流を得る。

(もっと読む)

電子回路

【課題】メモリ機能を有する電子回路またはメモリ素子と集積化可能な電子回路を提供すること。

【解決手段】本発明は、半導体からなるチャネルと、前記チャネルにスピン偏極した電子を注入し強磁性体を含むソース20a、20bと、前記チャネルから前記スピン偏極した電子を受け強磁性体を含むドレイン22a、22bと、前記チャネルの電界を共通に変化させるゲート24a、24bと、を各々備える複数のトランジスタ30a、30bを具備し、前記複数のトランジスタの各々チャネルにおける電子の走行方向は、スピン軌道相互作用に起因する有効磁場に交差する方向であり、かつ前記ゲートに共通に印加されるゲート電圧により前記複数のトランジスタの各チャネルにおける電子に加わる有効磁場の大きさが相対的に変化する方向である電子回路である。

(もっと読む)

論理回路

【課題】 回路面積をさらに小型化しつつ、付加機能として動的再構成性を持たせることができる再構成可能な論理回路を提供する。

【解決手段】 本発明の論理回路は、配線選択部1、配線選択部1にて選択された配線が接続された入力ノード71、72のうちの1つの入力ノードに入力された信号、及びその他の入力ノードに入力された信号を論理演算する論理演算部2、及び論理演算部2に接続され、OR、ANDとNOR、NAND、NOTとを切り替える切替部3を有する。

(もっと読む)

プログラマブル論理回路

【課題】記憶素子を微細化しても書き込みおよび保持特性に与える影響を可及的に抑制し、かつソフトエラーが生じるのを抑制することを可能にする。

【解決手段】複数の入力信号を受ける入力部100と、第1のトランジスタを含む抵抗変化型のプログラム可能な第1の記憶回路と、第2のトランジスタを含む抵抗変化型のプログラム可能な第2の記憶回路とが並列に接続された単位プログラマブルセルが複数個、マトリクス状に配置されたプログラマブルセルアレイであって、同一行にある単位プログラマブルセルの第1のトランジスタのそれぞれのゲートが複数の入力信号から一つの選択された入力信号を受けるとともに前記第2のトランジスタのそれぞれのゲートが選択された入力信号の反転信号を受け、同一列の単位プログラマブルセルのそれぞれの第1および第2の記憶回路の出力端子が共通の出力線に接続されているプログラマブルセルアレイ200と、を備えている。

(もっと読む)

磁気メモリの試験方法および試験装置

【課題】非常に低い確率で起こる“書けない不良”の不良ビットを、可及的に短い試験時間内で検出することを可能にする。

【解決手段】電流を流して抵抗を変化させることにより書き込みが可能な磁気抵抗素子を有するメモリセルがマトリクス状に配列されたメモリセルアレイを備えた磁気メモリにおいて、使用時の書き込みパルスの高さ以下の高さを有しかつ当該の書き込みパルスの幅よりも狭い幅を有する書き込みパルスを用いて前記メモリセルに試験データの書き込みを行う書き込みステップを備えている。

(もっと読む)

磁気論理素子

【課題】ピントルク磁化反転過程によるメモリセルへの書き込み、読み出し動作と同様にして、論理素子の演算を行い、メモリ、論理素子いずれの動作速度もほぼ等しい装置を提供する。

【解決手段】第1磁化固定層、第1絶縁層、磁化自由層、第2絶縁層、及び第2磁化固定層を積層してなる二重トンネル障壁素子を複数組み合わせて構成されたインバータ素子、NAND素子及びNOR素子によって構成した論理回路11と、磁化固定層と絶縁層と磁化自由層を積層し電流誘起磁化反転機構により動作する磁気メモリ素子を複数有するメモリ17とを同一基板上に混載し、同一の制御回路12から共通のクロックを取る。

(もっと読む)

再構築可能な磁気論理回路配列体、および再構築可能な磁気論理回路配列体の製造方法および動作方法

本発明は、少なくともそれぞれ2つの磁性層から成る少なくとも2つの磁気抵抗素子と、少なくとも2つの信号端子に対する少なくとも1つの導体とを備えた再構築可能な磁気論理回路配列体に関し、該磁性層はそれぞれ中間層によって相互に分離されており、該磁性層のうち1つは基準層として、外部磁界に影響されても磁化を実質的に変化せず、他方の磁性層は自由層として、外部磁界に影響されると磁化を検出可能に変化し、該導体が通電されている状態では該導体によって、該磁気抵抗素子に作用して該自由層の磁化を切り換える第1の磁界が生成され、当該磁気論理回路配列体はさらに、該磁気抵抗素子に影響する第2の可変の磁界を必要に応じて生成するための第2磁界生成装置も備えている。このような回路配列体では、前記のような2つの磁気抵抗素子が相互に隣接して配置され、前記2つの基準層の磁化は、予め設定された一軸異方性によって相互に逆方向に配向され、前記第1の磁界および前記第2の磁界が前記磁気抵抗素子に作用して前記自由層の磁化の配向が変化し、ひいては該磁気抵抗素子の抵抗が変化することによって論理回路配列体においてすべての基本的な論理関数の切換動作が行われるように該磁気抵抗素子は相互に接続されており、とりわけAND関数、OR関数、NAND関数、NOR関数、XOR関数またはXNOR関数の切換動作が行われるように該磁気抵抗素子は相互に接続されている構成によって発展される。  (もっと読む)

(もっと読む)

1 - 10 / 17

[ Back to top ]