国際特許分類[H03K5/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | パルスの整形 (700) | 立上りまたは立下りの峻度の増大によるもの (76)

国際特許分類[H03K5/12]に分類される特許

1 - 10 / 76

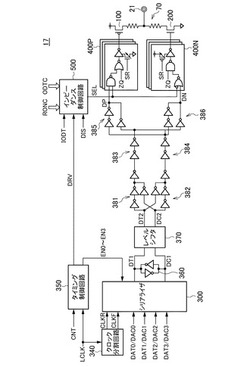

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

クロック出力回路

【課題】クロック出力回路1にて電流消費を抑えつつ、周波数が安定したクロックを出力する。

【解決手段】 発振回路10から出力される発振信号を論理否定するNOTゲート21A、22Aと、NOTゲート21Aの出力信号を論理否定するNOTゲート23と、NOTゲート22A、23の出力信号を入力信号とするRSフリップフロップ回路24とを備え、NOTゲート21Aの第1の閾値Th1はNOTゲート22Aの第2の閾値Th2よりも大きく、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなる。発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24が源クロックの出力を待機し、周波数が低くなるとRSフリップフロップ回路24が源クロックを出力する。

(もっと読む)

半導体装置

【課題】出力クロック信号を生成して出力するまでに要する時間を短縮させる。

【解決手段】半導体装置は、第1のクロック信号のライズエッジ及び第2のクロック信号のライズエッジを合成して第1及び第2のクロック信号のライズエッジの間にライズエッジを有する第3のクロック信号を生成する第1の位相合成回路と、第1のクロック信号のフォールエッジ及び第2のクロック信号のフォールエッジを合成して第1及び第2のクロック信号のフォールエッジの間にフォールエッジを有する第4のクロック信号を生成する第2の位相合成回路と、第3のクロック信号のライズエッジを受けてライズ/フォールエッジの内の一方の位相を、第4のクロック信号のフォールエッジを受けてライズ/フォールエッジの内の他方の位相を其々調整した出力クロック信号を出力する第3の位相合成回路と、を備える。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

半導体装置

【課題】ドライブ能力およびスルーレートを調節可能な出力ドライバを備え、従来よりも微細化することができる半導体装置を提供する。

【解決手段】半導体装置は、コア回路から転送されるデジタルデータを出力するために複数のサブドライバを含む出力ドライバODと、サブドライバを選択するセレクタとを備える。各サブドライバは、デジタルデータに従って出力データを立ち上げまたは立ち下げるために、第1の電源PS1と出力配線WOUTとの間に接続された出力トランジスタTP30と、出力トランジスタTP30のゲートと第2の電源VSSとの間に直列に接続されたスイッチングトランジスタTN33およびスルーレート調整トランジスタTN34とを備える。各スルーレート調整トランジスタTN34は、出力データの立ち上がりまたは立ち下がりのスルーレートを決定するために調整されたゲート電位をセレクタによって選択的に与えられる。

(もっと読む)

負荷駆動回路

【課題】ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能な負荷駆動回路を提供する。

【解決手段】電源3と負荷1との間に接続されたハイサイドスイッチとしてパワーMOSFET2を用いた負荷駆動回路10であって、パワーMOSFET のゲート電圧Vgと電源3の電源電圧Vpとを比較する比較回路11と、パワーMOSFET2のターンオフ動作においてパワーMOSFET2のゲート端子から電荷を放電させる遮断回路12とを具備し、遮断回路12によってパワーMOSFET2のゲート端子から電荷を放電させる放電速度は、ゲート電圧Vgが電源電圧Vpより高い場合の放電速度よりも、ゲート電圧Vgが電源電圧Vpより低い場合の放電速度が遅くなるように設定されている。

(もっと読む)

電圧出力回路

【課題】スイッチングノイズの少ない電圧出力回路を提供する。

【解決手段】電圧出力回路10では、出力トランジスタ11は、入力電圧Vinが印加される第1端子16と負荷RLが接続される第2端子17の間に接続され、ゲート電極が第1ノードN1に接続される。第1プルアップ回路12は、制御信号VcがLowのときに、第1ノード電圧Vn1を引き上げる。プルダウン回路13は、制御信号VcがHighのときに導通して第1ノード電圧Vn1を引き下げる。ゲート電圧監視回路14は、第1端子16と第1ノードN1の間に接続され、差電圧ΔV=Vin−Vn1が基準電圧Vrefより大きいときに導通して第2ノード電圧Vn2をHighにする。第2プルアップ回路15は、第1端子16と第1ノードN1の間に接続され、制御信号VcがLowで且つ第2ノード電圧Vn2がHighのときに導通して第1ノード電圧Vn1を引き上げる。

(もっと読む)

スキュー調整回路

【課題】

LSIの動作状態などに適合したスキューを複数の信号に与えることができるスキュー調整回路を提供する。

【解決手段】

第1及び第2の信号をそれぞれ伝播する第1及び第2の信号線と,第1及び第2の信号線を伝播する第1及び第2の信号がそれぞれ入力される第1及び第2のバッファ回路とを有する集積回路に設けられるスキュー調整回路であって,第1及び第2のバッファ回路の前段にそれぞれ設けられた第1及び第2の遅延回路と,第1及び第2の信号の間のスキューを測定するスキュー測定回路と,スキュー測定回路が測定した測定スキューに基づいて前記第1,第2の遅延回路の遅延量を決定し,当該決定した遅延量を前記第1,第2の遅延回路に設定する遅延調整回路とを有する。

(もっと読む)

半導体装置

【課題】終端抵抗のオンオフの切り替え時に外部端子にインピーダンスの急激な変化が生じることを低減する。

【解決手段】外部端子(図2のDQに相当)と、外部端子に接続され、出力信号を外部端子に出力可能とする出力回路(図2の21に相当)と、外部端子に終端抵抗をオンオフ可能に接続する終端回路(図2の22に相当)と、終端抵抗がオフ状態又はオン状態のいずれか一方の状態から他方の状態に変化するまでの時間を、データ出力時に出力信号が一方の論理レベルから他方の論理レベルへ変化するまでの時間以上となるように制御する第1のスルーレート制御回路(図2の23aに相当)と、を備える。

(もっと読む)

1 - 10 / 76

[ Back to top ]