国際特許分類[H03M1/10]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 符号化,復号化または符号変換一般 (10,763) | アナログ/デジタル変換;デジタル/アナログ変換 (2,647) | 較正または試験 (431)

国際特許分類[H03M1/10]に分類される特許

1 - 10 / 431

アナログデジタル変換装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

DACの直線歪補正回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

AD変換回路及びその補正方法

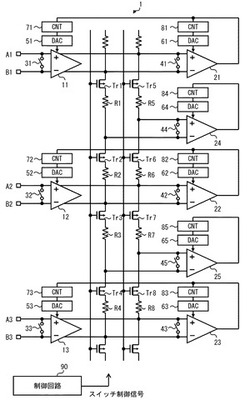

【課題】精度の高いAD変換を行うことがが可能なAD変換回路を提供すること。

【解決手段】本発明にかかるAD変換回路は、プリアンプ11,12と、コンパレータ21,22,24と、スイッチ31,41と、トランジスタTr1,Tr5と、スイッチ41をオンした場合におけるコンパレータ21の比較結果に基づいてコンパレータ21のオフセット電圧を補正する第1補正部と、スイッチ31をオンし、スイッチ41及びトランジスタTr1,Tr5をそれぞれオフした場合におけるコンパレータ21の比較結果に基づいてプリアンプ11のオフセット電圧を補正する第2補正部と、を備える。

(もっと読む)

二次電池の状態検知装置、二次電池の状態検知装置のための故障診断方法

【課題】故障診断用の電圧が変動した場合でも、精度良くADコンバータの故障診断を実施する二次電池の状態検知装置を提供する。

【解決手段】二次電池の状態検知のために検出されたアナログ値をデジタル値に変換する複数のADコンバータ(18−20)を備えた二次電池の状態検知装置において、前記複数のADコンバータの故障診断時に、故障診断用電圧を同時に前記複数のADコンバータへ入力するための故障診断用電源(15)と、前記複数のADコンバータの出力値を相互に比較して故障の判定を行う演算部(16)と、を備えた。

(もっと読む)

半導体装置

【課題】受信特性に悪影響を及ぼすことなく、受信動作中にバックグランドキャリブレーションを実施可能とする半導体装置を提供する。

【解決手段】受信動作中に、利得や受信チャンネルの切り替えに伴って無効な受信信号が発生するタイミングを検出して、このタイミングに合わせてバックグランドキャリブレーションを行う。このとき、受信信号はもともと無効なのでキャリブレーションに伴うさらなる受信精度の悪化は表面化しない。また、バックグランドキャリブレーションを一定の周期で行う際に発生する不要信号成分も、バックグランドキャリブレーションをランダムなタイミングで行えば発生しない。

(もっと読む)

デジタル受信機及びそれを用いた光通信システム

【課題】受信信号の品質に応じて、AD変換器の識別レベルを適切に調整することにより、その実効的な分解能を向上させ、もって、高分解能と高速化の要求に応え得るデジタル受信機を提供する。

【解決手段】デジタル受信機は、識別レベル制御信号に応じて識別レベルを設定し、設定された識別レベルに基づいて入力アナログ信号をデジタル信号に変換するAD変換器102と、設定値に基づき識別レベル制御信号を生成し、AD変換器へ出力する識別レベル調整回路104と、設定値に基づきAD変換器の伝達関数に関する情報である伝達関数補正制御信号を生成する信号品質モニタ部108と、伝達関数補正制御信号に基づいて、AD変換器の伝達関数と初期伝達関数とのずれを相殺するようにデジタル信号を信号処理する伝達関数補正回路106とを備える。

(もっと読む)

時間誤差推定装置、誤差補正装置およびA/D変換器

【課題】時間インターリーブ方式のA/D変換を行う際のA/D変換部のサンプリング時間誤差を、簡易な構成で精度よく推定できるようにする。

【解決手段】複数のA/D変換部のそれぞれでタイミングをずらしてA/D変換を行って得た複数のデジタル出力信号を複数の出力端子から出力する時間インターリーブA/D変換器における時間誤差推定装置は、前記複数のA/D変換部のサンプリング時間誤差を推定するものであり、前記複数のデジタル出力信号同士の類似度を表す相関値を求める相関器と、前記複数のA/D変換部の出力信号の微分値により前記相関値の重みを調整した結果に基づいて、前記複数のA/D変換部のサンプリング時間誤差を推定する重み加算器と、を備える。

(もっと読む)

A/D変換器および固体撮像装置

【課題】A/D変換器の比較器のオフセット電圧を簡単な構成で補正するための技術を提供する。

【解決手段】アナログ信号を入力するための入力端子INと、時間的に変化する参照信号を生成する信号源に接続される参照信号供給線と、非反転入力端子、反転入力端子及び出力端子を有し、非反転入力端子に供給された電圧と反転入力端子に供給された電圧との比較結果に応じた出力信号Voutを出力端子から出力する比較器CMPと、比較器の反転入力端子に接続された補正用キャパシタCoffと、入力端子に入力されたアナログ信号に対応するデジタルデータを出力する出力回路330とを備え、入力端子に入力された第2アナログ信号を比較器の非反転入力端子に供給しつつ、参照信号を用いて、比較器の非反転入力端子に供給されている第2アナログ信号又は補正用キャパシタに保持されている合計電圧を変化させる。

(もっと読む)

アナログデジタル変換回路、撮像装置、アナログデジタル変換回路の検査方法

【課題】 カウンタが複数のメモリに共通してカウント信号を供給する列ADCにおいて、カウンタからメモリへカウント信号を伝送する信号経路の不良によって生じる、メモリに供給されるカウント信号の遅延を好適に検出することを目的とする。

【解決手段】 カウント信号の信号値が変化したタイミングに応じて、カウント信号をメモリに保持させるラッチ信号をメモリに供給するテストラッチ信号供給部を有するアナログデジタル変換回路である。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

1 - 10 / 431

[ Back to top ]