国際特許分類[H03M13/01]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 符号化,復号化または符号変換一般 (10,763) | 誤りの検出または誤りの訂正のための符号化,復号化または符号変換;符号理論の基本的仮定;符号化の限界式;誤り確率の評価方法;通信路モデル;符号のシミュレーションまたは試験 (2,253) | 符号理論の基本的仮定;符号化の限界式;誤り確率の評価方法;通信路モデル;符号のシミュレーションまたは試験 (26)

国際特許分類[H03M13/01]に分類される特許

1 - 10 / 26

RAID装置及びガロア体の積演算処理方法

【課題】ガロア体を用いてパリテイデータを生成する際に、高速にガロア体の積演算を実行する。

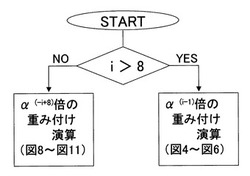

【解決手段】n台のデータストレージユニット(10−1〜10−16)の内、 (n−1)/2より大きな最小の整数をsとして、i=1〜s+1番目のデータストレージユニットのデータのガロア体の元として、α^(i−1)を、i=s+2〜n番目のデータストレージユニットのデータのガロア体の元を、α^(−i+s+1)を、重み付けとして、積演算を実行する。

(もっと読む)

量子誤り推定装置、量子誤り推定方法、そのプログラム、量子誤り訂正装置、量子誤り訂正方法

【課題】Steaneコードの量子誤り訂正方式において2個以上の物理キュービットにエラーが生じている場合にエラーの推定を行う技術を提供する。

【解決手段】7個の物理キュービットで構成される論理キュービットに対する6種類のユニタリー作用による観測の2種類の観測結果に古典ビット0と1を対応させて得られる6ビットについて、前半3ビットjと後半3ビットkがj≠kであり、且つ、jおよびkが各物理キュービットにエラーが無い場合の観測結果に対応する古典ビットのビット列ではない場合に、各物理キュービットのエラー発生確率をp1,…,p7とし、jとkに基づき、エラー発生確率pj×pk,pj×pj(+)k,pk×pj(+)kを計算し、pj×pk,pj×pj(+)k,pk×pj(+)kの大きさを比較し、最大のものを判定する。

(もっと読む)

パリティ機能付きハードディスク装置

【課題】簡易な手法にてデータの信頼性を向上させることが可能なパリティ機能付きハードディスク装置を提供する。

【解決手段】コントローラ11は、データを記録する場合、所定のブロック毎に、データをハードディスク13に記録し、所定のエラー訂正方式によってブロック内のデータからパリティを計算し、パリティをフラッシュメモリ14に記録する。また、データを再生する場合、ハードディスク13からデータを読み出し、所定のブロック内で読み出しエラーを判定すると、フラッシュメモリ14からそのブロックのパリティを読み出し、所定のエラー訂正方式によってデータエラーを復元する。所定のブロック長のサイズ及び所定のエラー訂正方式は、ハードディスク13のセクタに対する記録及び再生処理の可否を測定し、そのエラー率及びエラー分布に基づいて、予め設定される。

(もっと読む)

復調回路および復調方法

【課題】回路規模および消費電力を低減したOFDMA復調回路の実現。

【解決手段】シンボル方向とサブキャリア方向で定義されるフレーム内に複数のバースト領域が定義される復調回路であって、受信信号を復調した受信データをシンボル単位で記憶するシンボルメモリ31と、シンボルメモリに記憶された受信データをシンボル単位で伝送路推定・補償処理する伝送路推定・補償回路26と、伝送路推定・補償回路の出力を記憶し、誤り訂正処理におけるブロック単位で、出力するバッファ32と、バッファから出力された伝送路推定・補償処理済み受信データに対してブロック単位で誤り訂正処理を行う誤り訂正回路27と、を備える。

(もっと読む)

誤り検出機能を備える、符号化又は復号処理のための回路構成

【課題】符号化・復号回路の動作時のエラー検出を確実に行い、かつ回路規模と動作速度に対するペナルティを軽微なものとする回路構成を提供すること。

【解決手段】あるステージにおいて符号化処理が実行されている時、その1つ前段のステージでは、直前のサイクルにおける符号化処理の検証としての復号処理が並行して実行される。復号されたデータは、直前のサイクルにおいて符号化の対象となったデータと比較されて、一致しているかどうかが調べられる。その次のサイクルでは、当該ステージにおいて先に符号化されたデータが復号され、符号化される前のデータと一致しているかどうかが調べられる。並行して、先に符号化されたデータに対して次段のステージで符号化処理が進められ、前段のステージには新たなデータが入力されて符号化処理が行われる。

(もっと読む)

プログラム可能なプロセッサにおける随意選択的なガロア域計算の実行

ガロア域乗算のための方法は第1及び第2の指令の実行を含んでいる。第1の指令は、第1の変数のような第1の入力を受信し、第2の変数のような第2の入力を受信し、第1及び第2の入力を使用してGF(2m)により多項式乗算を行い、積を生成することを含んでいる。第2の指令は、第1の指令からの積である第3の入力を受信し、積において演算するための予め定められた生成多項式である第4の入力を受信し、積における予め定められた生成多項式の演算を限定するため予め定められた生成多項式の長さである第5の入力を受信し、長さにより限定された予め定められた生成多項式を介して除数に関して積の係数を計算することを含んでいる。ハードワイヤブロックも説明されている。 (もっと読む)

ランダムエラー発生装置、M系列発生回路及びその設計方法

【課題】光通信や電子通信における雑音等に起因するエラーに近似したランダムエラー信号を実現する。

【解決手段】ランダムエラー発生装置に組込まれたM系列発生回路を実現するための2元の拡大ガロア体(2m)における次数m(レジスタ数)を複数の原始多項式p(x)を実現できるように選択し、この複数の原始多項式p(x)のうちの項数が多い原始多項式p(x)を採用する。

さらに、各クロックに同期して、ガロア体乗算するデータを原始元α単体でなく、指定べき乗値(αk)としている。

(もっと読む)

演算処理装置

【課題】受信データのデータ長によらず高速に演算処理ができる演算処理装置を提供。

【解決手段】受信データ長30に基づいてパラレル演算回数およびシリアル演算回数が演算回数生成部32にて生成され、これら演算回数を制御するためにパラレルイネーブル信号20またはシリアルイネーブル信号16が演算イネーブル生成部40から入力制御部14に与えられると、パラレルイネーブル信号20の入力期間に受信データ12がパラレルにて演算処理部24に入力され、シリアルイネーブル信号16の入力期間に受信データ12がシリアルにて演算処理部24に入力され、演算処理部24ではそれぞれ入力データをパラレル演算処理およびシリアル演算処理をしてその処理結果を出力26に出力する。

(もっと読む)

エラー訂正処理装置の制御方法

【課題】訂正前データと訂正後データを記憶するメモリの規模を小さくでき、オーバーフローの発生を未然に防止することができるエラー訂正処理装置の制御方法を提供することにある。

【解決手段】訂正処理能力制御回路25は、負荷検出回路37と能力制御回路38を有している。負荷検出回路37はエラー訂正処理回路部24にかかる負荷を検出する。能力制御回路38は、その負荷検出回路37が検出した負荷が大きい場合に、エラー訂正処理回路部24の訂正処理速度を速くする。

(もっと読む)

半導体記憶装置

【課題】ECC回路を搭載した半導体記憶装置において、ユーザデータの入出力に際し、データの信頼性が高く、従来の装置とも互換性を備えかつユーザデータの記憶容量の高い半導体記憶装置を提供する。

【解決手段】ECC回路205に入力されるデータのビット数を、書き込みのため外部から入力されるデータのビット数よりも多くすることにより、メモリセルアレイ201に書き込まれるユーザデータに対するパリティビットの比率を低減させる。結果、従来装置に比べてメモリセルにおけるパリティビット用の記録領域の占める割合を低下させることで、集積密度が同一のメモリセルアレイにおいて、ユーザが利用可能な記憶容量を高くしている。

(もっと読む)

1 - 10 / 26

[ Back to top ]