株式会社東芝により出願された特許

1,901 - 1,910 / 54,554

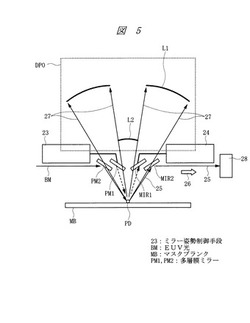

マスクブランクの欠陥検査方法およびマスクブランクの欠陥検査装置

【課題】互いに多層膜の周期長の異なる複数のマスクブランクに対しても、検出感度の高い検査を実現する。

【解決手段】マスクブランクMBに関する情報に基づいてマスクブランクMBの表面に照射するEUV光BMの入射角度を調整し、照明光学系を介して取り込まれたEUV光BMをマスクブランクMBの被検査領域に照射する。EUV光BMの入射角度は、ミラー姿勢制御手段23を用いて多層膜ミラーPM1,PM2の位置および角度を制御することにより調整する。

(もっと読む)

半導体記憶装置

【課題】データ保持特性に対する信頼性を回復させることができる半導体記憶装置を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体と、前記積層体を貫く半導体ピラーと、前記電極膜と前記半導体ピラーとの間に設けられた電荷蓄積層と、前記電荷蓄積層と前記半導体ピラーとの間に設けられたトンネル層と、前記積層体の積層方向に対して直交する一の方向において、前記半導体ピラー同士の間に設けられた前記電極膜を分離する分離溝と、前記分離溝の内部に設けられた加熱部と、を備えている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

露光方法及び露光用マスク

【課題】 マスク作製にかかるコストや時間の増大を極力抑えつつ、多層膜の位相欠陥等であってもウエハ上の共通欠陥を消失させることができ、パターン寸法精度の向上をはかる。

【解決手段】 反射型マスクを用いた露光方法であって、所望パターンが形成された第1の反射型マスクAを用いて、試料上にパターン露光を行う工程と、第1の反射型マスクAの欠陥13に相当する位置に反射膜のパターン15を形成した第2の反射型マスクBを用いて、試料上に補正露光を行う工程と、を含む。

(もっと読む)

固体撮像素子

【課題】色ずれの抑制を図ることができる固体撮像素子を提供することである。

【解決手段】実施形態に係る固体撮像素子は、複数の光電変換部が設けられた基板と、前記複数の光電変換部毎に設けられ、特定の波長帯域の光を選択的に透過させるカラーフィルタと、を備えている。そして、前記カラーフィルタは、屈折率の異なる層が積層された積層構造部と、複数の要素が前記特定の波長帯域および光の入射角度に応じて異なる周期で設けられた周期構造部と、を有する。

(もっと読む)

半導体記憶装置

【課題】十分な消去速度が得られる半導体記憶装置を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上にそれぞれ交互に積層された複数の電極層と複数の第1の絶縁層とを有する第1の積層体と、前記第1の積層体上に設けられ、選択ゲートとその上に設けられた第2の絶縁層とを有する第2の積層体と、前記第1の積層体を積層方向に貫通して形成された第1のホールの側壁に設けられたメモリ膜と、前記第1のホールと連通し、前記第2の積層体を積層方向に貫通して形成された第2のホールの側壁に設けられたゲート絶縁膜と、前記メモリ膜の内側および前記ゲート絶縁膜の内側に設けられたチャネルボディと、を備えている。そして、前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成され、前記チャネルボディの前記選択ゲートの上端近傍に位置する領域は、シリサイド化されている。

(もっと読む)

半導体装置およびその製造方法

【課題】チップ分割時の残留歪みが少ない半導体装置およびその製造方法を提供する。

【解決手段】半導体装置10の製造方法では、対向する第1の面11aと第2の11b面を有する半導体基板11の第1の面11aに、ダイシングライン14、15に沿って円柱状のトレンチ22を形成する。半導体基板11を熱処理し、円柱状のトレンチ22の回りの半導体基板材のマイグレーションにより、半導体基板11の内部に中空部16を形成する。中空部16が形成された半導体基板11の第1の面11aであって、ダイシングライン14、15で囲まれた矩形状領域に半導体素子12を形成する。半導体素子12が形成された半導体基板11を、第2の面11b側から所定の厚さになるまで除去する。中空部16を起点として、ダイシングライン14、15に沿って半導体素子12が形成された半導体基板11をチップ25に分割する。

(もっと読む)

インプリント用テンプレート及びインプリント方法

【課題】凹凸パターン内への光硬化性有機材料の充填速度が低下することを防止し、インプリント処理に要する時間の増加を抑制する。

【解決手段】本実施形態によれば、インプリント用テンプレート10は、1面に凹凸パターンを有するインプリント用テンプレートであって、光透過性を有する基材12と、基材12上に設けられ、複数の粒子14を含んだ第1層16と、第1層16上に設けられ、前記凹凸パターンが形成されており、光透過性及びガス透過性を有する第2層18と、を備える。粒子14は、所定波長の光を吸収して熱を放出する。

(もっと読む)

半導体基板の超臨界乾燥方法

【課題】半導体基板上の金属材料やポリシリコンのエッチングを抑制し、半導体デバイスの電気的特性の劣化を防止することができる半導体基板の超臨界乾燥方法を提供する。

【解決手段】半導体基板の超臨界乾燥方法は、半導体基板を洗浄・リンスした後に、表面が水溶性有機溶媒で濡れた半導体基板をチャンバ内に導入する工程と、前記チャンバを密閉し、前記水溶性有機溶媒を超臨界状態にする工程と、前記チャンバ内の圧力を下げ、超臨界状態の前記水溶性有機溶媒を気体に変化させて、前記水溶性有機溶媒を前記チャンバから排出する工程と、前記チャンバ内の圧力が大気圧まで下がるに伴い、前記チャンバ内へ不活性ガスを供給する工程と、前記半導体基板を冷却する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

1,901 - 1,910 / 54,554

[ Back to top ]