東芝メモリアドバンスドパッケージ株式会社により出願された特許

1 - 10 / 30

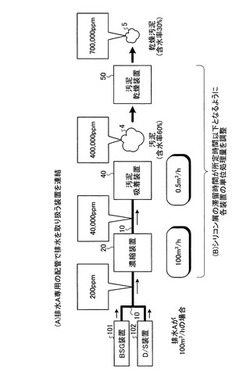

シリコン回収システムおよびシリコン回収方法

【課題】ピュアシリコンの含有率が高いシリコン汚泥を回収すること。

【解決手段】結晶シリコンの研磨および/または研削に伴う排水を流通させる樹脂製またはステンレス製の配管を用いることとしたうえで、流通される排水を貯留する貯留槽内の排水に浸漬した膜エレメントへシリコン汚泥を吸着させる汚泥吸着装置と、吸着されたシリコン汚泥を乾燥させることによって乾燥シリコン汚泥を得る汚泥乾燥装置とを配置し、シリコンが水と接した状態で留まる滞留時間が、かかる状態のシリコンにおける酸素濃度の時間変化率を示す酸化係数および回収されるシリコンにおける酸素濃度の目標値に基づいて算出される上限時間以下となるように、配管によって流通される単位時間あたりの排水の量および汚泥吸着装置によって処理される単位時間あたりの排水の量を決定するようにシリコン回収システムを構成する。

(もっと読む)

封止樹脂の難燃性評価方法および難燃性評価用試験体

【課題】電子機器に用いられる封止樹脂の難燃性の実使用に即した評価方法を提供する。

【解決手段】この封止樹脂の難燃性評価方法は、発熱体を内蔵する封止樹脂成形体である試験体に対して、通電により発熱体を発熱させて溶断させる工程と、発熱体の溶断後通電を継続して封止樹脂を発火させる工程と、発熱体の溶断から封止樹脂の発火までに印加された電圧および/または電流を測定する工程を備える。また、この試験体は、この難燃性評価方法に使用される試験体であり、電熱線と、この電熱線の両端に接続された該電熱線よりも電気抵抗の低い金属から成る通電用端子と、前記電熱線の外周に被覆された封止樹脂層を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 パッケージ側面部の口開きの発生及び内部への進行を抑制した半導体装置及びその製造方法を提供する。

【解決手段】 主面上に素子領域が形成された半導体基板1と、素子領域の所定の位置上に形成された層間絶縁膜及び配線層と、層間絶縁膜、配線層及び半導体基板の主面を覆い、素子領域を取り囲む開口部に充填された封止樹脂膜9とを備え、封止樹脂膜9と開口部内の封止樹脂膜からなる接合部11とを連続的に形成することにより、封止樹脂9の口開きの発生及びその内部への進行を抑制する。

(もっと読む)

高さを測定する方法及び高さ測定装置

【課題】ICのリードの浮きによる高さのような微小な高さを測定する際に測定装置の構成を簡易にし、繰り返し測定精度を高め、測定に要する時間を短くし、スループットを高められようにする。

【解決手段】リード先端部分の形状を矩形関数で表し、その形状関数と点応答関数のコンボリューション積分で表されるリード先端部分の像の強度分布のフーリエ変換を求める。そのフーリエ変換から、リード先端部分の画像における強度分布とリード先端の高さとの関係の式を求め、この式からリードの浮きによる高さを求める。この高さを求める解析演算を行う装置としては、既存の撮影手段と画像解析ソフトウェアとからなる2次元検査装置に高さを求める演算を行うための解析用ソフトウェアを追加モジュールとして付加したものとする。

(もっと読む)

バンプ構造、半導体装置およびその製造方法

【課題】半導体装置のバンプ構造において、フリップチップ接続時の超音波振動による応力に起因する半導体素子の電極部などの機械的損傷や劣化を防止する。

【解決手段】本発明のバンプ構造は、半導体素子の電極パッド上に形成されたスタッド形状を有する第1のバンプと、その上に積重ねて形成されたスタッド形状を有する第2のバンプと、第1のバンプの側周面を覆うように形成された有機樹脂層を備える。有機樹脂層は、第1のバンプの先端部と第2のバンプの底面との間に形成されたくびれ部の少なくとも一部を充填するように形成され、かつ第2のバンプの底面より上方へは延出しないように形成されている。半導体装置は、このようなバンプ構造を有する半導体素子と、電極端子を有する配線基板を備え、第2のバンプの先端部が配線基板の電極端子に接合されフリップチップ接続されている。

(もっと読む)

半導体装置

【課題】リジッドパッケージ基板の表面上に半田バンプを有する半導体チップをフェースダウンにより搭載して、前記半導体チップと前記リジッドパッケージ基板とをフリップチップ(FC)接続を介して機械的及び電気的に一体化した半導体装置において、前記リジッドパッケージ基板の反りを十分に低減する。

【解決手段】半導体チップと、前記半導体チップがフリップチップ接続により搭載されるリジッドパッケージ基板と、少なくとも前記半導体チップ及び前記リジッドパッケージ基板間に形成された空隙を埋設するように設けられた樹脂封止体とを具えた半導体チップにおいて、前記リジッドパッケージ基板を、前記樹脂封止体の端部から前記半導体チップの少なくとも端部を含んで延在する領域が弾性体を含むように構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来に比べて小型化を図ることができるとともに、従来に比べて設計上のフレキシビィリティーの向上を図ることのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、最下段に位置する下段半導体パッケージ10を具備している。下段半導体パッケージ10は、フレキシブルプリント基板11の上に設けられている。フレキシブルプリント基板11は、その一部が下段半導体パッケージ10の上部に位置した状態となるよう折り曲げられ。このフレキシブルプリント基板11の下段半導体パッケージ10の上部に位置した部分に、中段半導体パッケージ20が搭載されている。中段半導体パッケージ20のフレキシブルプリント基板21は、その一部が中段半導体パッケージ20の上部に位置した状態となるよう折り曲げられ。このフレキシブルプリント基板21の上に、上段半導体パッケージ30が搭載されている。

(もっと読む)

半導体装置の製造方法及びそのテスト装置

【課題】システムLSIにつきウェハ状態で一括してテスト可能な半導体装置の製造方法及びそのテスト装置を提供すること。

【解決手段】 表面から突出したボール状の外部接続端子17を複数有する半導体ウェハ1をステージ21上に戴置するステップS11と、前記ステージ21上に戴置された前記半導体ウェハ1に対してプローブカード22を近接させ、該プローブカード22に備えられた複数のプローブ端子28を前記外部接続端子17の各々に接触させるステップS12と、前記プローブ端子28を介して前記半導体ウェハ1に電圧を印加して、該半導体ウェハ1のテストを行うステップS13、S14とを具備し、前記外部接続端子17の全てに対して、個々の前記プローブ端子28が接触される。

(もっと読む)

半導体装置とその製造方法

【課題】例えばスタック型マルチチップパッケージを作製するにあって、より一層の薄型化を可能にした半導体装置を提供する。

【解決手段】半導体装置1は、同一表面に形成された素子搭載部4と接続部5とを有する回路基板2を具備する。回路基板2の素子搭載部5には、第1の半導体素子7がフェースアップ状態で搭載されている。第1の半導体素子7上には、スペーサ10を介して第2の半導体素子12がフェースダウン状態で積層されている。回路基板2の接続部5と第2の半導体素子の第2の電極部11とは対向配置されていると共に、第2の導電性ワイヤ15を介して電気的に接続されている。

(もっと読む)

開発管理装置、開発管理システム、コンピュータプログラム

【課題】製品開発者と部品開発者との開発作業の円滑な連携を可能にすること。

【解決手段】複数の部品から構成される製品の開発状況を管理する開発管理装置であって、製品開発に必要な製品情報および製品を構成可能な部品に関する部品情報を記憶する記憶部と、製品情報に基づいて、記憶部に記憶された部品情報から開発が完了した開発済部品情報を抽出してユーザに提供する既存部品抽出部と、製品情報に基づいて、記憶部に記憶された部品情報から開発途上にある仕掛部品情報を抽出してユーザに提供する仕掛部品抽出部と、ユーザが選択する開発済部品情報および仕掛部品情報を受け付け、製品情報と関連付けて記憶部に記憶させる製品情報管理部とを具備する。

(もっと読む)

1 - 10 / 30

[ Back to top ]