アーム・リミテッドにより出願された特許

81 - 90 / 134

ホストデータ処理装置内におけるデバイスエミュレーションのサポート

メモリ管理装置24を備えたデータ処理装置12が提供される。メモリ管理装置24は、メモリ停止をトリガする。メモリ停止が発生すると、前記メモリ停止を特徴付けるデータがフォールトステータスレジスタ28(メモリ停止レジスタ)に書き込まれる。前記メモリ停止を特徴付けるデータは、前記メモリ停止の発生源となったメモリアクセスと関連付けられたレジスタ番号を特定するデータを含む。このレジスタ特定データを用いて、前記メモリ停止に繋がるプログラム命令を読み出す必要無く、メモリアクセス命令のアクションをエミュレートする。これは、仮想データ処理装置2のための仮想化サポートを提供する際に、有用である。  (もっと読む)

(もっと読む)

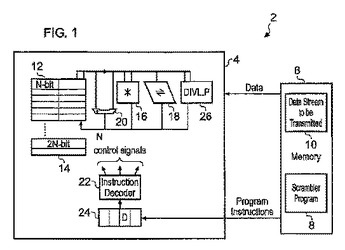

多項式データ処理演算

データ処理システム(2)は、多項式除算演算を実行するために処理回路構成(26)を制御する制御信号を生成する多項式除算命令DI−VL.PNに応答する命令復号器(22)を含んでいる。分母多項式は、多項式の最高次数項が、常に「1」の係数を有しているので、この係数は、分母値を格納するレジスタ内に格納される必要がないと見なして、レジスタ内に格納された分母値によって表わされる。従って、分母多項式は、分母値だけを格納するレジスタ内のビット空間で起こり得る次数より1つ高い次数を有することができる。多項式除算命令は、商の多項式及び剰余多項式をそれぞれ表わす商の値及び剰余値を戻す。  (もっと読む)

(もっと読む)

集積回路内のデバイス間のデータ転送

【課題】相互接続16を介して通信するため、多数のデバイス4,6,8,10,12,14を備えた集積回路2を提供する。

【解決手段】送信デバイス18は、その繰り返しデータワード自体の代わりに、繰り返しデータワードの表示の使用を示す、サイドバンド信号を含んでいる。次いで、受信デバイスは、表示の受信に応じて、データワードの繰り返しパターンを構成することができる。これによって、相互接続16によって消費される帯域幅を削減する。

(もっと読む)

診断コンテキストの構成および比較

【課題】一連のプログラム命令の実行の分析を容易にするための診断機構を提供するデータ処理システムを提供する。

【解決手段】データ処理システム1は、プロセッサコア2を有し、該プロセッサコアは、仮想マシン識別子によってそれぞれが識別された複数の仮想マシンのうちの1つとして機能するようにプログラム可能であり、各仮想マシンは、コンテキスト識別子によってそれぞれ識別された複数のコンテキストのうちの1つにおいて機能し、各コンテキストは、一連のプログラム命令を実行し、各プログラム命令は1つ以上の関連するメモリアドレスを有する。データ処理システムは、プロセッサコア上で診断動作を実行するための診断回路10を有する。診断制御回路12が提供され、該回路は、仮想マシン識別子、コンテキスト識別子、および1つ以上の関連するメモリアドレスのうちの少なくとも1つの現在値に応答して診断回路10をトリガして診断動作を実行する。

(もっと読む)

複数の命令セットの命令プリデコード

【課題】複数の命令セットの命令プリデコードを提供すること。

【解決手段】データ処理装置は、プリデコード命令を生成する機能を有すプリデコード回路10を備える。プリデコード命令は、命令キャッシュ20内に格納される。命令キャッシュ20からのプリデコード命令は、デコード回路45,50,46により読み出され、対応する処理動作を制御する制御信号を形成するために使用される。最初にフェッチされたプログラム命令は、複数の命令セットのうちのそれぞれ1つの命令セットに属すことができる。1つの命令セットからの命令は、プリデコード回路10により、複数の命令セットのうちの他の命令セットから取り出した対応する命令に共有される機能を表す共有フォーマットを有するプリデコード命令にプリデコードされる。このようにして、デコード回路の共有部分は、それらの異なる命令セット両方からの命令の共有機能に関して制御信号を生成できる。

(もっと読む)

データの順列演算を実行するための装置および方法

順列演算を実行するための順列回路を有する処理回路と、データを格納するための複数のレジスタを有するレジスタバンクと、プログラム命令に応答して処理回路を制御し、データ処理演算を実行する制御回路と、を含む処理データのための装置が提供される。制御回路は、制御生成命令に応答して、ビットマスクに基づいて制御信号を生成し、入力オペランドに対して順列演算を実行するための順列回路を構成するように構成される。ビットマスクは、第1の順序を有する第1のグループのデータ要素と第2の順序を有する第2のグループのデータ要素とを前記入力オペランド内で特定し、順列演算は、前記第1の順序と前記第2の順序とのうちの一方を保存するが、前記第1の順序と前記第2の順序とのうちの他方を変える。  (もっと読む)

(もっと読む)

複数の電力領域を有する集積回路内の出力I/O信号の維持

【課題】選択的にパワーアップまたはパワーダウンさせることができる電力領域PD0,PD1,PD2,PD3を集積回路に設ける。

【解決手段】電力領域内のコア回路10によって生成された信号12をバッファする働きをする出力回路8は、それぞれ出力電力供給電圧IOVddを有している。適応型電圧感知回路24は、コア回路10へのコア電力供給電圧が閾値レベルを下回ったことを感知するとともに、低電圧信号を生成する。出力信号保持が事前に選択され、関係する出力信号に対してアクティブにされた場合に、出力回路8は、出力状態(低電圧で駆動される出力信号、高電圧で駆動される出力信号、またはハイインピーダンス駆動状態における出力信号)を維持することによって、低電圧信号に応答する。保持モードは、保持が要求されているか否かを示すモードラッチ24内に格納された値とともにオンショットパルスによって事前に選択される。

(もっと読む)

ハードウエアアクセラレータ内のデータ値のクリーニングの制御

【課題】ハードウエアアクセラレータ12に接続されたプログラム可能な汎用プロセッサ10を具備しているデータ処理装置2を提供する。

【解決手段】メモリ14,6,8は、プロセッサ10及びハードウエアアクセラレータ12によって共有されている。メモリシステム監視回路16は、1又は複数の所定のオペレーションに応答して、メモリシステム14,6,8上のプロセッサ10によって実行される、ハードウエアアクセラレータ12にトリガを生成し、それによって、その処理オペレーションを停止し、かつ、メモリシステム14,6,8に、ハードウエアアクセラレータのレジスタ20内の一時的な変数として保持された、任意のデータ値をクリーンする。

(もっと読む)

算術演算のためにマグニチュード検出を実行するための装置および方法

処理回路と、1つまたは複数のレジスタと、制御回路とを備える装置および方法が提供される。この制御回路は、結合マグニチュード検出算術命令に応答して、少なくとも1つのデータエレメント上で算術演算を実行するように、さらに、マグニチュード検出演算を実行するように、処理回路を制御するように構成される。マグニチュード検出演算は、算術演算のマグニチュードの最上位ビットのポジションが、少なくとも1つのデータエレメントのデータエレメント幅を超えるかどうかにかかわらず、最上位ビットのポジションを表示するマグニチュード表示結果を計算する。  (もっと読む)

(もっと読む)

相互接続素子および装置の構成の生成

【課題】複数の装置4、6、8、10、12を接続する相互接続素子14を持つ集積回路2の構成を生成する方法を提供する。

【解決手段】相互接続素子に接続される装置を選択するステップと、ファイルまたはモデル(例えばIP-XACT)からその装置のインターフェースパラメータを読み出すステップと、読み出したパラメータに合わせるために、相互接続素子のインターフェース"if"のパラメータを選択するステップと、インターフェースの選択されたパラメータに合わせるために必要な、相互接続素子14自体の構成における設定を検出して設定を行うステップと、現状では、相互接続素子の構成に合わせるために必要な、相互接続素子に以前から接続されていた装置の構成における必要な変更を検出するステップとを用いる。この方法において、相互接続素子の構成は、間違いの可能性の減少およびこのような構成の速度の上昇によって、少なくとも半自動であり得る。

(もっと読む)

81 - 90 / 134

[ Back to top ]