アーム・リミテッドにより出願された特許

41 - 50 / 134

集積回路の電力管理

【課題】集積回路の一部分を低電力状態にすることができるだけでなく、そのような部分がこの低電力状態から出る時に、迅速に処理動作を再開できることが望ましい。これを支援するために、論理回路の状態変数は、低電力状態の間維持される必要がある。

【解決手段】集積回路2は、実質(virtual)電力線6、8に接続される論理回路4を含む。これらの実質電力線は、電力制御トランジスタ10、16を介して、電力供給源14に接続される。電力制御装置20は、導電状態にある多数の電力制御トランジスタ10、16を決定する、制御信号を生成し、したがって、中間電圧レベルを有するように実質電力線を制御する。中間電圧レベルを選択して、論理回路を保持モードで維持してもよく、この状態は論理回路4内で維持されるが、処理動作は行われない。機能モードが再入力されると、ヘッダーおよびフッタートランジスタ10、16のすべてが導電状態に切り替えられ得る。

(もっと読む)

乗累算演算を実行するための装置および方法

【課題】乗累算演算を実行するデータ処理装置及び方法を提供する。

【解決手段】該データ処理装置は、制御信号に応答して、入力データ要素において、データ処理演算を実行するデータ処理回路を含む。命令デコーダ回路は、入力オペランドとして、第1入力データ要素、第2入力データ要素及び述語値を指定する述語化された乗累算命令に応答して、データ処理回路を制御するように制御信号を生成し、第1入力データ要素および前記第2入力データ要素を乗算し、乗算データ要素を生成し、該述語値が第1の値を有する場合、該乗算データ要素を初期累算データ要素に加算して結果累算データ要素を生成し、該述語値が第2の値を有する場合、該初期累算データ要素から該乗算データ要素を減算して、該結果累算データ要素を生成することで、乗累算演算を実行する。本発明は、パフォーマンス、エネルギー消費及びコード密度を改善する。

(もっと読む)

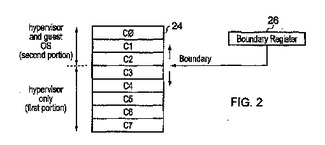

データ処理システム内のハードウェア資源管理

性能モニタ(12)およびコンテキストポインタ(18)等の複数のハードウェア資源を伴う、プロセッサ(6)を提供する。境界指示回路(14、20)は、プログラム可能であり、ハードウェア資源を第1の部分と第2の部分とに分割する境界位置を指示する、境界値を記憶する。資源制御回路(16、22)は、プログラム実行回路(8)が第1のプログラムを実行しているとき、複数のハードウェア資源のうちのいくつが存在するかについての問い合わせに、第1の値を返すように応答し、一方、プログラム実行回路が第2のプログラムを実行しているとき、第2の部分内のこれらのハードウェア資源に対応する値を返すことによって、そのような問い合わせに応答するように、ハードウェア資源へのアクセスを制御する。  (もっと読む)

(もっと読む)

分散システム内の種々のコンポーネントの活動を同期させること

インターコネクトを介して受信側デバイスにトランザクション要求を発行するイニシエータデバイスが開示される。イニシエータデバイスは、前記インターコネクトから要求を受信し、前記インターコネクトに要求を発行する少なくとも1つのポートと、バリアトランザクション要求を生成するバリア発生器とを備え、バリアトランザクション要求は、インターコネクトを通過するトランザクション要求のストリーム内の少なくともいくつかのトランザクション要求の順序付けが、バリアトランザクション要求に関してトランザクション要求のストリームにおいてバリアトランザクション要求の前に発生するトランザクション要求の少なくともいくつかの再順序付けを可能にしないことによって維持されるべきであることを、インターコネクトに示し、トランザクション要求の少なくとも部分集合の進捗を問い合わせる同期要求の受信に応答して、イニシエータデバイスは、トランザクション要求の少なくとも部分集合内の任意の保留中のトランザクション要求を実行し、バリア発生器においてバリアトランザクション要求を生成し、少なくとも1つのポートを介してインターコネクトにバリアトランザクション要求を発行し、バリアトランザクション要求に対する応答を受信することに応答して、同期要求に対する応答としてアクノリッジ信号を発行するように応答する。  (もっと読む)

(もっと読む)

メモリからのデータの配列の読み込みを制御する方法および装置

【課題】フレームバッファ、読み込みオペレーションなど、データ配列に対する改善を提供すること。

【解決手段】ディスプレイコントローラ7は、フレームバッファ3からデータブロックを読み込み、ローカルメモリバッファ8内に格納し、それらのデータブロックをディスプレイ2に出力する。ディスプレイコントローラ7は、類似度メタデータ10を使用して、表示処理されるべき新しいデータブロックがディスプレイコントローラ7のローカルメモリ8内にすでに格納されているブロックに類似しているかどうかを判定する。処理すべきデータブロックがローカルバッファ8内のデータブロックに類似している場合、ディスプレイコントローラは、フレームバッファ3から新しいデータブロックを読み込まず、バッファ8内にある既存のデータブロックをディスプレイ2に供給する。

(もっと読む)

グラフィックス処理システム

【課題】グラフィックス処理システムにおけるフレームバッファ生成および類似のオペレーションに対する改善を提供すること。

【解決手段】トランザクション排除ハードウェアユニット5は、タイルベースのグラフィックスプロセッサによって生成されるタイルのメモリ2内のフレームバッファへの書き込みを制御する。トランザクション排除ハードウェアユニット5は、タイル毎にタイルの内容を表す署名を生成する署名生成器20を有する。署名比較器23は、グラフィックスプロセッサからの新しいタイルの署名をフレームバッファ内のタイルの署名と比較する。署名が一致しない場合、署名比較器23は、書き込みコントローラ24を制御して、新しいタイルをフレームバッファに書き込む。署名が一致する場合、フレームバッファにデータは何も書き込まれず、既存のタイルがフレームバッファ内に残る。

(もっと読む)

メモリ内部のスキャン機能支援

【課題】データを記憶するストレージアレイと、データをストレージアレイとの間で送信するアクセス回路とを備えるメモリが開示される。

【解決手段】アクセス回路は、データをストレージアレイへ入出力するデータ経路を形成する。アクセス回路は、第1のクロック信号の第1の位相に応答してラッチするラッチと、第2のクロック信号の第2の位相に応答してラッチし、出力ラッチを備えるラッチとを備え、第1および第2のクロック信号が互いに同期している。メモリはマルチプレクサとスキャン入力とスキャンイネーブル入力とをさらに備え、マルチプレクサがスキャンイネーブル信号に応答して、マスタ・スレーブ・フリップフロップを形成するラッチを備えるスキャン経路を形成し、スキャンイネーブル信号がアサートされている間に、スキャン入力で入力されたスキャンデータがマスタ・スレーブ・フリップフロップを通過し、出力ラッチによって出力される。

(もっと読む)

トランザクションの優先レベルを設定するデータ処理装置および方法

【課題】トランザクションの優先レベルを設定するデータ処理装置および方法を提供する。

【解決手段】該データ処理装置は、トランザクションを処理する共有リソースと、該共有リソースへ該トランザクションを発行する少なくとも1つのマスタデバイスとを有する。該少なくとも1つのマスタデバイスは、該トランザクションの複数のソースを提供し、該トランザクションのそれぞれは、これに関連付けられた優先レベルを有する。アービトレーション回路は、該共有リソースへ発行された複数のトランザクションの中からあるトランザクションを選択するように、アービトレーションポリシーを適用するために使用され、該アービトレーションポリシーは、該選択を実行する際に、該複数のトランザクションのそれぞれに関連付けられた該優先レベルを使用する。

(もっと読む)

SIMD処理における定数の生成

【課題】SIMD処理に係るデータ処理装置及び方法を提供する。

【解決手段】データ処理装置(2)は、データ要素を記憶することができるレジスタデータ記憶装置と、生成された定数を伴いそれに引き続き関連付けられたデータ数値を有する命令を復号することができる命令デコーダ(14,16)と、命令デコーダ(16)により復号されたデータ処理命令に応答して並列処理レーン内部で少なくとも1つのソースオペランドに対してデータ処理を実行することができるデータプロセッサ(18)とを備え、データプロセッサは、生成された定数及び関連付けられたデータ数値を伴う復号された命令に応答して関連付けられたデータ数値の少なくともデータ部分(1210)を拡張することができ、拡張は、少なくとも1つのソースオペランドの内の1つを形成する生成された定数(1240)を伴う命令に応答すると共に選択された機能に基づいて定数(1240)を生成するように実行される。

(もっと読む)

複数ビット値を格納するための読み出し専用メモリセル

【課題】複数ビット値を格納するための読み出し専用メモリセルを開示する。

【解決手段】該読み出し専用メモリセルは、少なくとも3本の出力線であって、該少なくとも3本の出力線のそれぞれは、異なる複数ビット値を表す、少なくとも3本の出力線と、該3本の出力線のうちの1本と電圧源との間に接続される切り替え装置とを含む。該切り替え装置は、切り替え信号に応答して、該電圧源と該3本の出力線のうちの1本との間の電気接続を提供し、該接続された出力線の電圧は、既定の電圧への接続に応答して値を切り替え、それによって、該出力線によって表される該複数ビット値が選択される。該選択された複数ビット値を出力するための、出力装置も提供する。

(もっと読む)

41 - 50 / 134

[ Back to top ]