アーム・リミテッドにより出願された特許

31 - 40 / 134

階層的な変換テーブル制御

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

タイムスタンプを生成するための方法、装置およびトレースモジュール

【課題】効率的にタイムスタンプを生成することを目的とする。

【解決手段】本発明は、データ処理の分野に関し、特に、データ処理装置または処理のトレーシングの特徴がデータ処理装置によって実行されている間に、タイムスタンプを生成するための方法、装置1およびトレースモジュール12に関する。所定の事象が発生する場合、タイムスタンプリクエストが保留になっていることを示すように、タイムスタンプリクエストフラグ18が設定される。後続のトレースパケットの生成時において、タイムスタンプリクエストフラグは、タイムスタンプリクエストが保留になっていることを示すかどうかが判定され、リクエストが保留になっている場合には、後続のトレースパケットに対応するタイムスタンプが生成され、いかなる保留になっているタイムスタンプリクエストも存在しないことを示すために、タイムスタンプリクエストフラグが設定される。

(もっと読む)

トレースデータの優先度の選択

【課題】トレースデータの容量が大きい場合でも、処理すべきデータの優先度に応じ、重要な情報が失われることを回避する。

【解決手段】集積回路2は、バス相互接続16を経由して、トレース出力デバイス8へ接続される、データソース6としてのプロセッサを備える。トレース出力デバイス8にマップされた異なるメモリアドレスは、異なる優先度レベルに関連付けられる。少なくとも1つのメモリアドレスに書き込まれたトレースデータは、これが受け入れられた、またはトレース出力デバイス8によってデータが処理可能になるまで、伝送がストールされた、第1の優先度レベルを有する。異なるメモリアドレスに関連付けられた別の優先度レベルは、トレース出力デバイス8が、処理する能力を有さない場合、例えば、その時点でそのデータを格納する能力を有さない場合に、データが常に受け入れられるが、破棄される。

(もっと読む)

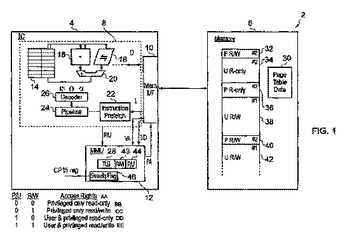

ハードウェアモードおよびセキュリティフラグに基づく、読み出される命令用のメモリエリアの制限

データを処理するための装置(2)は、プロセッサ(8)と、メモリ(6)と、メモリ制御回路(12)とを含む。プロセッサ(8)は、特権モードおよびユーザモードを含む、複数のハードウェアモードで動作する。特権モードで動作している際、プロセッサ(8)は、メモリ制御回路(12)によって、レジスタ(46)内のセキュリティフラグがこの遮断機構が有効であることを示すように設定されている場合にユーザモード内で書き込み可能である、メモリ(6)内のメモリアドレス領域(34、38、42)から命令をフェッチすることを遮断される。  (もっと読む)

(もっと読む)

メモリのセキュア領域および非セキュア領域へのセキュアモードページテーブルデータの格納

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

インターコネクトにおけるデータ・ストア・メインテナンス要求

【課題】長時間に亘って相互作用プロセスの一貫した挙動を確保することを可能にする仕組みを提供する。

【解決手段】インターコネクト回路は複数のパスのうちの少なくとも1つに沿って、データ・ストア・メインテナンス操作を送信し、引き続きバリア・トランザクション要求を送信することによりデータ・ストア・メインテナンス操作の受信に応答するように構成され、トランザクション要求のストリームの中でデータ・ストア・メインテナンス要求の後に続く少なくともいくつかのトランザクション要求がバリア・トランザクション要求によってデータ・ストア・メインテナンス要求の後に保持されるように、いくつかのトランザクション要求の順序付けを維持するように構成され、少なくとも1つの入力から受信されたトランザクション要求を少なくとも1つの出力へルーティングする制御回路と、を備える。

(もっと読む)

フレームバッファにおけるウィンドウ表示の形成

【課題】各タイルの全ピクセル値のこのような読み取りおよび書き込みを行うことは、不利に高い回数のメモリアクセスを要求する。その結果、スピードの低下およびエネルギー消費の増大が生じることとなる。

【解決手段】遅延描画コマンドを用いるウィンドウ表示は、タイルメモリ40内に記憶された1つまたは複数の新規のピクセル値を形成するようにフレームバッファ30のタイル22に対して書き込む描画コマンドを処理することにより動作する。タイルメモリ内のどのピクセルが、新規のピクセル値を記憶するダーティピクセルであり、タイルメモリ内のどのピクセルが、新規のピクセル値を記憶しないクリーンピクセルであるかを示すダーティピクセルデータも、形成される。ダーティピクセルデータに応じて、タイルメモリ内に記憶された新規のピクセル値は、フレームバッファメモリに対して書き込まれる。タイルメモリ内のクリーンピクセルに対応するフレームバッファメモリ内に記憶されたピクセルは、書き込まれることがないため、変更されないままとなる。

(もっと読む)

グラフィック処理システム

【課題】グラフィック処理システムにおける累積バッファ動作を提供する。

【解決手段】グラフィック処理システムの累積バッファ工程は、全体で累積されたフレームを構成する各サブフレームを順繰りにレンダリングすることによりではなく、累積されたフレームを構成する各個々のタイル2、3、4、及び5に異なるレンダリングパスの系列を個々に経験させることにより実行される。従って累積されたフレームを構成する各個々のタイルに関して、いくらかのサブタイル(例えば2'、2''、2'''、及び2'''')は順繰りに生成され、問題のタイルの累積されたバージョンとして出力される最終累積タイル(2acc)を提供するのに1つに累積される。これは累積されたフレーム1を構成している残りの個々のタイル3、4、及び5のそれぞれに関して反復され、個々の累積されたタイル2acc、3acc、4acc、及び5accは出力の累積されたフレーム6を提供するのに1つに結合される。

(もっと読む)

電圧調整回路

【課題】電圧調整回路を提供するための改善された技法を提供する。

【解決手段】供給電圧ノードを出力電圧ノードに接続するプルアップp型閾値デバイスであって、制御信号に依存してオフに切り替えられるように構成されるプルアップp型閾値デバイスを備える電圧調整回路が提供される。プルダウンスタックは、出力電圧ノードを基準電圧ノードに接続し、プルダウンスタックは、直列で接続されるプルダウンp型閾値デバイスおよびプルダウンn型閾値デバイスを備える。インバータは、出力電圧ノードから入力を受け取るように構成され、カットオフ信号を生成するように構成され、プルダウンn型閾値デバイスは、制御信号に依存してオンに切り替えられるように構成され、プルダウンp型閾値デバイスは、カットオフ信号に依存してオフに切り替えられるように構成される。

(もっと読む)

集積回路の作動パラメータモニター

【課題】単純な一連の境界提供ウェーハ承認試験に依存すると、MOSFETパラメータは、文脈依存影響と、ウェーハモニターが設置される離れた場所からは監視することができない局所的な変化と、が原因で、システムオンチップ埋め込みMOSFETモニターに比べて精度が低くなる。

【解決手段】集積回路2は、リング発振器22の形態の1つ又はそれ以上の監視回路14、16、18、20を備えている。これらのリング発振器22は、漏洩モードで作動する電流制限トランジスタ42を含む複数のトライステートインバータ24、26、28を含んでいる。トランジスタ42を通過する漏洩電流は、監視される集積回路2の作動パラメータに依存する。従って、リング発振器22の振動周波数FOSCは、測定されるべき作動パラメータに依存して変化する。

(もっと読む)

31 - 40 / 134

[ Back to top ]