エヌエックスピー ビー ヴィにより出願された特許

71 - 80 / 657

映像信号の動き補償処理の方法および装置

映像の動き補償処理を行うにあたり、入力映像を縮小し、縮小映像とする、縮小ステップ(sc1)と、前記縮小映像に動き補償処理を施し、動き補償映像とする、動き補償処理ステップ(ME UPC)と、前記動き補償映像を拡大し、拡大動き補償映像とする、拡大ステップ(sc2)と、前記拡大動き補償映像を入力映像に合成し、出力映像とする、合成ステップ(M)とを実行する。  (もっと読む)

(もっと読む)

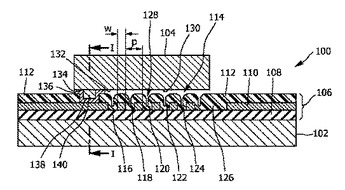

基板と基板上の突起電極との間の応力低減

本発明は、基板及び突起電極を有する半導体部品に関するものである。突起電極は、基板に対面する基板面を有し、この基板面は、ギャップによって基板から分離された第1基板面部分を備えている。このギャップは、突起電極の基板に対する応力補償変形を可能にする。突起電極の基板面はさらに、基板に機械的に固定接続及び電気接続された第2基板面部分を備えている。突起電極と基板との機械接続のより小さいフットプリントにより、突起電極は、同量の応力を基板上またはアセンブリ内の外部基板に伝えることなしに、加えられた機械的応力に三次元的に追従することができる。このことは、半導体部品を突起電極によって外部基板に接続したアセンブリの改善された寿命を生じさせる。  (もっと読む)

(もっと読む)

エッチングステップ中の電極の適正なアンダーカットの試験方法

基板上のプローブ電極構造を記載し、このプローブ電極構造は、第1プローブ電極及びこれに隣接する第2プローブ電極を層配列上に備え、この層配列は全体的に、基板からプローブ電極に向かって、導電性の最下層、電気絶縁性の中央層、及び導電性の最上層を備えている。本発明のプローブ電極構造は、第1プローブ電極外の領域から最上層を除去することを目的としたエッチングステップ中の、第1プローブ電極のアンダーカットを検出する手段を提供する。第1電極の第1エッジからの許容可能な距離を超えるアンダーカットは、第1プローブ開口部内の第1最上層プローブ部分を除去し、このことは、第1プローブ電極と第2プローブ電極との間の電気抵抗の検出可能な変化を生じさせる。  (もっと読む)

(もっと読む)

信号符号化変調搬送波信号の周波数を測定する装置および方法

変調されていない(CSU)あるいは所定の信号符号化に従って変調されている(CSM)搬送波信号(CS)を含むものと予期される入力信号(IN)の周波数を測定する装置(10)であって、測定期間(MP)を生成するための手段(9)と、前記測定期間(MP)の間に前記入力信号(IN)のエッジをカウントするように構成された入力信号カウンタ(2)と、前記入力信号(IN)がエッジを含むかどうか検出するサンプリング手段(4)と、前記測定期間(MP)の満了時に、前記入力信号カウンタ(2)のカウント値(CNT_2)を読み込み、前記入力信号カウンタ(2)のカウント値(CNT_2)から前記入力信号の周波数(FR)を導き出すように構成された制御手段(7)とを備え、前記測定期間(MP)を生成するための手段(9)は、前記入力信号(IN)のエッジの欠如が検出される期間(EXP)だけ測定期間(MP)を延長する周波数測定装置。  (もっと読む)

(もっと読む)

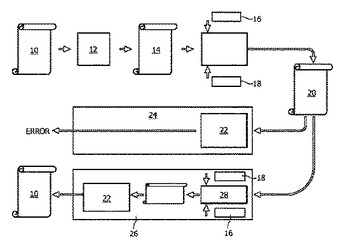

メディア再生デコーダ及びその追跡方法

装置内に組み込まれた追跡中のメディア再生デコーダを識別する方法において、追跡メッセージを表現するデータをメディアコンテンツファイルのコンテンツフィールド内に含め、トリガストリング(16)をファイルのユーザーデータフィールド内に含める。このファイルをデコーダに入力し、追跡中のデコーダは、トリガ信号の検出に応答して追跡メッセージを所望フォーマットにするように構成されている。デコーダが追跡中のデコーダでなければ、トリガストリングは無視され、ソフトウェアコンポーネントは、メディアコンテンツファイルを通常のメディアコンテンツファイルのように処理しようとし、このことはエラーを生じさせる。  (もっと読む)

(もっと読む)

デュアルインタフェースのメモリ装置および方法

本発明は、垂直方向と水平方向に切られたメモリマッピングの組み合わせから形成されるチェック模様のメモリマッピングを使用するデュアルインタフェースのメモリ装置を提供し、マッピングメモリにアクセスするよう構成した2次元アクセス手段を有し、このアクセス手段は、双方のインタフェースにマッピングされたメモリに水平方向および垂直方向にオーバーラップするよう構成し、前記メモリ装置は、好適にも各インタフェースのための2個のDTLチャネルを提供し、これにより、CPU、オーディオ、ビデオおよびグラフィックス処理のようなすべての処理態様に対して極めて効率のよい統合メモリ装置が得られる。  (もっと読む)

(もっと読む)

集積回路及びこれを備えるアセンブリ

高周波数で用いるのに適しており、且つ、入力と出力を有する第1のキャパシタ及びグランド接続を備える集積回路であって、キャパシタは、該キャパシタの出力とグランド接続との間の抵抗を介してESD保護され、抵抗は、グランド接続のRF性能への実質的な影響を阻止するように充分に高い抵抗値を有する、集積回路。  (もっと読む)

(もっと読む)

D級音声増幅器

D級増幅器(1)は、デジタル入力信号(Vin)を受信する入力ユニット(11)、入力信号(Vin)に基づいてパルス整形信号を生成するパルス整形ユニット(12)、パルス整形信号を比較し、また比較器信号を生成する比較器ユニット(13)、比較器信号に基づいてドライバ信号を生成するドライバユニット(14)、ドライバ信号に基づいてパルス幅変調出力信号(Vout )を生成する切り替え出力ユニット(15)、および出力信号(Vout )をパルス整形ユニット(12)にフィードバックするフィードバックユニット(16)を有する。入力ユニット(11)は、パルス幅変調出力信号(Vout )のデューティサイクルを制御するクリッピング制御ユニット(10)を有する。  (もっと読む)

(もっと読む)

パワーアンプ・アセンブリ

パワーアンプモジュールが、熱ビア及び端子、並びに半導体材料の相互接続基板を有するプラットフォームデバイスを備えた積層基板を備えている。この基板は、その第1面に電気相互接続が設けられ、反対側の第2面は積層基板上に装着されている。導電接続部が、第1面から基板を通って第2面に延びる。パワーアンプデバイスが基板の第2面に取り付けられている。相互接続基板を通る導電接続部の1つはパワーアンプ用の接地経路であり、熱経路は半導体材料によって設ける。相互接続基板には最適な厚さが存在し、この厚さにおいて、適切な接地及び許容可能な熱放散が共に行われる。  (もっと読む)

(もっと読む)

負荷ラインの適応

明細書中に開示される一般的概念に従って、パワーアンプ(300)出力に接続された負荷ラインの予め定められた負荷ラインインピーダンスに負荷インピーダンス(z load)を適応整合させるための回路は、パワートランジスタと適応整合回路ネットワーク(101)との間に固定整合ネットワーク(201)を含む。固定整合ネットワークはインピーダンスインバータとして機能し、結果として、高電力での挿入損失が比較的低くなる。結果として、インピーダンス反転ネットワークが10倍以上のインピーダンス変動でも使用可能となることが分かる。さらに、パワートランジスタ付近で固定整合ネットワークを使用することにより、伝送零点の実現が可能となり、および/または、基準周波数での(可変)負荷インピーダンスとは無関係に、予め定められた高調波周波数での十分に規定された負荷インピーダンスが可能となる。  (もっと読む)

(もっと読む)

71 - 80 / 657

[ Back to top ]