グローバルファウンドリーズ・インコーポレイテッドにより出願された特許

1 - 10 / 18

フィンを含む半導体構造およびその形成方法

【課題】フィン高さの改良を図れるフィンの形成方法を提供すること。

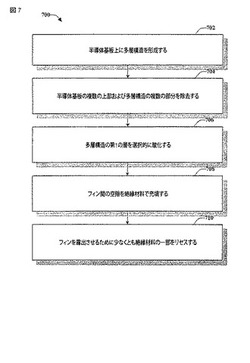

【解決手段】実施形態のフィン形成の方法は、まず、半導体基板上に多層構造を形成する。前記半導体構造は、前記半導体基板上の第1の層、前記第1の層上の第2の層および前記第2の層上の第3の層を具備する。次に、前記半導体基板および前記半導体構造の複数の部分からなる複数のフィンを形成するために、前記半導体基板の複数の上部および前記半導体構造の複数の部分を除去する。次に、前記第2の層および前記第3の層の酸化速度を前記第1の層よりも酸化速度よりも小さくしながら、前記第1の層を選択的に酸化する。次に、前記選択的な酸化の後に前記複数のフィン間の空隙を絶縁材料で充填する。そして、フィンを露出させるために少なくとも前記絶縁材料の一部をリセスし、前記フィンの少なくとも一つの側面または前記フィンの上面をチャネル領域にする。

(もっと読む)

ゲート型横型サイリスタベースランダムアクセスメモリ(GLTRAM)セルを製造するための方法

【解決手段】

ゲート型横型サイリスタベースメモリデバイス(gltram)を製造するための方法が提供される。半導体層(406)内の第1の伝導性タイプの第1、第2、第3及び第4のウエル領域(463,471,486,493)を含む半導体層(406)が設けられる。第1のゲート構造(465/408)は第1のウエル領域(463)上にあり、第2のゲート構造(475/408)は第2のウエル領域(471)上にあり、第3のゲート構造(485/408)は第3のウエル領域(486)上にあり且つ第2のゲート構造(475/408)と一体であり、第4のゲート構造(495/408)は第4のウエル領域(493)上に配置される。第1のゲート構造(465/408)の第1の側壁(414)及び第2乃至第4のゲート構造(475/408,485/408,495/408)の側壁(412,413,416,417,418,419)に隣接して側壁スペーサ(469)が形成される。また、第1のウエル領域(463)の部分(468)及び第1のゲート構造(465/408)の部分を覆う絶縁スペーサブロック(467)が形成される。絶縁スペーサブロック(467)は第1のゲート構造(465/408)の第2の側壁(415)に隣接する。第1のゲート構造(465/408)に隣接して第1のソース領域(472)が形成され、第1及び第2のゲート構造(465/408,475/408)の間に共通ドレイン/カソード領域(474/464)が形成され、第3のゲート構造(485/408)に隣接して第2のソース領域(482)が形成され、第3及び第4のゲート構造(485/408,495/408)の間に共通ドレイン/ソース領域(484/492)が形成され、第4のゲート構造(495/408)に隣接してドレイン領域(494)が形成される。第1のゲート構造(465/408)に隣接する絶縁スペーサブロック(467)の下で第1のウエル領域(463)内に延在する第1のベース領域(468)が形成され、第1のベース領域(468)に隣接する第1のウエル領域(463)内に延在するアノード領域(466)が第1のウエル領域(463)内に形成される。

(もっと読む)

論理エラー保護のためのハイブリッド冗長性を備えたプロセッサ

プロセッサコア(100)は、複数の整数実行ユニット(154a,154b)に同じ整数命令ストリームをディスパッチし、浮動小数点ユニット(160)に同じ浮動小数点命令ストリームを連続的にディスパッチしうる命令デコードユニット(140)を有する。前記整数実行ユニットは、各クロックサイクル中に、各整数実行ユニットが同じ整数命令を実行するように、ロックステップ方式で動作しうる。前記浮動小数点ユニットは、前記同じ浮動小数点命令ストリームを2回実行しうる。比較ロジック(158a,158b,163)は、前記整数命令がリタイヤする前に、前記整数実行ユニットのそれぞれからの実行結果間の不一致を検出しうる。また、前記比較ロジックは、前記浮動小数点命令ストリームの前記実行の結果を前記浮動小数点ユニットから転送する前に、各連続する浮動小数点命令ストリームの実行の結果間の不一致を検出しうる。更に、前記比較ロジックは、不一致を検出すると、前記不一致を発生させた命令を再実行させうる。  (もっと読む)

(もっと読む)

プロセッサで実行中のプログラムソフトウェアをプロファイルするためのメカニズム

1つ以上のプロセッサコア(15)を有するプロセッサ(12)は、1つ以上のプロセス(P1,P2)を含む命令を実行する実行ロジックを有する。各プロセスは1つ以上の実行スレッド(T1,T2)を含んでもよい。また、前記プロセッサは、モニタロジック(18)とモニタプロセス(モニタコード)とを有するプロファイリングメカニズムを有する。前記モニタロジックは、前記1つ以上のプロセスをモニタし、モニタされている前記1つ以上のプロセスの制御のフローに割り込むことなく、前記1つ以上のプロセスに関連するパフォーマンスデータへのアクセスを提供する。前記モニタプロセスは、前記パフォーマンスデータを収集しうる。また、前記モニタプロセスは、ユーザモードで動作中に、前記1つ以上のプロセッサコアによって実行可能なプログラム命令を含んでもよい。  (もっと読む)

(もっと読む)

一般作業負荷およびグラフィックス作業負荷を処理するための統合プロセッサアーキテクチャ

1つ以上の制御ユニットと、複数の第1の実行ユニットと、1つ以上の第2の実行ユニットとを備えるプロセッサである。プロセッサ命令セットに適合するフェッチされた命令が、第1の実行ユニットに送られる。第2の命令セット(プロセッサ命令セットとは異なる)に適合するフェッチされた命令が、第2の実行ユニットに送られる。第2の実行ユニットは、グラフィックス演算を実行するように構成され、またはJavaバイトコード、マネージドコード、ビデオ/オーディオ処理演算、暗号化/復号化演算などの実行のような他の特殊な機能を実行するように構成されてもよい。第2の実行ユニットは、コプロセッサのように動作するように構成されてもよい。単一の制御ユニットが、すべての実行ユニットに対するフェッチ、デコード、およびスケジューリングを処理してもよい。他の形態として、マルチ制御ユニットが、実行ユニットの異なるサブセットを処理してもよい。 (もっと読む)

複数サイズ対応のパッケージソケット

複数のサイズのチップパッケージ基板(40,335)(50,337)用の各種ソケット(20,320)が開示される。一態様では、第1の半導体チップパッケージ基板(40,335)または第2の半導体チップパッケージ基板(50,337)を収容するために適合された内部空間(140,350)を画定する周縁壁(120,340)を有するソケット(20,320)を備える装置が提供される。前記第1の半導体チップパッケージ基板(40,335)は第1のサイズおよび第1の複数の構造的特徴(160a,420a)を有し、前記第2の半導体チップパッケージ基板(50,337)は前記第1のサイズとは異なる第2のサイズおよび第2の複数の構造的特徴(180a,490a)を有する。前記ソケット(20,320)は前記第1の半導体チップパッケージ基板(40,335)を前記内部空間(140,350)内の第1の予め選択された位置に配置させるか、前記第2の半導体チップパッケージ基板(50,337)を前記内部空間(140,350)内の第2の予め選択された位置に配置させるかを選択的に可能とするために、いずれかの半導体チップパッケージ基板の前記特徴と係合するように動作可能な第3の複数の構造的特徴(130a,130b,390a)を有する。  (もっと読む)

(もっと読む)

半導体デバイスにおいてゲート電極高を調整するための方法

高エネルギー注入プロセス(203)中に、高度な半導体デバイス(200)のゲート電極構造(252)上に注入ブロック材料(258)を設けることによって、トランジスタ(250A,250B)のチャネル領域(255)に対する必要な遮蔽効果を得ることができる。後の製造段階において、層間絶縁材料(210)の堆積時のプロセス条件を向上させるために、注入ブロック部分(258)が除去されてゲート電極高さ(253H)が所望の高さに低減され、これにより、高密度のデバイス領域であっても、層間絶縁材料(210)内にボイドなどの不規則性が形成されるリスクを大幅に低減することができる。  (もっと読む)

(もっと読む)

導電性の構造物を含む半導体構造および形成方法

半導体構造(300)は、半導体基板(301)を有する。前記半導体基板(301)の上に電気絶縁材料の層(304)が形成されている。前記電気絶縁材料の層(304)に導電性の特徴(312)が形成されている。前記導電性の特徴(312)と前記電気絶縁材料の層(304)の間に第1の半導体材料の層(320)が形成されている。  (もっと読む)

(もっと読む)

クロックサイクルスチールのための方法および装置

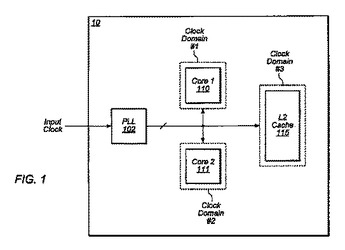

複数のクロック信号を生成するための方法。前記方法は、位相ロックループ(PLL)を使用して基準クロック信号を生成するステップを有する。前記基準クロックが、複数のクロック分周器ユニットのそれぞれに供給され、前記複数のクロック分周器ユニットのそれぞれが、前記受信基準クロック信号を分周して、対応する分周クロック信号を生成する。前記方法は、前記対応する受信分周クロック信号の周波数と、除去するサイクル数とに基づいて、それぞれが有効周波数を有する複数のドメインクロック信号を生成するために、(所定の数のサイクルにつき)1以上のクロックサイクルを除去する。  (もっと読む)

(もっと読む)

種類および膜厚の異なるゲート絶縁層を有するCMOSデバイス、ならびにその形成方法

high−k金属ゲート構造(310N,310B,310P)によって従来のゲート電極構造(310)を置換するためのプロセスシーケンスにおいて、例えば、選択性の高いエッチングステップ(322,325,327,331)を使用することによって、追加のマスク形成ステップの数を少なく保つことができ、これにより、従来のCMOS技術との高い互換性を保つことができる。更に、ここに開示の技術は、前工程(front-end)のプロセス技術および後工程(back-end)のプロセス技術との互換性を実現し、これにより、トランジスタレベルのほか、コンタクトレベルでも実績のある歪み発生機構を組み込むことが可能となる。  (もっと読む)

(もっと読む)

1 - 10 / 18

[ Back to top ]