シノプシス, インコーポレイテッドにより出願された特許

11 - 20 / 33

詳細なルーティング可能性推定を計算するための方法および装置

本発明の一実施形態は、回路レイアウトに関連する一群の局所ルーティング領域にわたるルーティング可能性推定を計算する、システムを提供する。本システムは、まず、ルートオーバーフローに関連する、第1の局所ルーティング領域を選択し、それぞれの局所ルーティング領域は、回路レイアウトの領域内のルーティング層に対するいくつかのルーティングオーバーフローの推定に関連付けられる。さらに、それぞれのルーティング層は、好ましい方向変数Dに関連付けられる。次に、システムは、第1の局所ルーティング領域のオーバーフロールーティング層から、方向dにおけるk以上のルートのオーバーフローを処理する能力を有する、第2の局所ルーティング領域に、方向dにおけるオーバーフロー値kを転送する。最後に、システムは、グローバルオーバーフローコストおよび隣接するオーバーフローコストの関数として、グローバルルーティング可能性推定を計算する。  (もっと読む)

(もっと読む)

フォトマスク形状の非均一分割を検出するための方法および機器

本発明の一実施形態は、所望の構成とは異なる基本形状の構成に分割された所与の形状の発生を検出する、システムを提供する。該システムは、所与の形状の分割形状インスタンス化を選択し、それと所与の形状の他の分割形状インスタンス化が比較される。比較過程の一部として、該システムは、選択した分割形状インスタンス化における少なくとも1つの基本形状に一致するマスクパターン記述における基本形状を含む、フィルタ処理したマスクパターン記述を生成する。次に、該システムは、所与の形状に一致する、フィルタ処理したマスクパターン記述からの第1の組の形状発生を識別し、所与の形状に一致する、マスクパターン記述からの第2の組の形状発生を識別する。次いで、該システムは、第1および第2の組の形状発生の間で排他的OR比較を行うことによって、第3の組の形状発生を生成する。  (もっと読む)

(もっと読む)

多重レベルのマスキング解像度用の交番位相偏移マスキング

【課題】多重造形クラスに対する多重位相偏移マスク解像度レベル用の交番位相偏移マスクを製作する。

【解決手段】層を定義するフォトリソグラフィ・マスク用の、前記層内の第1及び第2造形クラスの造形を定義するパターンを処理する段階と;第1造形解像度レベル用の位相偏移ウィンドウ対に関する第1レイアウト寸法と、第2造形解像度レベル用の位相偏移ウィンドウ対に関する第2レイアウト寸法とを定義する段階と;前記第1造形クラスに対して前記位相偏移ウィンドウ対に関する第1レイアウト寸法を使用する段階と、前記第2造形クラスに対して前記位相偏移ウィンドウ対に関する第2レイアウト寸法を使用する段階とを含む、複数の位相偏移ウィンドウ対をレイアウトする段階と;前記複数の位相偏移ウィンドウ対内の位相偏移ウィンドウに第1及び第2位相偏移値を割り当てる段階から構成されている。

(もっと読む)

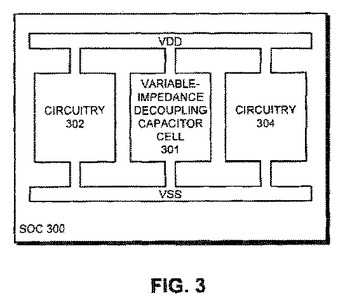

可変インピーダンスゲートデカップリングセル

本発明の実施形態は、電力レールと、接地レールとを含む、電力システム内のノイズを制御するシステムを提供する。システムは、電力レールと接地レールとの間でデカップリングコンデンサと直列に連結される、MOSトランジスタと、MOSトランジスタおよびデカップリングコンデンサと並列に電力レールに連結される、誘導パッケージング接続とを含む。MOSトランジスタ、デカップリングコンデンサ、および誘導パッケージング接続の組み合わせは、共振回路を形成する。動作中、システムは、電力レール上のVdd信号中にノイズが存在するかを判定する。Vdd信号中に存在するノイズに基づき、システムは、他の周波数でのスイッチングノイズの不必要な増加を引き起こすことなく、共振回路の関心周波数(ωinterest)付近の周波数範囲内のノイズを低減するように、MOSトランジスタのインピーダンスを調整する。  (もっと読む)

(もっと読む)

半導体基板におけるイオン注入損傷のトラップ方法

結晶格子内へのドーパント注入時に、前記格子の注入領域に生じる欠陥の影響を最小化する方法。前記方法は、前記格子を構成する原子よりもサイズの小さいトラップ原子をトラップ層に注入する工程から始まる。注入後、前記格子は、格子間欠陥原子が欠陥領域から放出されるのに十分な時間アニールされる。そうすることで、トラップ原子と放出された格子間原子のエネルギー的に安定したペアが形成される。  (もっと読む)

(もっと読む)

半導体基板における格子欠陥の抑制方法

結晶格子に対するドーパント注入後に、リークを促進する欠陥が格子に形成されるのを抑制する方法。前記方法のプロセスは、格子を構成する原子よりもサイズが大きい原子からなる圧縮層を提供する。次に、格子間欠陥原子が圧縮層から放出されるのに十分な時間、格子をアニールする。こうすることで、エネルギー的に安定した欠陥が、圧縮層から離間して格子内に形成される。  (もっと読む)

(もっと読む)

配置配線システムにおける設計最適化のためのフィラーセル

集積回路設計において、複数の回路レイアウトセルを相互の間に間隙を設けてレイアウトし、前記間隙の少なくとも一部の所定の間隙の夫々に、前記所定の間隙に隣接する少なくとも1つの回路レイアウトセルの性能パラメータに対して所望される影響に基づいて所定のデータベースから選択された対応するフィラーセルを挿入するためのシステム及び方法を提供する。前記回路レイアウトセルは複数行にわたって配列されており、幾つかの実施形態では、所定の間隙に対する適切なフィラーセルの選択は、前記所定の間隙の両側に隣接する回路レイアウトセルの性能パラメータに依存する。前記所定のフィラーセルは、例えば、ダミー拡散領域、ダミーポリシリコン線、Nウェル境界の移動、エッチング停止層境界の移動を備える。一実施形態では、回路レイアウトセルは、選択されたフィラーセルを収容するために移動させることができる。  (もっと読む)

(もっと読む)

ダミーフィルセルのセットの使用によるダミーフィル実施の方法および装置

一実施形態は、標的密度の範囲内の標的密度を達成するように設計レイアウトでダミーフィルを実施する。動作中、システムは、その密度が標的密度の所望の範囲内ではない領域を含む、設計レイアウトを受容する。次に、システムは、ダミーフィルアレイを配置して、任意にサイズ決定された長方形を充填するために使用することができる、ダミーフィルセルのセットを受容する。ダミーフィルセルは、ダミーフィルアレイのサイズに関係なく、ダミー形状を適切にプリントさせる、補助特徴および光近接効果補正を含有してもよい。次いで、システムは、ダミーフィルセルで充填するために、設計レイアウトにおいて多角形を決定する。次に、システムは、多角形を長方形のセットに破砕する。システムは、長方形を充填するダミーフィルアレイを配置するために、ダミーフィルセルのセットを使用する。  (もっと読む)

(もっと読む)

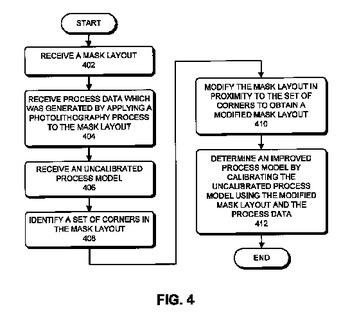

マスク角部円形化効果のモデル化によるプロセスモデル精度の向上

一実施形態は、マスク角部円形化(MCR)効果をモデル化する改良型プロセスモデルを決定するシステムおよび技術を提供する。動作中、システムは、マスクレイアウトと、マスクレイアウトにフォトリソグラフィープロセスを適用することによって生成されたプロセスデータとを受信してもよい。システムはまた、一式のMCR構成要素を含有してもよい、未較正プロセスモデルを受信してもよい。次に、システムは、マスクレイアウトにおいて一式の角部を識別してもよい。次いで、システムは、修正されたマスクレイアウトを得るように、一式の角部に近接するマスクレイアウトを修正してもよい。あるいは、システムは、一式のマスク層を決定してもよい。次に、システムは、修正されたマスクレイアウトおよび/または一式のマスク層、およびプロセスデータを使用して、未較正プロセスモデルを較正することによって、改良型プロセスモデルを決定してもよい。  (もっと読む)

(もっと読む)

アーキテクチャー上の物理的合成

【課題】高レベル記述から合成プロセスを通して集積回路を設計する方法及び装置を提供する。

【解決手段】本発明は、集積回路を設計する方法及び装置を開示する。1つの態様によれば、本発明の回路設計は、合成及び配置の繰り返しプロセスを開示し、各繰り返しは、集積回路の設計に対する増分的変化を与える。本発明の増分的繰り返し解決策は、合成から配置へ及びそれとは逆の連続的な進行を与え、現在インスタンス配置を知ることで合成に対する増分的改善がなされ、現在回路ロジックを知ることで配置に対する増分的改善がなされる。別の態様によれば、本発明の回路設計は、異種リソース分布問題に対処するためにリソースレイヤを使用する増分的力指向配置変換を開示し、インスタンスに対する力は、それらリソースのローカル混雑に基づきリソースレイヤからの力の重み付けされた平均となる。更に、増分的なエリア除去方法を使用し、リソース需要トポロジーマッピングのような力指向配置変換に基づくクオリティメトリックを通してリソース利用問題に対処することができる。

(もっと読む)

11 - 20 / 33

[ Back to top ]