旺宏電子股▲ふん▼有限公司により出願された特許

11 - 20 / 27

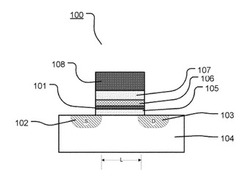

ポリ間電荷トラップ構造体を有する浮遊ゲートメモリ素子

【課題】非対称な複数のトンネル障壁を有する電荷トラップ浮遊ゲートメモリ素子を提供する。

【解決手段】本メモリセルはチャネル領域で分離されたソース領域及びドレイン領域を備える。第1トンネル障壁構造体が該チャネル領域の上方に配置されている。浮遊ゲートが該第1トンネル障壁構造体上に配置され該チャネル領域を覆っている。第2トンネル障壁構造体が該浮遊ゲート上に配置されている。該第2トンネル障壁構造体上に電荷トラップ構造体が配置され、該電荷トラップ構造体上に阻止誘電構造体が配置されている。該上部誘電構造体上に配置された上部導電層がゲートとして働く。該メモリセルをプログラムするバイアス条件下及び消去するバイアス条件下で、該第2トンネル障壁構造体は該第1トンネル障壁構造体より効率的なトンネル電流の導体である。

(もっと読む)

高κキャップ阻止誘電体‐バンドギャップ操作SONOS及びMONOS

【課題】阻止誘電体操作電荷トラップメモリーセルを提供する。

【解決手段】この阻止誘電体操作電荷トラップメモリーセルは、阻止誘電体によってゲートから分離された電荷トラップ要素を備える。該阻止誘電体は該電荷トラップ要素に接し高品質に作ることができる二酸化シリコン等のバッファ層(第1層)と、該ゲートに接するキャップ層(第2層)とを含む。該キャップ層は第1層より高い誘電率を有し、高κ材料でできているのが好ましい。第2層は相対的に高い伝導帯オフセットも有している。チャネルと該電荷トラップ要素の間にバンドギャップ操作トンネル層が設けられ、該多層阻止誘電体と組合わされて正孔トンネル現象による高速消去動作を可能にする。或いは、単一層からなるトンネル層が使用されてもよい。

(もっと読む)

高速プログラム型のMLCメモリ

【課題】フラッシュ・マルチレベルメモリセル(MLC)メモリをプログラミングする方法および装置を提供する。

【解決手段】この方法は、データをSRAM内にロードするステップと、前記SRAM内の前記データから複数のマルチビットワードを読み出すステップと、ワードを少なくとも1個のラッチバッファにロードするステップと、少なくとも1個のラッチバッファ内のワードの1つからの1つまたは複数のビットを、少なくとも1個のラッチバッファ内の別のワードからの1つまたは複数のビットと対にするステップと、前記ビット対のどれにプログラミングが必要であるかを決定するステップと、前記メモリセルを前記決定されたビット対と共に並列プログラミングするステップとを備える。

(もっと読む)

積層型薄膜トランジスタ型不揮発性メモリ装置、およびその製造方法

【課題】積層型不揮発性メモリ装置を提供する。

【解決手段】積層型不揮発性メモリ装置は、互いの上面に積層された、複数のビット線層とワード線層とを含む。ビット線層は、高度なプロセス技術を使用して形成することができる複数のビット線を含み、装置の製造を効率的かつ費用効率の高いものとしている。装置はNAND演算用に構成することができる。

(もっと読む)

浮遊ゲートNANDフラッシュメモリ用のゲート注入を用いるセル動作方法

【課題】浮遊ゲートに対して効率的なFNトンネリングを可能にするように、浮遊ゲート装置を動作させること。

【解決手段】フラッシュメモリ素子上で動作を行う方法であって、浮遊ゲートと制御ゲートの間にゲート結合率が0.4未満である場合に用いられる。電位は、制御ゲートを介して印加する必要がある。電子は、制御ゲートから浮遊ゲートに注入されるか、または浮遊ゲートから制御ゲートに放出される。注入および放出に対応した動作は、素子内に提供されるシリコンチャネルの性質によって決定される。この方法には特に、バルク結合FinFET状構造を用いる素子が適している。この方法は特に、NANDアレイ内のセル上で用いる場合にも適している。

(もっと読む)

積層型不揮発性メモリデバイスおよびその製造方法

【課題】窒化物読取専用メモリデバイスを積層する積層型不揮発性メモリデバイス及びその製造方法を提供する。

【解決手段】積層型不揮発性メモリデバイスは、お互いの上に積層された複数のビットライン110,130およびワードライン層120,140を含む。ビットライン層110,130は、前記デバイスの製造を効率的かつ費用効率の良いものとする進歩した加工技術を利用して形成されうる複数のビットラインを含む。デバイスはNAND処理のために構成することができる。

(もっと読む)

不揮発性メモリ素子の動作方法

【課題】メモリ素子の信頼性が浅いトレンチ隔離構造によって生じるバードビーク効果によって影響されず、動作速度が非常に速い、メモリ素子の動作方法を提供すること。

【解決手段】不揮発性メモリ素子の動作方法を提供する。素子は、半導体基板、スタック層、および基板の表面下に配置し、チャネル領域によって分離されたソース領域とドレイン領域を備えたメモリセルを有する。スタック層は、チャネル領域上に配置した絶縁層、絶縁層上に配置した電荷蓄積層、電荷蓄積層上の多層トンネリング誘電体構造、および多層トンネリング誘電体構造上に配置したゲートを有する。ゲートに負のバイアスを供給し、−FNトンネリングによって、多層トンネリング誘電体構造を介して電荷蓄積層に電子を注入し、素子の閾値電圧を増大させる。ゲートに正のバイアスを供給し、+FNトンネリングによって、多層トンネリング誘電体構造を介して電荷蓄積層に正孔を注入し、素子の閾値電圧を減少させる。

(もっと読む)

フラッシュメモリのためのパッシベーション構造およびその製造方法

【課題】下に横たわる装置構成要素を効果的に保護するばかりでなく、従来的パッシベーション構造の形成方法よりも迅速かつ低廉に製造されるパッシベーション構造が必要である。

【解決手段】本発明によるパッシベーション構造は、最小限の層の数を用いて強化されたパッシベーション効果を供する高紫外線透過性珪素(UV−SiN)層を有する半導体装置のためのパッシベーション構造である。このUV−SiN層は実質的に形状に追随して、半導体基板の上に形成された複数の上部金属線上に横たわり、隣接する上部金属線の間に、形状的窪みが明確に示される。スピンオンガラス(SOG)材料が該形状的窪みに埋められる。比較的厚く、上面が実質的に平坦な酸窒化珪素層は、下に横たわる形態を水分から保護するのみならず、アルカリ金属イオンがそこを通ることを防ぐ。酸窒化珪素層は、続く湿潤エッチング処理の間、SOG材料を保護する。

(もっと読む)

バンドギャップ操作SONOSデバイスを用いたサブゲートANDアーキテクチャの構造及び方法

【課題】スケーラビリティを有するAND型フローティングゲートフラッシュメモリを提供する。

【解決手段】ソースサイドインジェクションプログラミング方法を実行するため、ANDアーキテクチャを有するバンドギャップ操作BE‐SONOSデバイス構造は、酸化物141‐窒化物142‐酸化物143‐窒化物144‐酸化物145スタックに重ねられる制御ゲート110と、ゲート酸化物150に重ねられるサブゲート130との間に配されるスペーサ酸化物120を含む。第1の形態においては、BE‐SONOSサブゲートANDアレイアーキテクチャは、サブゲートライン及び拡散ビットラインを有するSONONOSデバイスの複数の列を含む。第2の形態においては、BE‐SONOSサブゲート反転ビットラインANDアーキテクチャは、サブゲート反転ビットラインを有して、拡散ビットラインは有さないSONONOSデバイスの複数の列を含む。

(もっと読む)

不揮発性メモリセルの過剰消去を保護する方法および装置

【課題】不揮発性メモリセルを消去命令に応じて過剰に消去することを保護する方法および装置を開示する。

【解決手段】電荷捕捉メモリセルを消去する方法であって、複数の電荷捕捉メモリセルを消去するために命令に応じてそれぞれが閾値電圧と関連した電荷捕捉構造、プログラミングされた状態および消去された状態を有し、第一バイアス処置を複数の電荷捕捉メモリセルの電荷捕捉メモリセルをプログラミングするために適用することと、第二バイアス処置を複数の電荷捕捉メモリセルで消去された状態を確立するために適用することを含み、前記の複数の電荷捕捉メモリセルの各電荷捕捉メモリセルの電荷捕捉構造がプログラミングされた状態よりも消去された状態で高い正味電子電荷を有することを特徴とする方法。

(もっと読む)

11 - 20 / 27

[ Back to top ]