Fターム[2F085GG16]の内容

未知の時間間隔を測定するもの (1,604) | 計時手段 (305) | 電気化学的手段 (8)

Fターム[2F085GG16]に分類される特許

1 - 8 / 8

時間振幅変換装置

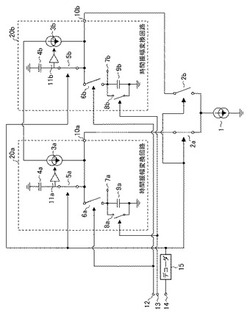

【課題】複数の時間振幅変換回路を有する場合でも、素子ばらつきの影響を小さくすることのできる時間振幅変換装置を得る。

【解決手段】電圧電流変換素子3a,3bは、増幅器11a,11bの出力電圧に対応した電流を出力する。校正時は、時間振幅変換回路20a,20bに対して、スイッチ2a,2b及びスイッチ5a,5bを切り替えることで、各々基準電流源1を接続し、電圧電流変換素子3a,3bの出力電流値を基準電流源1の電流値に収束させた際の電圧値を容量素子4a,4bの値として記憶する。

(もっと読む)

再利用可能なタイマー表示装置

【課題】温度依存性がなく再利用が可能なタイマー表示装置を提供する。

【解決手段】2つの導電層で挟み込まれたエレクトロクロミック層を含むタイマー表示層と、タイマー表示層に電力を供給するための電源と、タイマー表示層と電源との間を電気的に接続及び切断する切換手段とを備え、切換手段によってタイマー表示層と電源との間を電気的に切断することによりタイマー表示層のタイマー表示機能を駆動する、再利用可能なタイマー表示装置。

(もっと読む)

稼動時間計

【課題】 稼動時間計の低コスト化を図ることを可能にする。

【構成】 稼動時間計1は、正極21、負極22を有した電極板20と、電極板20に電圧を通電するための入力端子51,52と、電極板20にイオンを伝導させるための電解質60が入れられたハウジング10とを備えている。電気機器2の稼動に際して入力端子51,52に電圧が入力されると、電極板20の正負極間に電圧が通電され、電解質60を通じて電流が流れ、これに伴って、その電気量に応じて電極板20の正極21の電気的腐食が進行する。そして、正極21の電気的腐食の進行度がハウジング10外から視認可能になっている。

(もっと読む)

RC放電回路、電源管理回路

【課題】測定分解能が向上したRC放電回路等を提供する。

【解決手段】コンデンサ(C)に蓄積された電荷を電気抵抗(R1、R2)を含む抵抗部を介して放電するRC放電回路(33)を、前記コンデンサの充電電圧を検出する検出部を含み、前記コンデンサの充電電圧が所定の閾値(Vth)未満となった場合に作動し、前記抵抗部の全体的な抵抗値を変化させることによって前記コンデンサの静電容量と前記抵抗部の抵抗値とによって規定される放電時定数を変更する時定数変更部(33a)を備える構成とした。

(もっと読む)

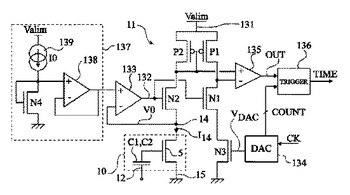

時間測定のための電荷保持要素を読み取る回路

【解決手段】本発明は、その誘電体がリークを示す少なくとも1つの容量性素子(C1,C2) と、残留電荷を読み取るための絶縁された制御ターミナル(5) を含むトランジスタとを備えたタイプの時間測定のための電荷保持電子要素(10)を読み取るための方法及び回路に関し、前記読み取り回路は、第1タイプの少なくとも1つのトランジスタ(P1,P2) と、第2タイプの1つのトランジスタ(N3,5)とを夫々含む、2つの供給ターミナル間の2つの平行な分岐を備えており、前記分岐の一方の第2タイプのトランジスタは、読み取られるべき前記要素のトランジスタから構成されており、前記分岐の他方の第2タイプのトランジスタは、該トランジスタの制御ターミナルでステップ信号(VDAC)を受けており、第1タイプのトランジスタの夫々のドレインは、比較器(135) の夫々の入力に接続されており、比較器の出力(OUT) が、電荷保持要素における残留電圧の表示を与える。  (もっと読む)

(もっと読む)

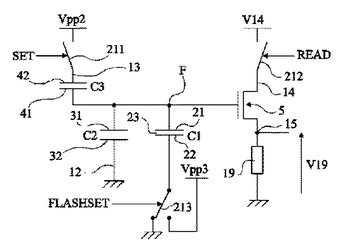

時間測定のための電荷保持回路のプログラミング

【解決手段】本発明は、その誘電体がリークを有する少なくとも1つの第1容量性素子(C1)と、その誘電体が第1容量性素子のキャパシタンスより大きいキャパシタンスを有する少なくとも1つの第2容量性素子(C2)とを備えた時間測定のための電荷保持電子回路であり、前記2つの素子は、残留電荷を測定するために、素子(5) に接続可能なフローティングノード(F) を構成する共通電極を有する前記電荷保持電子回路を制御する方法に関し、電荷保持期間が、第1容量性素子を介した充電又は放電によりプログラミング又は初期化される。  (もっと読む)

(もっと読む)

半導体装置

【課題】時間計測のための内部電池を持たずとも、経過時間を計測または経過時間に応じた処理の切り替えを行うことが可能な半導体装置を提供する。

【解決手段】例えば、抵抗素子31と相変化素子33とで抵抗分割回路を構成し、その分圧出力でトランジスタを制御し、このトランジスタの出力端子36を電源として内部回路014を動作させる。内部回路014は、例えば、高電圧動作回路015と低電圧動作回路016で構成する。そうすると、初期状態として相変化素子33がアモルファス状態(高抵抗状態)の場合、出力端子36からは高電圧が出力されるが、抵抗分割回路に所定の時間電流が流れることで相変化素子33が結晶状態(低抵抗状態)に遷移すると、出力端子36の出力が低電圧に移行する。これに伴い、初期状態で活性化していた高電圧動作回路015が、所定の時間経過後に不活性に切り替えられる。

(もっと読む)

クロックジッターの測定

本発明は、ジッターの影響を受けたクロック信号に基づく時間データを補正する技術を提供する。クロック信号17でのイベントの時間測定におけるジッターに起因する誤差は、イベント時点で、又は多数のイベントに亘る平均として、決定される。測定は、局部的なジッターに比較的影響されない、例えばキャパシタなどの長時間定常なデバイス19に関連する時間依存参照変数によりなされる。測定は、充電キャパシタ両端の電圧の読み込みであっても良い。測定値は期待値と比較され、時間誤差はこの結果に基づく。期待値は、キャパシタ19を有する装置1のメモリ6内のルックアップテーブル18から知られて、あるいはキャパシタの既知の充電率から計算されても良い。時間測定のジッターに起因する誤差は、キャパシタの測定値と期待値との間の電圧差にほぼ線形に比例する。この技術は、ノード内での局部的なジッターの変動により引き起こされる、ネットワーク内の2つのノード間でのフライト時間測定に対する誤差の如何なる寄与も除去する際に役立つ。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]