Fターム[2G132AL25]の内容

Fターム[2G132AL25]の下位に属するFターム

並列試験 (108)

Fターム[2G132AL25]に分類される特許

1 - 20 / 146

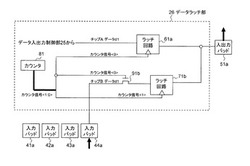

半導体装置およびその検査方法

【課題】ウエハ検査時に必要なプローブピンを削減可能にした半導体装置を提供する。

【解決手段】第1のデータを記憶する記憶素子と、データ読み出しの指示が入力されると、記憶素子から第1のデータを読み出して出力するデータ入出力制御部と、データ入出力制御部から出力される第1のデータを第1の端子に出力し、第1のデータを第1の端子に出力するとき、自装置の第2の端子と他の半導体装置の第1の端子とを接続するプローブカードを介して他の半導体装置から受信する第2のデータを保持し、その後、第2のデータを自装置の第1の端子に出力するデータラッチ部とを有する。

(もっと読む)

半導体試験装置、半導体試験方法及びプログラム

【課題】ウェハに含まれる半導体集積回路の電気的特性の測定には、測定対象となる全ての半導体集積回路が専用の測定回路を備えている必要があるが、全ての半導体集積回路に対して専用の測定回路を配設すると、半導体集積回路の面積が増加してしまう問題がある。そのため、半導体集積回路の面積を増加させることなく、半導体集積回路の電気的特性の測定を可能とする半導体試験装置が望まれる。

【解決手段】半導体試験装置は、第1の半導体集積回路と、電気的特性を測定するための測定回路及び測定端子と、前記測定回路に近接する第2の半導体集積回路と、を含むウェハの特性の測定を行う測定部と、第2の半導体集積回路に対して実施するウェハテストから得られる第1の電気的特性と、測定端子から測定した第2の半導体集積回路についての第2の電気的特性と、の相関に基づいて第1の半導体集積回路について第2の電気的特性を推定する制御部と、を備えている。

(もっと読む)

プローブカード、半導体ウェハの試験装置及び試験方法

【課題】簡単な構成で複数のチップに対して異なる試験を実施することはできるプローブカードを提供する。

【解決手段】本発明の一形態に係るプローブカードは、複数のチャネル11〜14から第1の試験を実行するための試験信号を伝送する第1の伝送路17が略集約され、半導体ウェハのチップ3に第1の試験を実行する第1の試験部21と、複数のチャネル11〜14から第2の試験を実行するための試験信号を伝送する第2の伝送路18が略集約され、半導体ウェハ3のチップ3aに第2の試験を実行する第2の試験部22と、を備える。

(もっと読む)

半導体ウェハ、プローブ装置、ウェハテスト装置及びウェハテスト方法

【課題】本発明は、同時測定を行うチップに関わる不要な干渉を最小限にする半導体ウェハ、当該半導体ウェハをテストするためのプローブ装置、プローブ装置ごとの相関を気にすることなく、治具の製作が可能となるウェハテスト装置及びウェハテスト方法を提供する。

【解決手段】本発明の半導体ウェハは、複数の半導体チップが形成されており、複数の半導体チップは、n個(nは2以上の整数)の半導体チップが360/n度ずつ回転して配置され、かつ上記n個の半導体チップそれぞれの間に1つ以上の半導体チップが挟まれて配置された配置パターンを基本単位とし、当該基本単位を複数繰り返すように配置されている。

(もっと読む)

半導体パッケージの検査方法及びそれに用いる検査装置

【課題】 被検体内の異なるデバイスを同時に検査可能な半導体パッケージの検査方法を提供する。

【解決手段】 テストプロセッサ112が第1制御信号および第2制御信号をそれぞれテスタ110内の第1パターン発生部114およびテストヘッド120内の第1パターン発生部124に伝送する(ST150)。第1パターン発生部114が第1パターンを第1半導体チップDに入力し(ST152)、第1判定部116が第1半導体チップDの不良可否を判断する(ST154)。一方、第2パターン発生部124が第2パターンを第2半導体チップFに入力し(ST162)、第2判定部126が第2半導体チップFの不良可否を判断する(ST164)。これにより、異なる第1半導体チップと第2半導体チップとを同時に検査できるようになり、異なる半導体チップを有する半導体パッケージを検査する時間を大幅に短縮することができる。

(もっと読む)

デバイステスタ

【課題】過去に取得したデータを含めて、再度のシュムーデータの取得なしに複数のDUTのシュムーデータの全体的傾向を把握することが容易なデバイステスタを提供。

【解決手段】本発明の構成は、被試験デバイス(DUT140)の電気的試験を行うデバイステスタ100であって、被試験デバイスのシュムーデータを取得するシュムー取得部220と、取得したシュムーデータをファイルに保存するデータ保存部222と、ファイルからシュムーデータを読み出すデータ読出部228と、取得したシュムーデータおよびファイルから読み出したシュムーデータから1または2以上のシュムーデータをユーザに選択させるデータ選択部226と、選択された1または2以上のシュムーデータ同士をプロット単位で論理計算し、計算された重畳シュムーデータを表示部212に表示する重畳表示部230と、を備えることを特徴とする。

(もっと読む)

スイッチ装置および試験装置

【課題】圧電素子を設けたアクチュエータの接点同士の凝着を防止するスイッチ装置を提供する。

【解決手段】スイッチ装置100は、第1接点122が設けられた接点部と、第1駆動電圧に応じて伸縮する第1圧電膜136、および第1圧電膜136と並行して設けられて第2駆動電圧に応じて伸縮する第2圧電膜138を有し、第1圧電膜136および第2圧電膜138の伸縮に伴い第2接点132を移動させて第1接点122と接触または離間させるアクチュエータと、第1駆動電圧および第2駆動電圧を制御する制御部200と、を備え、制御部200は、第1接点122および第2接点132を接触状態から切断状態へと切り替える場合に、第1駆動電圧を遮断すると共に、第2圧電膜138を伸ばす第2駆動電圧を第2圧電膜138に印加してアクチュエータの戻りを付勢する。

(もっと読む)

試験方法

【課題】簡易なテスタにより被試験デバイスの試験を行うことができる試験方法を提供することを課題とする。

【解決手段】各々が記憶回路を有する複数の被試験デバイス(211〜214)の試験方法であって、試験パタンが前記複数の被試験デバイスの記憶回路に分割されて記憶されており、前記複数の被試験デバイスの記憶回路から試験パタン(DT0〜DT3)を読み出して、前記読み出した複数の被試験デバイスの試験パタンを併合して前記複数の被試験デバイスに同じ試験パタン(PTN0〜PTN3)を供給する試験パタン読み出しステップと、前記供給された同じ試験パタンを用いて前記複数の被試験デバイスを同時に試験する試験ステップとを有する試験方法が提供される。

(もっと読む)

半導体デバイスのテスト装置、テストシステム、及びテスト方法

【課題】従来のマルチサイト・テストやコンカレント・テストにおける各種の問題点の少なくとも一部を解決し、テスト時間の短縮を図ること等ができる、テスト装置、テストシステム、及びテスト方法を提供すること。

【解決手段】第1IPコア4と第2IPコア5を集積して構成された第1半導体デバイス1と、第1IPコア4と第2IPコア5を集積して構成された第2半導体デバイス2とを、同時にテストするためのテスト装置20であって、ワークステーション21と、第1IPコア4をテストするための第1テスト回路22と、第1半導体デバイス1に電力を供給する第1電源回路23と、第2IPコア5をテストするための第2テスト回路24と、第2半導体デバイス2に電力を供給する第2電源回路25とを備える。

(もっと読む)

試験装置および試験装置の制御方法

【課題】複数の試験モジュールに対して効率的に制御命令を送信する。

【解決手段】複数の被試験デバイスを試験する試験装置であって、前記複数の被試験デバイスを試験する複数の試験部と、前記複数の試験部のそれぞれの有効化または無効化を選択する選択コマンドと、有効化された試験部を制御するための制御コマンドとを、ブロードキャストする試験制御部と、それぞれが前記複数の試験部のうち少なくとも1つの試験部を制御し、前記試験制御部からブロードキャストされた制御コマンドに対応する処理を、有効化された前記試験部に対して行う複数のサイト制御部と、を備える試験装置を提供する。

(もっと読む)

電圧を供給する装置

【課題】集積回路デバイスの内部の電源容量を大きくすることなく、電流供給能力を高くする。

【解決手段】集積回路デバイスと、駆動電圧を発生して集積回路デバイスに供給する電圧供給部と、を備え、集積回路デバイスは、複数の回路と、複数の回路のうち対応する回路を駆動するための駆動電圧を外部から受け取る複数の電圧入力端子と、外部から受け取る駆動電圧の基準となる基準電圧を出力する基準端子とを有し、電圧供給部は、基準電圧を電力増幅した駆動電圧を発生する、装置を提供する。

(もっと読む)

複数の被試験デバイスを試験する装置及び方法

TSVベースの3次元積層ICのためのテストアーキテクチャ

試験装置および試験モジュール

【課題】試験モジュールが有するリソースを有効に使用する。

【解決手段】少なくとも1つの被試験デバイスを試験する試験装置であって、被試験デバイスとの間で信号を伝送して当該被試験デバイスを試験する複数の試験部を有する試験モジュールと、前記複数の試験部を制御する複数の試験制御部と、を備え、前記試験モジュールは、前記複数の試験部のそれぞれが前記複数の試験制御部のうちいずれの試験制御部による制御を受けるかを、前記複数の試験部のそれぞれに対して独立に設定可能である、試験装置を提供する。

(もっと読む)

フラッシュメモリのデータ読み出し方法、半導体試験方法およびフラッシュメモリのデータ読み出し装置

【課題】ピンシェアード接続により接続された複数のフラッシュメモリからデータを読み出すときに、読み出し動作の高速化を図ることを目的とする。

【解決手段】ピンシェアード接続されたフラッシュメモリ1Aおよび1Bからデータを読み出すフラッシュメモリのデータ読み出し方法であって、フラッシュメモリ1A、1Bに設けられるセルアレイ102から読み出したデータをバッファ103に転送する転送動作と、バッファ103に格納されたデータを外部に出力する出力動作と、を有し、フラッシュメモリ1A、1Bのうち1つのフラッシュメモリの転送動作と他のフラッシュメモリの出力動作とをオーバラップさせている。

(もっと読む)

半導体集積回路のテスト方法及び半導体集積回路

【課題】複数のメモリマクロを備える半導体集積回路のメモリテストを短時間かつ適切に実行すること。

【解決手段】本発明の第1の態様にかかる半導体集積回路のテスト方法は、複数のメモリマクロを備える半導体集積回路のテスト方法であって、複数のメモリマクロの内、テストデータを同時に書き込む動作である同時書き込み動作をさせるメモリマクロの数よりも、書き込まれたテストデータを同時に読み出す動作である同時読み出し動作をさせるメモリマクロの数を少なく選択する。

(もっと読む)

半導体装置

【課題】一部のデータ入出力端子のみを用いて内蔵された複数の半導体チップを並列にテストすることのできる半導体装置を提供する。

【解決手段】複数の第1データ入出力端子と接続され、第1のテスト回路と、第1の記憶部とを有し、テスト動作時には、第1の記憶部から出力されるデータに応じて第1のテスト回路で第1のテスト結果を生成する第1の半導体チップと、複数の第2データ入出力端子と接続され、第2及び第3のテスト回路と、第2の記憶部とを有し、テスト動作時には、第2の記憶部から出力されるデータに応じて第2のテスト回路で第2のテスト結果を生成し、第2のテスト結果と第1の半導体チップの第1のテスト回路から供給される第1のテスト結果とに応じて第3のテスト回路で第3のテスト結果を生成し、第3のテスト結果を所定の第2データ入出力端子に出力する第2の半導体チップと、を備える。

(もっと読む)

半導体チップ調整装置及び前記装置を用いた検査方法

本発明は半導体チップ調整装置及び検査方法を提供する。前記装置は一又は複数の半導体チップ(C)を受け入れるチップ温度制御手段(TE1,TE2,TE3)と対応する数のチップ結合台(S)とマザーボード(30)とを備える。前記制御手段は、温度制御用流体が流されるように構成され且つ前面(VS)から後面(RS)へ至る対応する数のリセス(GA)を有する基体(G)を備える。前記チップ結合台(S)は、前記基体(G)に熱的接触状態で前記リセス(GA)に挿入され、前面(VS)にチップ受入領域(SM)を且つ内部に前記チップ受入領域(SM)内の前記半導体チップ(C)に対して電気信号を送受信する電気信号配線手段(D1,D2)を有している。前記マザーボード(30)は、前記チップ結合台(S)の配線手段(D1,D2)が前記マザーボード(30)における配線手段(32)に電気的に接続されるように前記後面(RS)に装着されている。 (もっと読む)

半導体試験回路、半導体試験用冶具、半導体試験装置及び半導体試験方法

【課題】多くのDUTを同時に試験可能な半導体試験回路を提供する。

【解決手段】信号処理部12が、テスタ20から信号線SLを介して入力された試験信号を複数のDUT30−1〜30−nに分配して供給するとともに、試験信号に基づいた複数のDUT30−1〜30−nからの応答信号を合成した試験結果を生成し、試験結果出力部13が、その試験結果を、入力された試験信号とは異なる電圧レベルにして、信号線SLを介してテスタ20に出力する。

(もっと読む)

半導体試験装置

【課題】半導体試験装置と被試験デバイスと接続関係を自由に設定しつつ、被試験デバイスに複数ピンが備えられている場合に全ての被試験デバイスにフェイルが生じているか否かを検出することを目的とする。

【解決手段】複数のDUT2から出力される出力信号に基づいてDUT2のパスフェイル情報を生成するPE部3を備えた半導体試験装置であって、DUT2に接続されるPE部3の複数のDUTピンとDUT2との対応関係を記憶した対応表に基づいて、DUTごとにパスフェイル情報をグループ化して出力する変換部11と、DUT2ごとにグループ化されたパスフェイル情報を入力して論理和の演算を行い、被試験デバイス情報として出力を行う複数の論理和演算部12と、複数の論理和演算部12から出力される全ての被試験デバイス情報に対して論理積の演算を行う論理積演算部14と、を備えている。

(もっと読む)

1 - 20 / 146

[ Back to top ]