Fターム[4M104DD85]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 固相反応 (1,946) | 固相エピタキシー (7)

Fターム[4M104DD85]に分類される特許

1 - 7 / 7

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

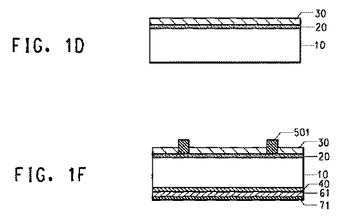

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

アルミニウムペーストおよびシリコン太陽電池の製造におけるその使用

粒子状アルミニウムと、亜鉛有機成分と、有機ビヒクルとを含むアルミニウムペースト、および、シリコン太陽電池のp型アルミニウム裏面電極の形成におけるその使用が開示される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 ゲート電極とドレイン領域間のリーク電流の増加を抑制する。

【解決手段】 半導体基板上にゲート酸化膜を介してゲート電極を形成する工程と、ゲート電極に第1の不純物を注入し、ゲート電極をマスクとして半導体基板に第1の不純物を注入する第1の不純物注入工程と、第1の不純物を活性化させる第1の熱処理を行う工程と、ゲート電極のゲート絶縁膜から離間させた位置に第2の不純物を注入する第2の不純物注入工程と、第2の不純物を含有する領域を活性化する形成する第2の熱処置を行う工程と、を含み、第1の不純物はリンからなる。

(もっと読む)

半導体デバイスの製造方法および該方法で得られた半導体デバイス

本発明は、基板(11)と、少なくとも一つの半導体素子(E)を設けた半導体本体(12)とを有し、単結晶シリコン(1)領域を具え、該単結晶シリコン領域(1)の上に金属シリサイド領域(3)を設け、そして金属シリサイド領域(3)の上に低結晶性シリコン領域(4)を設け、その後、低結晶性シリコン領域(4)を加熱することにより高結晶性を有するエピタキシャルシリコン領域(2)に変化させ、その処理の間に金属シリサイド領域(3)を低結晶性シリコン領域(4)の下部からエピタキシャルシリコン領域(2)の上へと移動させることにより、単結晶シリコン領域(1)の上にエピタキシャルシリコン領域(2)を形成する、半導体デバイス(10)の製造方法に関する。上記本発明によれば、金属シリサイド領域(3)より高い位置に、孔(6)を設けた絶縁層(5)を形成し、低結晶性シリコン領域(4)を孔(6)中および絶縁層(5)の上に析出させ、絶縁層(5)上の低結晶性シリコン領域(4)の一部(4A、4B)を平坦化処理により取り除き、その後にエピタキシャルシリコン領域(2)を形成する。この方法では、自己整合方式で金属シリサイドコンタクト(領域)が設けられており、そしてトランジスタのような半導体素子(E)の一部を形成できる、エピタキシャルシリコン領域(2)、好ましくはナノワイヤ(2)が簡単に得られる。  (もっと読む)

(もっと読む)

有機強誘電体メモリ及びその製造方法

【課題】 製造プロセスの容易化及び設計自由度の向上が実現できる、有機強誘電体メモリ及びその製造方法を提供することにある。

【解決手段】(a)基板100の上方に、ソース電極110、ドレイン電極112、有機半導体層114、ゲート絶縁層116及びゲート電極128を有する有機薄膜トランジスタ120を形成すること、(b)層間絶縁層122を貫通して有機薄膜トランジスタ120と電気的に接続する第1のコンタクト層124、及び層間絶縁層122を貫通して有機薄膜トランジスタ120と電気的に接続する第2のコンタクト層126を形成すること、(c)第1のコンタクト層124と電気的に接続する配線層130を形成すること、(d)第2のコンタクト層126と電気的に接続し、かつ下部電極142、有機強誘電体層144及び上部電極146を有する有機強誘電体キャパシタ140を形成すること、を含む。

(もっと読む)

エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法

【課題】 エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法が開示される。

【解決手段】 エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法において、第1単結晶シリコン膜上に前記第1単結晶シリコン膜の表面を部分的に露出させる開口部を有する第1絶縁膜パターンを形成した後、前記開口部によって露出された第1単結晶シリコン膜上に単結晶シリコンで構成された第1シード膜を形成する。そして、前記第1シード膜が形成された結果物上部にシリコンソースガスを提供して、前記第1シード膜上にエピタキシャル膜を成長させながら、前記第1絶縁膜パターン上に非晶質シリコン膜を形成する。その後、前記非晶質シリコン膜の結晶構造を単結晶に転換させて前記エピタキシャル膜と非晶質シリコン膜から第2単結晶シリコン膜を獲得する。

(もっと読む)

1 - 7 / 7

[ Back to top ]