Fターム[4M104DD91]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 基板へ不純物導入、拡散領域形成(析出後) (478)

Fターム[4M104DD91]の下位に属するFターム

電極(バリア層を含む)からの拡散 (55)

Fターム[4M104DD91]に分類される特許

421 - 423 / 423

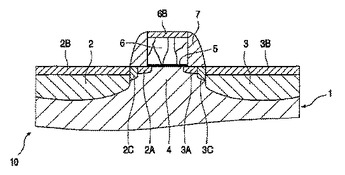

半導体装置とこの種の半導体装置の製造方法

この発明は、基板と半導体本体(1)とを有する半導体装置(10)に関し、半導体本体(1)がソース(2)及びドレイン(3)を有する第一のFET(3)を備え、ソース(2)及びドレイン(3)は、金属シリサイドを含む接続領域(2B,3B)が設けられ、そして、ゲート(6)下部のチャネル領域(4)と境界を成し且つソース(2)及びドレイン(3)より厚みが薄く且つドーピング濃度が低いソース及びドレイン領域拡張部(2A,3A)に接続されている。ソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)とは、第一の導電型で且つ厚み及びドーピング濃度がソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)との間の中間領域(2C,3C)により互いに接続されている。このようにして、接続領域(2B,3B)と基板と間にリーク電流並びに短絡が起きるのが抑制され、一方で、ソース及びドレイン領域拡張部(2A,3A)を用いることの効果が維持される。好ましくは、中間領域(2C,3C)がゲート(6)直近のスペーサ(7)下部に位置し、好ましくは、これらは、なるべく傾けられたイオン注入により形成される。  (もっと読む)

(もっと読む)

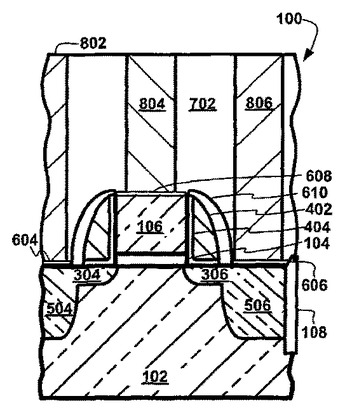

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

421 - 423 / 423

[ Back to top ]