Fターム[4M106AD05]の内容

半導体等の試験・測定 (39,904) | パッド(電極) (883) | 保護膜 (10)

Fターム[4M106AD05]に分類される特許

1 - 10 / 10

半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】1つの実施形態は、例えば、検査工程における検査用パッドへのコンタクトを容易化することに適した半導体装置、及び半導体装置の製造方法を提供する。

【解決手段】1つの実施形態によれば、半導体装置は、表面に垂直な方向から見た場合にチップエリアを内側に含む半導体基板と、前記チップエリアを保護するように、前記表面上における前記チップエリアの周囲に配されたエッジシールと、前記表面上における縁部に配された複数のパッド片と、前記表面上における前記チップエリアに対して第1の方向の少なくとも片側と第2の方向の少なくとも片側とのそれぞれにおいて、前記パッド片における前記エッジシールの側の縁部を覆う絶縁膜パターンとを備える。

(もっと読む)

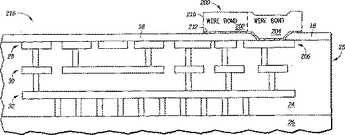

ボンディングパッドを有する半導体装置及びその形成方法

【課題】信頼性の高い集積回路を提供する。

【解決手段】集積回路20は、基板26を覆うパッシベーション層18及び前記基板26を覆うボンディングパッド200を備え、該ボンディングパッド200は、第1ボンディングワイヤを当該集積回路20に接続するための第1ワイヤボンディング領域202と第2ボンディングワイヤを当該集積回路に接続するための第2ワイヤボンディング領域204とを含み、前記第1ワイヤボンディング領域202の少なくとも非周辺部分が前記パッシベーションの上に位置し、前記ボンディングパッド200の下方にあるパッシベーション層が複数の開口を有し、前記基板26は配線領域を有し、該配線領域の少なくとも一部は前記パッシベーションの上に位置する前記ボンディングパッド200の一部の下に存在し、かつ前記配線領域の部分が前記複数の開口を介して前記ボンディングパッド200に結合する。

(もっと読む)

半導体装置及びその製造方法

【課題】パッド電極の直下でのクラックの発生を抑制できるようにした半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成されたLOCOS膜3と、LOCOS膜3上に形成されたポリシリコン膜5と、LOCOS膜3上に形成されたILD膜7と、ILD膜7に形成され、ポリシリコン膜5を底面とする第1の開口部と、第1の開口部内に形成され、ポリシリコン膜5と接するパッド電極9と、を有する。ポリシリコン膜5は、ILD膜7よりも強度があり、衝撃に対する耐性が高いため、プローブ検査の際にクラックの発生を抑制することができる。

(もっと読む)

半導体集積回路装置およびその検査方法、半導体ウエハ、およびバーンイン検査装置

【課題】正常なバーンイン検査を行うとともに、検査時の無駄な電力を削減できる検査方法、およびこれに用いられる半導体集積回路を提供する。

【解決手段】ウエハに対しウエハ試験を行ない、ウエハ試験後、良品には端子以外のチップ表面に保護膜を付加する。不良品には、端子も含むチップ表面全体に保護膜を付加し、その状態でバーンイン検査を行い、バーンイン投入前に判明した不良品チップへの電源供給、信号印加を遮断する。また、チップの良品判定を行うために自己検査回路を内蔵し、不良チップと判定された場合は、チップ内部動作を停止する機能をチップ内部に設けたり、あるいは、判定信号をバーイン検査装置に送信し、バーンイン検査装置から電源供給、信号印加を停止することでバーンイン投入後に判明した不良チップへの電源供給、信号印加を遮断できる。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体装置の検査方法

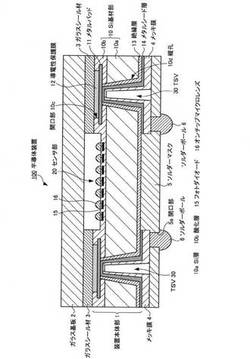

【課題】保護部材を形成した後でも半導体基板に形成された貫通配線の導通を確認することができる半導体装置、半導体装置の製造方法、及び半導体装置の検査方法を提供する。

【解決手段】受光部105が形成された受光部形成面に、受光部105と電気的に接続されてなく、少なくとも2つの互いに電気的に接続された電極108を有する半導体基板120と、電極108と電気的に接続されており、前記受光部形成面と前記受光部形成面とは反対側の面を貫通する貫通配線113と、前記受光部形成面に接続部を介して設けられた光透過性の保護部材101と、を有する半導体装置である。

(もっと読む)

パッドと半導体装置の製造方法

【課題】パッドと半導体装置の製造方法において、パッドの配置密度を向上させると共に、電気的試験で使用されるプローブによってパシベーション膜が欠損するのを防止する手段の提供。

【解決手段】開口面以外がパシベーション膜40、41で覆われたパッド37bにおいて、半導体装置に設けられた三角形状又は台形状の第1の金属膜37xと、第1の金属膜37x上であって、パッド37bの開口面の一部分に開口41aの側面と接するように形成された第2の金属膜37yとを備えたパッドとする。

(もっと読む)

半導体装置及びその製造方法

【課題】小型化が可能で、かつ、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、複数の電極14を有する半導体基板10と、複数の電極14に電気的に接続された複数のテストパッド20と、いずれかのテストパッド20と電気的に接続されたランド30と、ランドに設けられた外部端子40と、を有する半導体モジュール100を用意する工程と、テストパッド20にプローブ35を接触させて、電気特性を検査する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

絶縁膜(1)上に複数個のパッド(2)等を形成した後、全面にパッシベーション膜(3)を形成し、パッシベーション膜(3)に、全てのパッド(2)を露出する開口部(3a)を形成する。次に、全面に他のパッシベーション膜を形成し、このパッシベーション膜に、パッド(2)の中央部を露出する開口部をパッド(2)毎に形成する。このような方法によれば、パッシベーション膜(3)に開口部(3a)が形成された状態でプロービング試験を行うことが可能である。この状態でプロービング試験を行うと、パッド(2)の全面が露出しているため、プローブがパッド(2)に接触する確率が高くなり、正確な試験を行うことができる。従って、プローブにより高い精度を要することなく、パッドをより微細化したり、ピッチを狭めたりすることが可能となる。  (もっと読む)

(もっと読む)

ボンディングパッドを有する半導体装置及びその形成方法

ボンディングパッド(200)は第1ワイヤボンディング領域(202)と、第2ワイヤボンディング領域(204)と、を含む。一実施形態では、第1ワイヤボンディング領域(202)がパッシベーション(18)を覆って延びる。別の実施形態では、ボンディングパッドはプローブ領域、第1ワイヤボンディング領域、及び第2ワイヤボンディング領域を有する。一実施形態では、プローブ領域及びワイヤボンディング領域がパッシベーション(18)を覆って延びる。ボンディングパッドはどのような数のワイヤボンディング領域及びプローブ領域も有することができ、かつこれらの領域をどのような構成として有することもできる。ボンディングパッドが複数のワイヤボンディング領域を含むことができるので、マルチチップパッケージにおける場合のように単一のボンディングパッドへの複数のワイヤ接続を行なうことができる。ボンディングパッドがパッシベーションを覆って延びる形でパッドを設けることができるので、集積回路チップ面積を小さくすることもできる。  (もっと読む)

(もっと読む)

1 - 10 / 10

[ Back to top ]