Fターム[4M118DD06]の内容

Fターム[4M118DD06]の下位に属するFターム

Fターム[4M118DD06]に分類される特許

1 - 20 / 20

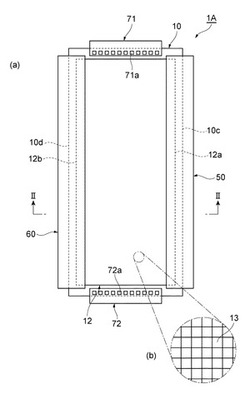

固体撮像装置

【課題】TDI動作によって撮像を行う際に、撮像に要する時間を短くすることができる固体撮像装置を提供する。

【解決手段】固体撮像装置1Aは、M×N個(M,Nは2以上の整数)の画素がM行N列に2次元配列されて成る撮像面12、撮像面12に対して列方向の一端側に各列毎に配置されたN個の信号読出回路20、及び、撮像面に対して列方向の他端側に各列毎に配置されたN個の信号読出回路30を有するCCD型の固体撮像素子10と、信号読出回路20から各列毎に出力される電気信号をディジタル変換したのちシリアル信号として順次出力する半導体素子50と、信号読出回路30から各列毎に出力される電気信号をディジタル変換したのちシリアル信号として順次出力する半導体素子60とを備える。

(もっと読む)

固体撮像素子及び固体撮像素子の製造方法

【課題】 ソースフォロアトランジスタの寄生容量を効果的に低減して感度を向上した固体撮像素子と、その製造方法を提供する。

【解決手段】 固体撮像素子は、光電変換によって生じた電荷が蓄積される浮遊拡散領域と、浮遊拡散領域と電気的に接続する増幅ゲート電極81を有し当該増幅ゲート電極81に印加される電位を増幅した出力信号を生成するソースフォロアトランジスタ8と、を備える。増幅ゲート電極81は、ソースフォロアトランジスタ8の活性領域82から延出する延出部分81aの少なくとも一部の膜厚が、ソースフォロアトランジスタ8に隣接する他のトランジスタ6,7のゲート電極61,71の膜厚よりも薄い。

(もっと読む)

単位画素及び固体撮像装置並びに単位画素の信号加算方法

【課題】光電変換素子が発生した光電子を4方向に振り分けて読み出すことができるとともに、リセットノイズを正確に除去することができる単位画素及び固体撮像装置並びに単位画素の信号加算方法を提供する。

【解決手段】光を検知して光電子に変換する光電変換素子を有する受光装置を備える単位画素であって、前記受光装置は、前記光電変換素子に発生した前記光電子を転送するための第1転送部と、前記光電変換素子により発生した前記光電子を一時的に保持する光電子保持部と、前記光電子保持部が保持した前記光電子を転送するための第2転送部と、転送された前記光電子を保持して該転送された前記光電子を電圧に変換させるための浮遊拡散層とを含む複数の光電子振分部を有し、前記単位画素は、前記浮遊拡散層の電位を基準電位にリセットするためのリセット用トランジスタと、前記光電変換素子に発生した前記光電子を排出する光電子排出部とを備える。

(もっと読む)

半導体装置及びその製造方法、固体撮像装置及びその製造方法、並びに電子情報機器

【課題】金属部品等による乱反射による画質低下もなく、また撮像素子が透明樹脂で完全に被われ、外部との接続端子部及び素子撮像エリア直上部を除いて、防湿材料により被われていることで、撮像素子チップに水分が浸入することも全くない、非常に高い信頼性の固体撮像装置を得る。

【解決手段】マイクロレンズを有する撮像素子チップ32と、該撮像素子チップに接続されたリード端子33と、該固体撮像チップを該リード端子とともに封止するクリアモールドパッケージ31とを備え、該リード端子の一部を外部リードとして該クリアモールドパッケージの外部に露出させた固体撮像装置30において、該クリアモールドパッケージを、その表面の、該撮像素子チップ32の撮像領域35に対向する透光領域を除いて、該クリアモールドパッケージの表面を遮光性材料36により被覆した構造とした。

(もっと読む)

固体撮像装置

【課題】水平間転送をスムーズに行った場合でも、他の特性が劣化してしまうのを抑制する。

【解決手段】固体撮像装置100は、画素部110に行列状に配置された複数の光電変換部120と、複数の光電変換部120の列に対応して設けられ、対応する複数の光電変換部120から読み出した複数の信号電荷を列方向に転送する複数の垂直転送部130と、複数の垂直転送部130によって転送された信号電荷を行方向に転送する、並列に配置された第1の水平転送部140a及び第2の水平転送部140bと、第1の水平転送部140a及び第2の水平転送部140bの出力端に隣接する領域のそれぞれに形成された複数のフローティングディフュージョン部を含み、転送された信号電荷を電気信号として出力する第1の出力部160a及び第2の出力部160bとを備え、複数のフローティングディフュージョン部は、隣接する水平転送部間の間隔より広い間隔で配置されている。

(もっと読む)

MOS型イメージセンサ、MOS型イメージセンサの駆動方法、撮像装置、撮像方法

【課題】広ダイナミックレンジ撮像が可能で低ノイズかつ安価なイメージセンサを提供する。

【解決手段】光電変換部PDとフローティングゲートFGを含む書き込みトランジスタWT及び読み出しトランジスタRTとを含む画素部21と、各画素部21のPD電荷のリセットの終了よりも前に、各画素部21のFG電荷を同時に消去し、リセットの終了直後にPDに存在する電荷をFGに蓄積し、蓄積電荷に応じた暗時信号を読み出し、FGへの電荷蓄積後に開始される第一露光期間中にPDに蓄積される電荷をFGに蓄積し、蓄積電荷に応じた第一信号を読み出し、第一露光期間の後に開始される第二露光期間中にPDに蓄積される電荷をFGに蓄積し、蓄積電荷に応じた第二信号を読み出す駆動回路3と、デジタル変換後の暗時信号を記憶するメモリ8と、デジタル変換後の第一信号及び第二信号の各々と暗時信号との差分を求めて出力するノイズ除去回路6とを備える。

(もっと読む)

MOS型イメージセンサ及び撮像装置

【課題】駆動電圧を低減することが可能なMOS型イメージセンサを提供する。

【解決手段】複数の画素部21を有するMOS型イメージセンサ100であって、画素部21は、入射光に応じた電荷を発生し蓄積する光電変換部PDと、書き込みトランジスタWT及び読み出しトランジスタRTと、素子分離領域211とを含み、書き込みトランジスタWTは、フローティングゲートFGを有し、光電変換部PDに蓄積された電荷をフローティングゲートFGに蓄積するものであり、かつ、光電変換部PDに接続されたソースと書き込みコントロールゲートWCGの2端子構造となっており、書き込みコントロールゲートWCGがフローティングゲートFGの側面に対向する位置で、かつ、素子分離領域211上方に少なくとも配置されている。

(もっと読む)

MOS型イメージセンサ、MOS型イメージセンサの駆動方法、撮像装置

【課題】グローバルシャッタ機能を有する高画質撮像かつ高感度撮像が可能なMOS型イメージセンサを提供する。

【解決手段】複数の画素部21を有するMOS型イメージセンサ100であって、画素部21は、シリコン基板210内に形成された光電変換部PDと、シリコン基板210の表面に形成されたトランジスタであって、該表面上方に絶縁膜219を介して設けられ光電変換部PDに蓄積される電荷を蓄積するフローティングゲートFGを含む書き込みトランジスタWT及び読み出しトランジスタRTとを含み、光電変換部PDは、シリコン基板210の表面とは反対面の裏面から入射してきた光を受光して、この光に応じた電荷を発生して蓄積するものであり、書き込みトランジスタWTの電荷注入領域の少なくとも一部が、平面視において、光電変換部PDと重なる位置に設けられている。

(もっと読む)

固体撮像素子及び撮像装置

【課題】暗いシーンを撮像したときに固体撮像素子の半導体基板に形成したアンプ等で発光する赤外光の影響を抑制する。

【解決手段】赤外光カットフィルタを透過した可視光の受光量に応じた被写体画像信号を検出する画素部56と該被写体画像信号を増幅するアンプ58とが半導体基板51の表面部に形成された固体撮像素子100であって、半導体基板51のアンプ58が形成された直下近傍位置にだけ該アンプ58で発光され半導体基板51内を進む赤外光の画素部56方向への侵入を阻止する赤外光抑制層61を設ける。

(もっと読む)

撮像素子の撮像素子の製造方法

【課題】電荷検出感度を安定させることができる撮像素子及び撮像素子の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11上に形成されたゲート絶縁膜12と、半導体基板11の表面に形成され、ゲート絶縁膜12に形成されたコンタクトホールから露呈するフローティングディフュージョンFDと、ゲート絶縁膜12上に形成され、フローティングディフュージョンFDとコンタクトする配線層とを備え、配線層が不純物濃度の異なる複数の電極材料膜とを有し、複数の電極材料膜のうち、最下層より上に積層されたいずれかの電極材料膜がフローティングディフュージョンFDに接している。

(もっと読む)

固体撮像装置及びその製造方法

【課題】感度の低下を防止しながら浮遊拡散層におけるノイズの発生を防止する固体撮像装置及びその製造方法を提供する。

【解決手段】固体撮像装置1のN型シリコン層103内には浮遊拡散層103bが形成されている。平坦化膜104上には誘電体材料からなる4本の柱状の支持体106が平面視において浮遊拡散層103bを囲むように立設されており、遮光膜107を支持している。遮光膜107は浮遊拡散層103bに外光が入射するのを防止する。遮光膜107と浮遊拡散層103bとの間は中空になっており、浮遊容量の発生が抑えられる。

(もっと読む)

出力2分岐型固体撮像素子

【課題】撮像したカラー画像に2つの出力アンプのゲイン差が表れることのない出力2分岐型固体撮像素子を提供する。

【解決手段】第1色光,第2色光,第3色光の夫々の受光量に応じた信号電荷を蓄積する複数の光電変換素子と、電荷転送路103と、電荷転送路103に設けた分岐部120と、分岐部120から分岐され前記第1色光,第3色光に応じた信号電荷を転送する第1分岐転送路105と、分岐転送路105より転送段数が1段分多く第2色光に応じた信号電荷を転送する第2分岐転送路104と、各分岐転送路の出力端部に設けられ転送されてきた信号電荷の電荷量に応じた電圧値信号を同時に出力する第1及び第2のアンプとを備える。

(もっと読む)

電荷転送装置及び固体撮像装置

【課題】LH電極からHOG電極への転送の改善を図ると共にDレンジの改善をも図る。

【解決手段】撮像部と、撮像部より転送された信号電荷を転送する水平転送レジスタ4と、水平転送レジスタの最終段から出力ゲートを介して転送された信号電荷を検出する電荷検出部とを備えるCCD固体撮像装置において、水平転送レジスタの最終段に電圧を印加する電極が第1の電極14aと第2の電極14bに2分割され、第1の電極に接地電位を印加すると共に、第2の電極に転送クロックを印加する。

(もっと読む)

電荷転送素子

【課題】リセットノイズを発生させることなく、高S/Nで電圧変換効率の良好な電荷−電圧変換器を有する電荷転送素子を提供することを目的とする。

【解決手段】電荷−電圧変換部における接合トランジスタのゲート電極領域を、電位障壁を発生させず、緩やかな電位勾配が形成される構造にすることにより、リセットノイズを発生させることなく高いS/Nを実現でき、電圧変換効率の良好な電荷−電圧変換器を容易に実現できる。

(もっと読む)

半導体装置およびその製造方法

【課題】アスペクト比の高いコンタクトホールの形成されたコンタクト部においても、断線を防止し、信頼性の高い固体撮像素子を提供する。

【解決手段】基板表面に形成された不純物領域と、電極配線とを電気的に接続するコンタクト部とを備えた半導体装置であって、前記電極配線の端部を含み前記不純物領域に開口するように形成されたコンタクトホールと、前記コンタクトホール内で、前記電極配線と前記不純物領域とを電気的に接続するシリコン系導電性膜からなる下地配線と、前記下地配線の上層に形成され、前記コンタクトホール内で少なくとも前記下地配線に接続された金属配線層と備えている。

(もっと読む)

電荷転送装置

【課題】 CCDイメージセンサの水平シフトレジスタの出力端のチャネル幅を狭める部分にて転送効率が低下し得る。

【解決手段】 出力端部34においてチャネル幅を絞り込む角度を後段ほど小さくなるように、各ストレージ部30-k及び各バリア部32-kの寸法、形状を定める。第(k−1)段と第k段との水平位置の差(Lsk+Lbk)に対するチャネル幅の差(Wk−1−Wk)の比が後段に行くほど小さくなるように設定する。

(もっと読む)

固体撮像装置

【課題】 信号電荷の転送効率及び検出感度が高い低電圧駆動の固体撮像装置を提供する。

【解決手段】 信号電荷を転送する第1電荷転送部102と、第1電荷転送部102の側部と接し、第1電荷転送部102に信号電荷を入力する信号入力部101と、第1電荷転送部102の端部の幅方向における中央部と接し、第1電荷転送部102のチャンネル幅よりも狭い幅を有し、第1電荷転送部102により転送された信号電荷を電圧に変換する電荷検出部103とを備え、第1電荷転送部102は、電荷検出部103と接する部分と、第1電荷転送部102の幅方向の中央を境にした信号入力部101と接する部分とにおいて、第1電荷転送部102のチャンネル幅よりも狭いチャンネル幅の第2電荷転送部104を有する。

(もっと読む)

電荷結合装置及び固体撮像装置

【課題】 CCDシフトレジスタの出力端において、出力ゲート電極(OG)と最終段転送電極との容量結合によりOGの電位が転送クロックに応じて変動する結果、出力信号にノイズが生じやすい。

【解決手段】 最終段転送電極56-2及びOG76それぞれのチャネル領域60に応じた位置に水平方向へ突き出た凸部を形成し、この部分のみにて両電極間のオーバーラップを生じさせる。凸部が設けられた箇所以外ではOG76と転送電極56-2との間には間隙が形成される。特にOG76、転送電極56-2をそれぞれ配線78,54に向けて比較的長く引き延ばした部分において、両電極は互いに重ならない。このようにして両電極間の容量結合を緩和する。

(もっと読む)

固体撮像装置

【課題】1段目の駆動MOSトランジスタとしてエンハンスメントMOSトランジスタを用いた構成を採ると、エンハンスメントMOSトランジスタが表面チャネルを利用したトランジスタであり、トランジスタサイズも小さいことから、1段目の駆動MOSトランジスタが1/fノイズの支配的な回路構成となってしまう。

【解決手段】CCD固体撮像装置の出力回路17において、当該出力回路17を2段ソースフォロア回路構成とし、1段目の駆動MOSトランジスタ21としてデプレッションMOSトランジスタを用い、2段目の駆動MOSトランジスタ22としてエンハンスメントMOSトランジスタを用いるようにする。

(もっと読む)

固体撮像装置およびその駆動方法

【課題】 信号読み出しを列毎に制御して信号加算が可能な2層ゲート構造を有する。

【解決手段】 転送時間差発生領域は、2層目の垂直ゲート電極27c,27eと1層目の垂直ゲート電極27d,27fとで構成し、A列の垂直ゲート電極27c,27fの直下にチャネルバリア29a,29bを形成している。そして、B列の垂直レジスタ24のみから水平レジスタ25に信号電荷を転送する場合には、駆動パルスΦV7を「H」にして、A列の垂直ゲート電極27f直下のポテンシャルを蓄積電荷が転送されないポテンシャルに維持させる。一方、A列から信号電荷を転送してB列からの信号電荷と混合する場合には、駆動パルスΦV7のレベルを「HH」にして、A列の垂直ゲート電極27f直下のポテンシャルを蓄積電荷が転送可能なポテンシャルまで低下させる。

(もっと読む)

1 - 20 / 20

[ Back to top ]