Fターム[4M119EE28]の内容

MRAM・スピンメモリ技術 (17,699) | 配線構成 (2,374) | ワード線(WL) (935) | WLが1セル、ユニットに複数本有するもの (300)

Fターム[4M119EE28]の下位に属するFターム

書込WLと読出WLを別に持つもの (217)

WLの分岐(バイパス線、裏打ち線) (7)

Fターム[4M119EE28]に分類される特許

1 - 20 / 76

磁気抵抗素子及び磁気メモリ

【課題】大きな電流で書込みを行うことができるとともに、高速動作を行うことができる磁気抵抗素子および磁気メモリを提供することを可能にする。

【解決手段】本実施形態の磁気抵抗素子は、スピン注入書込みによって磁化方向が可変の第1磁性層と、磁化方向が固定された第2磁性層と、前記第1磁性層と前記第2磁性層との間に設けられた非磁性層とをそれぞれ有し並列に配置された第1および第2素子と、前記第1および第2素子のそれぞれの第1磁性層と対向するように配置されるとともに第1磁性層と静磁結合し磁化方向が可変の第3磁性層と、磁化方向が固定された第4磁性層と、前記第3磁性層と前記第4磁性層との間に設けられたトンネル障壁層とを有するTMR素子と、を備え、前記第1および第2素子の第1および第2磁性層は膜面に垂直な磁化を有し、前記TMR素子の前記第4磁性層は膜面に平行な磁化を有する。

(もっと読む)

半導体記憶装置

【課題】MTJ素子にデータを書き込むために充分に大きな電流を駆動することができるセルトランジスタを備え、かつ、容易に製造可能なメモリを提供する。

【解決手段】本実施形態によるメモリはアクティブエリアを備え、セルトランジスタはアクティブエリアに形成されている。MTJ素子の一端がセルトランジスタのソース/ドレインの一方に電気的に接続されている。第1のビット線は、セルトランジスタのソース/ドレインの他方に電気的に接続されている。第2のビット線は、MTJ素子の他端に電気的に接続されている。ワード線は、セルトランジスタのゲートに電気的に接続され、あるいは、セルトランジスタのゲートとして機能する。1つの第1のビット線に対して複数の第2のビット線が対応している。MTJ素子が同一のワード線および同一のアクティブエリアを共有している。アクティブエリアは、第1および第2のビット線の延伸方向に連続して形成されている。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

抵抗変化型メモリ

【課題】メモリの動作マージンを向上する。

【解決手段】本実施形態の抵抗変化型メモリは、ビット線BLA,BLC間に接続された第1のセルSCAとビット線BLB,BLC間に接続された第2のセルSCBとを含むメモリセルMCと、第1のセルSCAを形成するメモリ素子8A及び選択トランジスタTrAと、第2のセルSCBを形成するメモリ素子8B及び選択トランジスタTrBとを具備し、メモリセルに対する書き込み動作時、ワード線が活性化されている期間において、メモリセルMC内の2つのメモリ素子8A,8Bを第1の抵抗状態に変化させた後、2つのメモリ素子8A,8Bのうち一方のメモリ素子を第2の抵抗状態に変化させる。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気メモリにおいて、安定的且つ容易に磁壁を導入可能な構造とする。

【解決手段】磁気メモリは、磁気記録層10と、非磁性層11を介して磁気記録層10に接続された参照層12と、磁気記録層10より下方に設置された第1、2磁化固定層19、20とを具備する。磁気記録層10及び参照層11は垂直磁気異方性を有する。磁気記録層10は、反転可能な磁化を有し参照層11と重なる磁化反転領域2と、磁化反転領域2の第1境界に接続され、磁化の向きが第1方向に固定された第1磁化固定領域1と、磁化反転領域2の第2境界に接続され、磁化の向きが第1方向と反平行な第2方向に固定された第2磁化固定領域3とを備える。第1、2磁化固定層19、20は、第1、2磁化固定領域1、3の磁化を固定する。第2磁化固定層20が、第1磁化固定層19と比較して保磁力が低い。

(もっと読む)

半導体装置

【課題】メモリセルの平面視における面積を増加せずに、磁気抵抗素子の情報の読み書きに用いる電流値を低減しながら、読み書きエラーや磁気抵抗素子間の短絡が抑制された集積回路を有する半導体装置を提供する。

【解決手段】半導体基板の主表面上に配置された、電流の流れる向きに応じて磁化状態を変化させることが可能な、スピントルク書き込み方式の面内磁化型の磁気抵抗素子MRDと、磁気抵抗素子MRDと電気的に接続され、主表面に沿った方向に向けて延びる第1配線BLとを備える。上記磁気抵抗素子MRDは平面視におけるアスペクト比が1以外の値である。上記磁気抵抗素子MRDとスイッチング素子とが電気的に接続されたメモリセルMCが複数並んだメモリセル領域において、平面視における磁気抵抗素子MRDの長手方向に関して、隣接する複数の磁気抵抗素子MRDが、上記長手方向に沿って延在する同一直線上に乗らないように配置される。

(もっと読む)

半導体記憶装置

【課題】上部電極と第2のビット線との間のビアコンタクトの劣化を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に配置された複数の磁気トンネル接合素子と、複数の磁気トンネル接合素子の一端に電気的に接続された複数の選択トランジスタとを備える。第1のビット線が、各磁気トンネル接合素子の一端に1つまたは複数の選択トランジスタを介して接続されている。複数の上部電極は、複数の磁気トンネル接合素子の他端に接続されえいる。第2のビット線は、各磁気トンネル接合素子の他端に上部電極を介して接続されている。上部電極は、第2のビット線に沿って延伸しており第2のビット線の延伸方向に配列された複数の磁気トンネル接合素子の各他端に共通に接続されている。

(もっと読む)

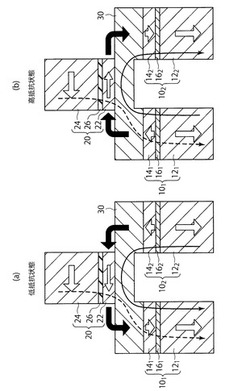

スピントロニクス装置及び論理演算素子

【課題】 電流−スピン流変換効率が高く、高強度のスピン流が得られるスピントロニクス装置を提供する。

【解決手段】 互いに平行に対向する第1端面及び第2端面を有し、電子と正孔とが同程度のキャリア密度と移動度を有し、正常及び異常ホール係数が共にゼロである強磁性の両極性伝導金属からなるスピン流生成領域30と、第1端面にオーミック接続し、電子をスピン流生成領域30に注入する第1主電極20と、第2端面にオーミック接続し、正孔をスピン流生成領域30に注入する第2主電極40とを備える。第1端面に垂直な面に直交する方向の外部磁場にもとづく正常ホール効果に、磁場誘起磁化もしくは自発磁化にもとづく異常ホール効果が加わることによって、電子と正孔とを同一方向に輸送されるように偏向して、電子と正孔の電荷を互いに相殺し、スピン流生成領域30における異常ホール効果によってスピン流を得る。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】一端がビット線に接続された磁気抵抗素子と、一端が磁気抵抗素子の他端に接続され、ゲートが読み出し用ワード線に接続され、他端が接地に接続された選択トランジスタとで構成されたメモリセルよりなるスピン注入方式の磁気ランダムアクセスメモリであって、従来と同等の書き込み電流値を確保し、書き込みマージンと読み出しマージンの両方を確保できる磁気ランダムアクセスメモリを提供する。

【解決手段】磁気抵抗素子は個別の磁気抵抗素子を複数直列に接続されてなり、個別の磁気抵抗素子の両端部に、それぞれNチャンネルトランジスタおよびPチャンネルトランジスタがドレインで接続され、Nチャンネルトランジスタのゲートに書き込み用ワード線が接続されソースに接地電圧が接続され、Pチャンネルトランジスタのゲートに反転書き込み用ワード線が接続されソースに電源電圧が接続された構成であることを特徴とする。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

磁気抵抗効果素子、磁気抵抗効果ヘッド、磁気記憶装置、および磁気メモリ

【課題】スピントランスファートルクに起因するノイズの低減を図った磁気抵抗効果素子

、磁気抵抗効果ヘッド、磁気記憶装置、および磁気メモリを提供する。

【解決手段】磁化固着層、非磁性層、磁化自由層を有する磁気抵抗効果素子の磁化固着層

、または磁化自由層内にZr,Nb,Mo,Ru,Rh,Pd,Ag,La,Hf,Ta

,W,Re,Os,Ir,Pt,Auのいずれかを含む層を配置する。

(もっと読む)

抵抗変化型半導体メモリ

【課題】セル面積の縮小及び動作特性の向上に優れたレイアウトを提案する。

【解決手段】実施形態によれば、抵抗変化型半導体メモリは、第1方向に並ぶ第1乃至第4メモリセルを備える。第1乃至第4メモリセルの各々は、第1ソース/ドレインが第1方向に延びる第1ビット線BLA1に接続され、ゲートが第2方向に延びるワード線WL1, WL2, WL3, WL4に接続されるセルトランジスタT11, T12, T13, T14と、一端がセルトランジスタT11, T12, T13, T14の第2ソース/ドレインに接続され、他端が第2方向に延びる第2ビット線BLB1, BLB2, BLB3, BLB4に接続される抵抗性記憶素子M11, M12, M13, M14とを有する。第1及び第2メモリセル内の第1ソース/ドレインは、共有化され、第3及び第4メモリセル内の第1ソース/ドレインは、共有化される。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのトランジスタの配置効率が高い不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMでは、各メモリセルMCのアクセストランジスタを2つのトランジスタQA,QBに分割し、トランジスタQA,QBのゲートをそれぞれワード線WLA,WLBに接続し、奇数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLAに接続し、偶数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLBに接続する。したがって、メモリセルMCのトランジスタの配置効率を高めることができる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタの拡散層に電気的に接続されたコンタクトプラグと、コンタクトプラグ上に形成され、上面がスイッチングトランジスタの上面よりも高い位置にある上部コネクタと、上部コネクタの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

半導体記憶装置

【課題】 製造コストおよびプロセス歩留りの改善が可能となる、抵抗変化素子を含む半導体記憶装置を提供すること。

【解決手段】 第1の方向に並んで設けられた第1および第2のMOSFETと、前記第1および第2のMOSFETの上方に設けられ下端が前記第1および第2のMOSFETのドレインに接続された第1の抵抗変化素子と、第1の方向に並んで設けられた第3および第4のMOSFETと、前記第3および第4のMOSFETの上方に設けられ下端が前記第3および第4のMOSFETのドレインに接続された第2の抵抗変化素子と、前記第1および第2のMOSFETのソースに接続され第1の方向に延びる第1の配線と、前記第3および第4のMOSFETのソースに接続され第1の方向に延びる第2の配線と、前記第1の抵抗変化素子の上端と前記第2の抵抗変化素子の上端とを接続する上部電極と、前記上部電極に接続され第1の方向に延びる第3の配線とを備える。

(もっと読む)

磁気抵抗記憶素子及び磁気ランダムアクセスメモリ

【課題】書込み電流を低減しつつ、信頼性の高い磁気抵抗記憶素子を提供する。

【解決手段】磁気抵抗記憶素子は、読出し構造体と、読み出し構造体の近傍に設けられた書込み構造体とを具備する。読み出し構造体は、磁化方向が変化する第1のフリー層と、磁化方向が固定された磁化固定層と、第1のフリー層と磁化固定層との間に設けられたトンネル絶縁層とを備える。書込み構造体は、磁化方向が変化する第2のフリー層を備える。第2のフリー層は、第2のフリー層の膜の上面に設けられ、第1方向に磁化が固定された第1の磁化固定領域と、膜の下面に設けられ、第2方向に磁化方向が固定された第2の磁化固定領域とを含む。膜の膜面方向に磁壁が存在する。第1のフリー層と第2のフリー層とは静磁結合している。

(もっと読む)

減電圧の入出力デバイス(REDUCEDVOLTAGEINPUT/OUTPUTDEVICE)を有する抵抗ベースメモリ

減電圧のI/Oデバイスを含む抵抗ベースメモリが開示される。特定の一実施形態では、回路は、第1の抵抗メモリセルおよび第1の負荷トランジスタを含むデータ経路を含む。基準経路は、第2の抵抗メモリセルおよび第2の負荷トランジスタを含む。第1の負荷トランジスタおよび第2の負荷トランジスタは、回路内のコアトランジスタのコア供給電圧と同等の負荷供給電圧で動作するように構成された入出力(I/O)トランジスタである。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】MRAMのメモリセル面積を縮小化する。

【解決手段】メモリセル80は、四角柱形状の素子形成領域100にメモリトランジスタTR1乃至3とTMR素子TMR1が設けられた3T1J型の3次元構造のメモリセルである。メモリトランジスタTR1のゲート電極5aが素子形成領域100の側面のA面及びB面に形成される。メモリトランジスタTR2はメモリトランジスタTR1の上部に設けられ、ゲート電極5bが素子形成領域100の側面のB面及びC面に形成される。メモリトランジスタTR3はメモリトランジスタTR2の上部に設けられ、ゲート電極5cが素子形成領域100の側面のC面に形成される。TMR素子TMR1は素子形成領域100上部に設けられる。B面のゲート電極5a及びゲート電極5bによりチャネル形成領域CH1が形成され、C面のゲート電極5b及びゲート電極5cによりチャネル形成領域CH2が形成される。

(もっと読む)

1 - 20 / 76

[ Back to top ]