Fターム[4M119HH20]の内容

MRAM・スピンメモリ技術 (17,699) | 回路技術 (628) | その他の回路技術 (36)

Fターム[4M119HH20]に分類される特許

1 - 20 / 36

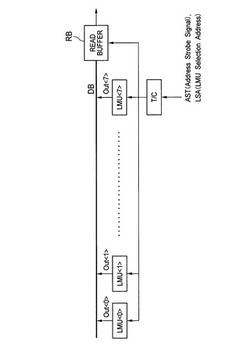

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

集積磁気薄膜増強回路素子を有する磁気抵抗ランダムアクセスメモリ(MRAM)

ルックアップテーブル回路およびフィールドプログラマブルゲートアレイ

【課題】動作速度の速いルックアップテーブル回路およびフィールドプログラマブルゲートアレイを提供する。

【解決手段】ルックアップテーブル回路1は、入力信号に基づいて複数の抵抗変化型素子の中から一つの抵抗変化型素子を選択する抵抗変化回路2と、抵抗変化回路2の最大抵抗値と最小抵抗値との間の抵抗値を有する参照回路4と、抵抗変化回路2の他端にソースが接続された第1のnチャネルMOSFET6と、参照回路の他端にソースが接続された第2のnチャネルMOSFET8と、第1のnチャネルMOSFET6のドレインを通して抵抗変化回路2に電流を供給する第1の電流供給回路10と、第2のnチャネルMOSFET8のドレインを通して参照回路4に電流を供給する第2の電流供給回路12と、第1のnチャネルMOSFET6のドレイン電位と第2のnチャネルMOSFET8のドレイン電位を比較する比較器14と、を備える。

(もっと読む)

磁気メモリ

【課題】磁気メモリの信頼性及び動作特性の向上を図る。

【解決手段】磁気メモリは、第1及び第2の磁性層の間に設けられた中間層とを有する磁気抵抗効果素子と、磁気抵抗効果素子に書き込まれた第1のデータが第1のデータが誤りを含むか否かを検出し、第1のデータが誤りを含む場合にその誤りが訂正された第2のデータを出力する誤り検出訂正回路と、第1のパルス幅Twp1を有する第1の書き込み電流Iw1及び第1のパルス幅Twp1より長い第2のパルス幅Twp2を有する第2の書き込み電流Iw2のいずれか一方を生成し、磁気抵抗効果素子に流す書き込み回路と、第2のデータを磁気抵抗効果素子に書き込む場合、第2の書き込み電流Iw2を磁気抵抗効果素子に流すように書き込み回路を制御する制御回路と、を備える。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

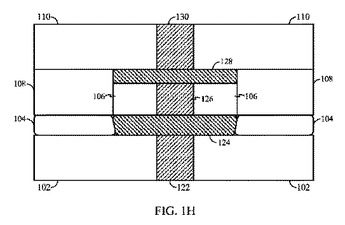

平坦化された電極上の磁気トンネル接合(MTJ)

直接接触を用いた磁気トンネル接合(MTJ)は、より低い抵抗、改善された生産量、及び、より単純な製造を有して製造される。より低い抵抗は、MTJの読み取り方法及び書き込み方法の両方を改善する。MTJ層(126)は、下部電極(124)上に堆積され、下部金属(122)に位置合わせされる。エッチング停止層(302)は、下部金属を囲う絶縁体のオーバーエッチングを防止するために下部金属に隣接して堆積され得る。下部電極は、実質的に平坦な表面を提供するためにMTJ層の堆積前に平坦化される。さらに、下層(202)は、MTJの所望の特性を促進するためにMTJ層の前に下部電極上に堆積され得る。  (もっと読む)

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】 ビットラインにプリチャージされる電圧をデータに応じて異なるようにし、プリチャージ動作を行なうことのできる半導体メモリ装置を提供すること。

【解決手段】本発明に係る半導体メモリ装置は、ソースラインおよびビットラインを介して流れる電流の方向に対応する極性のデータが保存される複数のメモリセル410と、前記データが複数の前記メモリセルに保存される前にプリチャージ信号PREに応答し、前記ビットラインを前記データに対応する電圧でプリチャージするプリチャージ駆動手段450とを備える。

(もっと読む)

不揮発性メモリセルの予測的予加熱

熱的前処理を用いてスピン注入磁化反転型ランダムアクセスメモリ(STRAM)メモリセルなどの不揮発性メモリセル(120)にデータを書込むための方法(180)および装置(106)。いくつかの実施形態では、論理状態は、第1のブロックアドレスと関連付けられる未処理不揮発性第1のメモリセルに書込まれる(184)。熱的前処理は、第1のブロックアドレス(186)選択に応答して選択される第2のブロックアドレスと関連付けられる不揮発性第2のメモリセルに同時に適用される(188)ため、記録ブロックアドレスは、不揮発性第1のメモリセルの書込動作に引続く書込動作で選択される可能性が比較的高いブロックのアドレスである。  (もっと読む)

(もっと読む)

半導体装置

【課題】内部回路の動作パラメータなどの設定を行うデータを長期にわたって安定に供給する。

【解決手段】第1の動作モード(PROM)時には、不揮発性メモリセルに対し非破壊的に書換え可能な態様でデータを書込み、第2の動作モード(OTP)時には不揮発性メモリセルに対し、破壊的に書換え不可能な態様でデータを書込む。この不揮発性メモリセルは、記憶素子として、可変磁気抵抗素子を有し、可変磁気抵抗素子の抵抗値に応じて情報を不揮発的に記憶する。

(もっと読む)

抵抗変化型メモリ

【課題】動作の信頼性が向上する抵抗変化型メモリを提案する。

【解決手段】本発明の例に関わる抵抗変化型メモリは、第1の方向に延在する第1の配線BLと、第2の方向に延在する第2の配線WLと、第1及び第2の配線BL,WLに接続され、抵抗変化型記憶素子10と非オーミック素子15とから構成される直列回路と、第1の配線BLに電流IPを与える電流供給回路8Aと、第2の配線WLに接続され、容量素子21を有する容量回路20Aと、を備える。

(もっと読む)

クラスター並びにこれを用いたスピンRAM及びスピントルク発振器

【課題】スピンRAM、スピントルク発振器などに適用できるクラスターを提案する。

【解決手段】本発明の例に係わるクラスターは、磁性発振素子としての第一磁気抵抗効果素子MTJ1と、メモリセルとしての第二磁気抵抗効果素子MTJ2とを備える。第一及び第二磁気抵抗効果素子MTJ1,MTJ2は、磁化方向が可変の磁気フリー層11−1,11−2、磁化方向が不変の磁気ピンド層12−1,12−2、及び、これらの間に配置されるスペーサー層13−1,13−2を基本構造とする。第一磁気抵抗効果素子MTJ1の磁気フリー層11−1は、第一磁気抵抗効果素子MTJ1に発振閾値電流よりも大きい電流を流したときに、第二磁気抵抗効果素子MTJ2の磁気フリー層11−2と磁気ピンド層12−2との残留磁化の磁化方向に依存した周波数で磁化振動する。

(もっと読む)

スピントルク移動磁気抵抗ランダムアクセスメモリ(STT‐MRAM)のソースローディング効果の低減

STT‐MRAMのソースローディング効果を低減するシステム及び方法が開示される。特定の実施形態では、本方法は、メモリセルの安定動作を可能にする磁気トンネル接合(MTJ)構造のスイッチング電流比を決定することを含む。メモリセルは、アクセストランジスタに直列に結合されたMTJ構造を含む。本方法は、MTJ構造の自由層に入射するオフセット磁場を変更することも含む。変更されたオフセット磁場によって、MTJ構造がそのスイッチング電流比を示すようにする。  (もっと読む)

(もっと読む)

磁性発振素子

【課題】高出力及び長寿命で、発振周波数が安定な磁性発振素子を提案する。

【解決手段】本発明の磁性発振素子は、磁化方向が可変の磁気フリー層1と、磁化方向が不変の磁気ピンド層3と、両者間に配置されるスペーサー層2と、磁気フリー層1に外部磁場を与える磁場発生部7とを備える。磁気フリー層1は、一軸磁気異方性を有し、それに発振閾値電流よりも大きな電流が流れることにより磁化振動を行う。磁場発生部7は、磁化振動による反磁場に起因する発振周波数のシフト量と磁気フリー層1の一軸磁気異方性による磁場に起因する発振周波数のシフト量とを相殺する方向に外部磁場の大きさ及び方向を制御する。磁気フリー層1の磁化振動の中心となる方向と磁気ピンド層3の磁化方向とのなす角度θは、0°≦θ≦70°及び110°≦θ≦180°の範囲内にある。

(もっと読む)

半導体装置

【課題】データの誤書き込みを防ぎ、かつレイアウト面積の増大を防ぐことが可能な半導体装置を提供する。

【解決手段】半導体装置101は、行列上に配置され、各々が、記憶データの論理値に対応する磁化方向に応じて電気抵抗値が変化する複数の磁気抵抗素子Mを含む複数の記憶部MUと、記憶部行に対応して設けられた複数の制御線WWLEと、記憶部列に対応して設けられた複数の制御線WWLと、記憶部MUに対応して設けられ、対応の記憶部MUに対応する制御線WWLEおよび制御線WWLの間に接続された複数の制御線DWWLと、記憶部MUに対応して設けられ、対応の記憶部MUに対応する制御線WWLEおよび制御線DWWLの間に接続されたダイオードDと、データ書き込み時、複数の制御線DWWLの少なくともいずれかを選択し、選択した制御線DWWLを通して書き込み電流を流す書き込み回路11とを備える。

(もっと読む)

半導体装置

【課題】記憶データに基づいて駆動電圧を負荷に供給するとともに、動作速度の低下およびレイアウト面積の増大を防ぐことが可能な半導体装置を提供する。

【解決手段】半導体装置101は、各々が、記憶データの論理値に対応する電気抵抗値を有する複数の抵抗体記憶素子Mと、複数の抵抗体記憶素子Mを通してそれぞれ読み出し電流を流す読み出し回路12と、各抵抗体記憶素子Mを通して流れる読み出し電流を加算し、加算した読み出し電流を駆動電圧に変換して負荷に供給する駆動電圧生成回路11とを備える。

(もっと読む)

薄膜磁性体記憶装置

【課題】メモリセルサイズの増加を招くことなく、安定的かつ効率的にデータ書込電流を供給可能な構成を備えた薄膜磁性体記憶装置を提供する。

【解決手段】ライトディジット線WDLは、データ書込電流の供給時に電源配線90と接続される。ライトディジット線WDLは、電源配線90側の末端付近に、MTJメモリセルの配置位置に対応する定常部分93と比較して断面積を増大ざせた強化部分95を有する。これにより、定常部分93ではMTJメモリセルの最小設計ルールに従った配線幅とすることによってメモリセルを高集積に配置できるとともに、電源配線90側の末端付近で金属原子の移動による配線幅の減少が生じても、この部分で電流密度が局所的に増大して動作信頼性に影響を与えることを防止できる。

(もっと読む)

薄膜磁性体記憶装置

【課題】メモリセルサイズの増加を招くことなく、安定的かつ効率的にデータ書込電流を供給可能な構成を備えた薄膜磁性体記憶装置を提供する。

【解決手段】各ビット線BLの両端には、データ書込電流を流すためのビット線ドライバ50が配置される。各ビット線の一端は、データ読出時に選択メモリセルからの読出データを伝達するための読出選択ゲート65を介して、データバスRDB1またはRDB2と接続される。読出選択ゲート65は、メモリセルアレイ10に対して、ビット線ドライバ50よりも外側に配置される。これにより、データ書込電流の電流経路を短くして、その経路抵抗を低減できるので、データ書込電流の確保が容易になる。

(もっと読む)

半導体装置

【課題】読み出し動作の速度低下を防ぎ、電源の低電圧化を図り、かつデータ読み出しを正確に行なうことが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1の差動アンプAMP0の第1入力端子と第1の定電圧トランジスタTRC0との間に直列接続された第1の選択トランジスタTRW0Aと、第1の差動アンプAMP0の第1入力端子と第2の定電圧トランジスタTRC1との間に直列接続された第2の選択トランジスタTRW0Bとを備え、第1の定電圧トランジスタTRC0は、第1の可変抵抗素子S0と第1の選択トランジスタTRW0Aとの間に接続され、第2の定電圧トランジスタTRC1は、第2の可変抵抗素子S2と第2の選択トランジスタTRW0Bとの間に接続されている。

(もっと読む)

1 - 20 / 36

[ Back to top ]