Fターム[5B001AD05]の内容

Fターム[5B001AD05]の下位に属するFターム

Fターム[5B001AD05]に分類される特許

1 - 9 / 9

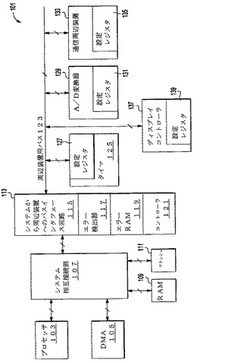

周辺装置の設定情報のエラー検出を有するデータ処理システム

【課題】高い強固であり、且つ高い信頼性を有するデータ処理システムを提供する。

【解決手段】データ処理システムは、周辺装置用バスインタフェースと動作可能に接続された第1マスタと、周辺装置用バスインタフェースに動作可能に接続された複数の周辺装置とを含む。第1マスタは、前記周辺装置用バスインタフェースを介して複数の周辺装置の各々と通信する。該データ処理システムにおける方法は、第1マスタによって設定情報を複数の周辺装置のうちの第1周辺装置に書き込みを開始することを含む。書き込み開始に応答して、第1周辺装置に格納するために周辺装置用バスインタフェースを介して設定情報が供給される。設定情報の第1エラーシンドロームは、周辺装置用バスインタフェースによって生成される。供給された設定情報は第1周辺装置に格納され、第1エラーシンドロームは周辺装置用バスインタフェースの記憶回路に格納される。第1エラーシンドロームは、次のエラー検出中に、設定情報の完全性をチェックするように使用され得る。

(もっと読む)

分散的な記憶及び通信

a)データを複数のデータサブセット(A,B)に分割し、b)複数のデータサブセット(A,B)からパリティデータ(P)を生成することで、前記複数のデータサブセットのうちの1つ又は複数のデータサブセットが、残りデータサブセットとパリティデータ(P)とから再生成されるようにすることにより、データを記憶、検索、送信、又は受信する。ステップaとbとが、前記複数のデータサブセット及び前記パリティデータの各々に対して繰り返されることにより、更なるデータサブセットと更なるパリティデータとが生成され、d)前記更なるデータサブセットと前記更なるパリティデータとが別々の記憶場所(380)に記憶されるか、又は送信される。 (もっと読む)

CPUポート設定方法

【課題】IDコードをより確実に切り替えるCPUポート設定方法を提供する。

【解決手段】

CPUポート設定方法は、2つのIDコードを4つのビット値の組で各々冗長に表現し、該組の各々は4つのビットで相互に値が異なり、CPU2の入力ポートの一部分をIDポート10(a、b、c、d)として割り当て、2つのIDコードのうち1つに対応するビット値の組をCPU2に読み取り可能に設定し、IDポート10を介してビット値の組を読み込み、読み込んだビット値の組が2つのIDコードのいずれのビット値の組に一致するかを判定し、一致した場合、当該IDコードを採用し、読み込まれたビット値の組が2つのIDコードのいずれかのビット値の組から1ビットで値が異なっている場合、読み込まれたビット値の組を、異なる当該IDコードのビット値の組に訂正し、該IDコードを採用する、各工程を備える。

(もっと読む)

データ完全性検証メカニズム

【課題】データの完全性を保守するための方法および装置が提供される。

【解決手段】ある局面の方法に従うと、物理的なチェックサム計算がデータブロック上で行なわれる(404)。物理的なチェックサム計算を行なった後、論理チェックが、データブロック内に含まれるデータ上で行なわれる(406)。データブロックが論理チェックをパスすると、データブロックは不揮発性メモリに書込まれ得る(410)。その後、データブロックが不揮発性メモリから読出されると、物理的なチェックサム検証手順がデータブロック上で行なわれて(412)、データブロック内に含まれるデータ上で論理チェックが行なわれた後にデータブロックが破損したかが判断される。

(もっと読む)

情報符号化装置、情報復号装置、情報符号化方法、および情報復号方法

【課題】複数の符号化率に対応する低密度パリティ検査符号において、回路規模を縮小しつつ、かつ、パンクチャの適用による性能の劣化を抑えることの可能な,情報符号化装置、情報復号装置、情報符号化方法、および情報復号方法を提供する。

【解決手段】検査行列により定義される低密度パリティ検査符号を符号化する情報符号化装置100において、パンクチャ開始位置を記憶するパンクチャ開始位置記憶部176と、パンクチャ終了位置を記憶するパンクチャ終了位置記憶部177と、所定の検査行列により定義される低密度パリティ検査符号の符号化をする符号化部155と、パンクチャ開始位置からパンクチャ終了位置の範囲の符号語データを削除する符号語データ削除部156とを備え、検査行列は、列方向に行重みと同数となるように複数の部分行列に分割すると、1つの部分行列の行重みが全て1となるものである。

(もっと読む)

ディジタル端末のブートプログラム書き替え方法

【課題】ブートプログラムのオンライン書き替えに、端末機能を確保し、操作者の過失等にもプログラムの破損を回避および自動修復を可能にする。

【解決手段】フラッシュROMにはブートプログラム・コア1Cとブートプログラム本体1A、1Bおよびチェックサムを書き込み、RAM上にコピーされたプログラム本体1Aは、新ブートプログラムと新チェックサムを受信してその正当性を確認し(S3)、プログラム本体1Bとそのチェックサムを消去し(S4)、この部分に新ブートプログラムと新チェックサムへ書き替え(S5)、プログラム本体1Aとそのチェックサムを消去し(S6)、この部分に新ブートプログラム本体と新アプリチェックサムへ書き替える(S7)。ブートプログラム・コア1Cは、プログラム本体1Aに異常が見受けられた場合にプログラム本体1Bの正当性を判定し、プログラム本体1Bをプログラム本体1Aにコピーすることを含む。

(もっと読む)

多次元記録システムのためのストライプに関する格子に基づく反復シンボル検出方法及び装置

例えば、幅広螺旋における2次元記録に関してビット検出を実行するとき、幅広螺旋のビット行の検出は非常に複雑になる。この複雑度を低下させるために、隣接行のサブセットに関して、検出が実行される。全ての検出と共に、サブセットは、幅広螺旋の幅をカバーする検出を結果としてもたらす。単一の検出器を用いて連続して検出を実行することに代えて、複数の検出器が用いられ、ここでは、各々の検出器は隣接検出器から得られるサイド情報を用いる。サイド情報は検出の信頼度を改善し、幅広螺旋の全幅に亘る検出に到達するサブセットの検出に繋がる。  (もっと読む)

(もっと読む)

2重化システム

【課題】 ペア・アンド・スペア構成の2重化システムにおいて、誤り検出回路、通信インターフェイスおよび制御側システムと待機側システムを接続している通信路が2重化されていないために、これらの故障が発生すると誤ったデータをメモリに書き込んでしまうという課題があった。また、これらの全てを2重化すると、コスト、実装スペース共に増大してしまうという課題もあった。

【解決手段】 サブシステムのそれぞれに誤り検出回路を設け、これらの誤り検出回路で受信したデータからチェックコードを計算し、このチェックコードと受信したチェックコードが一致したときのみ、サブシステム内のメモリ装置にデータを書き込み、一致しないときにエラー処理を行うようにした。通信インターフェイスと通信路をも2重化しなくても、これらの故障によってシステムが誤動作することはない。

(もっと読む)

エラー検出装置並びにそれを用いたエラー訂正装置及びその方法

【課題】 データビットのエラーの発生を、自身のビットのみで容易に簡単に検出すること。

【解決手段】 データビットを差動インタフェース形式で伝送した場合、受信側において、差動アンプを介して受信してこの差動アンプ出力30を、2つの比較器31,32により、互いに異なる閾値V1,V2によりそれぞれ比較し、これら比較結果をEXOR回路33にてEXOR演算して一致判定し、一致している場合は、エラー無し、不一致の場合には、エラー有りとして、エラー検出有無信号421を出力するよう構成する。これにより、1ビットのエラーの有無が、自身のビットのみにより判定可能となる。

(もっと読む)

1 - 9 / 9

[ Back to top ]