Fターム[5B005JJ21]の内容

階層構造のメモリシステム (9,317) | 目的、効果 (1,912) | 低コスト化 (210)

Fターム[5B005JJ21]の下位に属するFターム

ハードウェアの低コスト化 (161)

ソフトウェアの低コスト化 (3)

Fターム[5B005JJ21]に分類される特許

1 - 20 / 46

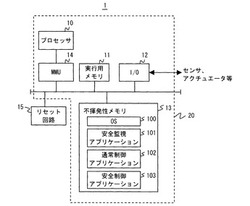

情報処理装置およびメモリ管理装置の動作確認方法

【課題】仮想アドレスを物理アドレスに変換するメモリ管理装置が正常に動作しているか否かを確認可能とする。

【解決手段】情報処理装置1は、メモリ11と、メモリ11の物理アドレス又はそれに対応する仮想アドレスを指定することで、メモリ11の物理アドレスに対してデータの読み出し又は書き込みを行うためのシステムプログラムと、システムプログラムを実行するプロセッサ10と、プロセッサ10からのメモリ11に対する仮想アドレスを指定した読み出し及び書き込みにおいて、仮想アドレスを物理アドレスに変換するメモリ管理装置14を備える。プロセッサ10は、システムプログラムによって、物理アドレスを指定してデータの書き込みを実施した後、その物理アドレスに対応する仮想アドレスを指定してデータの読み出しを実施して、書き込んだデータと、読み出したデータが一致するか否かを判定する。

(もっと読む)

キャッシュメモリ装置、プロセッサ、および情報処理装置

【課題】十分な消費電力の削減が図ることができるキャッシュメモリ装置を提供する。

【解決手段】キャッシュメモリ装置100aは、記憶装置のデータをキャッシュする。キャッシュメモリ装置100aは、記憶部110aと、制御部120aと、を備える。記憶部110aは、複数のキャッシュラインを有する。制御部120aは、前記複数のキャッシュラインのうち、前記記憶装置に書き込まれていないデータを含むダーティラインの数が予め定めた所定数を超える場合に、前記ダーティラインのデータを前記記憶装置に書き込む。

(もっと読む)

キャッシュメモリの最大レジデンシー交換のための方法およびシステム

【課題】キャッシュメモリの複数のセットウエイのレジデンシーを最大にするようにキャッシュメモリアロケーションを交換する方法を提供する。

【解決手段】ビクティムウエイのファーストイン、ファーストアウト(FIFO)交換リストを形成する。FIFO交換リストの深さは、キャッシュセット内の数にほぼ等しい。タグミスアロケーションを生じた場合にのみビクティムウエイをFIFO交換リスト上に配置する。ビクティムウエイは任意の以前に選択されたビクティムウエイの後でFIFO交換リストのおわりに配置される。ビクティムウエイのイニシャルアロケーションが完了するまで引き止めておくことにより、またはビクティムウエイのイニシャルアロケーションが完了するまで再使用リクエストをリプレイ(replay)することによりビクティムウエイの不完全な先のアロケーションの場合にFIFO交換リスト上のビクティムウエイの使用が防止される。

(もっと読む)

アクセラレータ用低コストのキャッシュ一貫性を維持するシステム

【課題】アクセラレータとCPUとの一貫性を維持しながら通信によるノード間の帯域幅の消費を低減する。

【解決手段】CPU210およびアクセラレータ220はマルチプロセッシング環境において個別のノードにクラスターできる。共有メモリ・デバイス212、222を収容する各ノード0、1は、他のノードでキャッシュされたかもしれない共有メモリのブロックを追跡するディレクトリを維持できる。そのため、コマンドとアドレスは、メモリ位置があるノード以外でキャッシュされたときに限り、他のノードのプロセッサおよびアクセラレータに送信できる。加えて、アクセラレータは一般的にCPUと同じデータにはアクセスしないため、最初の読み出し、書き込み、および同期の操作のみを他のノードに送信できる。データへの中間アクセスは一貫性を保たないで行える。その結果、一貫性を維持するために消費するチップ間の帯域幅を低減できる。

(もっと読む)

システムパフォーマンスを改善するための外部メモリデバイスの使用

【課題】回転式ストレージデバイス(例えば、ハードドライブ)のセクタをキャッシュするために外部メモリデバイスを利用して、システムパフォーマンスを改善するためのシステムおよび方法を提供すること。

【解決手段】外部メモリデバイス(EMD)が、コンピューティングデバイス、またはコンピューティングデバイスが接続されたネットワークに接続されたとき、システムは、EMDを認識し、ディスクセクタによってEMDをポピュレートする。システムは、ディスクセクタに対するI/O読取り要求を、実際のディスクセクタの代わりにEMDキャシュに向けて送る。EMDの使用は、コンピューティングデバイスにメモリを追加するコストに対してわずかのコストで、コンピューティングデバイスシステムにおけるパフォーマンスおよび生産性を向上させる。

(もっと読む)

情報処理装置およびキャッシュの制御方法

【課題】取り外されたキャッシュ装置を再度取り付けた場合に、キャッシュ装置内のキャッシュデータを有効に用いること。

【解決手段】情報処理装置は、メモリと、取り外し要求検出手段と、設定手段と、無効化手段とを具備する。メモリには、キャッシュ装置に格納されているキャッシュデータを管理するための情報が記述されているキャッシュ管理情報が格納される。取り外し要求検出手段は、キャッシュ装置の取り外し要求を検出する。設定手段は、取り外し要求が検出された場合に、キャッシュとしてのキャッシュ装置の使用を中断するキャッシュ無しモードに設定する。無効化手段は、キャッシュ無しモードにおいて記憶装置に第1データを書き込む場合、キャッシュ管理情報内の第1データに対応する第1キャッシュデータに係わる情報を無効化する。

(もっと読む)

データ処理装置、半導体装置および制御方法

【課題】RAMの使用効率を向上させるデータ処理装置を提供する。

【解決手段】データ処理装置は、CPU101と、電気的に書き換え可能な不揮発性メモリ107と、RAM105と、RAM105を、不揮発性メモリ107のプログラムをキャッシュするキャッシュメモリとして動作させる制御を行うキャッシュ制御部102と、不揮発性メモリ107を書き換えるための書き換えプログラムと書き換え用のデータとを格納するメモリとしてRAM105を利用し、当該書き換えプログラムを実行することにより不揮発性メモリ107を書き換える書き換えシーケンスを実行するフラッシュ書換部106と、キャッシュ制御部102およびフラッシュ書換部106を択一的に動作させる切換部104とを備える。

(もっと読む)

仮想アドレスキャッシュメモリ、プロセッサ及びマルチプロセッサシステム

【課題】TLBの機能をキャッシュメモリ上で実現して、回路量の削減を図ることができ、さらにタスク切り替えの応答性が向上したプロセッサを提供する。

【解決手段】仮想アドレスキャッシュメモリは、TLBの書き換えが発生したときにエントリデータの書き換えを行うTLB仮想ページメモリ21と、仮想ページタグ又はページオフセットをキャッシュインデックスとしてキャッシュデータを保持するデータメモリ23と、キャッシュインデックスに対応して前記データメモリに記憶された前記キャッシュデータのキャッシュステートを保持するキャッシュステートメモリ24と、TLBの書き換えが発生したときに、保持している物理アドレスの書き換えを行う第1の物理アドレスメモリ22と、TLBの書き換えの発生後、データメモリへの前記キャッシュデータを書き込むときに保持している物理アドレスの書き換えを行う第2の物理アドレスメモリ25とを有する。

(もっと読む)

キャッシュメモリ制御回路

【課題】複数のメモリ空間のデータをキャッシュメモリにキャッシュするキャッシュメモリ制御回路において、プロセッサの動作周波数の低減及びメモリアクセスのレイテンシの増加をさせることなく、消費電力を低減することができるキャッシュメモリ制御回路を提供する。

【解決手段】キャッシュメモリ制御回路は、それぞれがセット21a〜21d毎及びメモリ空間A及びB毎に設けられ、それぞれが対応するセットに対応するメモリ空間のデータがいくつ格納されているかをカウントする複数のカウンタ32a〜32d及び34a〜34dを有する。そして、キャッシュメモリ制御回路は、複数のカウンタ32a〜32d及び34a〜34dのそれぞれのカウント値に応じて、複数のセット21a〜21dのそれぞれのタグメモリ38a〜38d及びデータメモリ40a〜40dの活性化を制御する。

(もっと読む)

アドレス変換装置

【課題】アドレス変換すべき有効ビット数をユーザが指定しなくても、効率よくTLBにアドレス変換テーブルをキャッシュする。

【解決手段】アドレス変換装置(10)は、TLB(20)と、アドレス変換テーブルを参照して、TLB(20)に格納された対をなす論理アドレスおよび物理アドレスに連続する連続アドレス数をカウントし、当該連続アドレス数をアドレスおよび物理アドレスの対に対応付けて格納するとともに、変換対象アドレスがTLB(20)に格納された論理アドレスから連続アドレス数の範囲に含まれるか否かを判定し、変換対象アドレスがその範囲に含まれる場合、当該論理アドレスと変換対象アドレスとの差分を、当該論理アドレスと対をなす物理アドレスに加算して、変換物理アドレスを算出するアドレス変換制御部(30)と、を備えている。

(もっと読む)

集積回路、集積回路の制御方法および半導体デバイス

【課題】メモリに迅速にアクセスし、かつ、メモリの消費電力を削減すること。

【解決手段】集積回路1は、CPU3と、制御回路4とを有している。CPU3は、CPUコア3aと、メモリ管理部3bとを有している。メモリ管理部3bは、メモリ2の物理アドレスに関連付けられた仮想アドレスを保管する保管部31bを有している。このメモリ管理部3bは、CPUコア3aからの仮想アドレスへのアクセス要求に応じて、逐次、保管部31bを参照する。そして、アクセス先の仮想アドレスが存在するか否かを判断し、存在しないと判断した場合、保管部31bの仮想アドレスに対応する物理アドレスの内容を更新した情報を出力する。制御回路4は、メモリ管理部3bが出力した情報に含まれる物理アドレスを備えるメモリバンクを制御する。

(もっと読む)

オポチュニスティック・ページ・ラージフィケーション

ヒエラルキ型ページテーブルシステム内の最後のレベルのページテーブルが、候補ページテーブルのためにスキャニングされる。候補ページテーブルはラージページに変換され、ヒエラルキ型ページテーブルシステムの最後のレベルの前のレベルのページテーブルエントリが、新たに生成されたラージページに関連付けられるように調整される。ラージページがページテーブルに変換されるべきであるという通知を受け取ると、新しいページテーブルが作成される。新しいページテーブルにおける各エントリは、ラージページの小メモリセグメントに関連付けられる。また、ヒエラルキ型ページテーブルの最後のレベルの1つ前のレベルにおけるページテーブルエントリは、新しいページテーブルに関連付けられるように調整される。  (もっと読む)

(もっと読む)

ストレージ装置及びその制御方法

【課題】ストレージシステムに制御モジュールを順次追加できるように設計されても、上位装置に対して、統一された制御資源として管理できるようにしたストレージ装置及びその制御方法を提供する。

【解決手段】複数の制御モジュールのそれぞれに存在する管理部のうち、複数のモジュールに対して統一的な管理を実行する管理部を設定し、この管理部に管理ユーザがアクセスし、管理ユーザがこの管理部を介して複数のモジュールを統一的に管理するようにした。

(もっと読む)

キャッシュメモリ制御回路及びプロセッサ

【課題】通常アクセスモードと同等のキャッシュヒット性能を持ちつつ、可能な限りの低消費電力でキャッシュメモリを動作させることができるキャッシュメモリ制御回路を提供する。

【解決手段】キャッシュメモリ制御回路は、複数のウェイを所定の分割数で分割したキャッシュメモリの各ウェイあるいは2以上のウェイを、所定の順番で選択可能な選択部42と、各ウェイにおけるキャッシュヒットを検出する比較部33と、キャッシュヒットを検出すると、選択部42における各ウェイの選択を停止させる制御部41と、キャッシュメモリからのリードデータを二つのパスに伝播させて、一方が他方に対して所定の遅延量を有する2つのリードデータを比較する比較部61,62を有し、比較部61,62における2つのリードデータの一致あるいは不一致に応じて、所定の分割数を変更する分割数変更部16bとを有する。

(もっと読む)

キャッシュメモリ制御装置

【課題】キャッシュ容量の制御により、システムのスループットを安定させ、かつキャッシュメモリの電力消費を低減させることを可能とするキャッシュメモリ制御装置を提供すること。

【解決手段】キャッシュメモリ11及び主メモリ16の間におけるリフィル要求をカウントするリフィルカウンタ18と、リフィルカウンタ18によるカウント値に応じてキャッシュ容量を判定するキャッシュ容量判定部17と、を有し、キャッシュ容量判定部17は、カウント値が第1の閾値以下、又は第1の閾値未満である場合、キャッシュ容量の削減を指示するキャッシュ容量削減指示信号Sdをキャッシュメモリ11に対して送出し、カウント値が第1の閾値より大きい値である第2の閾値以上、又は第2の閾値より大きい場合、キャッシュ容量の増加を指示するキャッシュ容量増加指示信号Siをキャッシュメモリ11に対して送出する。

(もっと読む)

プロセッサ

【課題】複数のLSIでプロセッサを構成する際に、回路構成を簡素にしながらキャッシュメモリの容量が異なるプロセッサを容易に構成する。

【解決手段】プロセッサを含む第1LSIと、キャッシュメモリを備えた第2LSIと、第1LSIと複数の第2LSIを接続する情報伝達経路とを備えたプロセッサであって、第1LSIは第2LSIに対してプロセッサが要求するデータのアドレス情報を情報伝達経路からブロードキャストするアドレス情報発行部を含み、第2LSIはキャッシュメモリ全体のアドレス情報の一部を格納する部分アドレス情報格納部と、アドレス情報に対応するデータを格納する部分データ格納部と、情報伝達経路にブロードキャストされたアドレス情報と部分アドレス情報格納部に格納されたアドレス情報を比較してキャッシュヒットを判定する比較部とを含み、複数の第2LSIの比較部が情報伝達経路にそれぞれ接続される。

(もっと読む)

マルチプロセッサ・データ処理システムにおいて共有キャッシュ・ラインを与える方法、コンピュータ読み取り可能な記録媒体及びマルチプロセッサ・データ処理システム

【課題】 要求されたキャッシュ・ラインを各メモリ・ソースにおいて感知された温度値または電力消費値に基づいて、マルチプロセッサ・システムの複数のメモリ・ソースから与えるディレクトリィ・ベースのコヒーレンシ方法、システム及びプログラムを提供する。

【解決手段】 要求されたキャッシュ・ラインを共有するメモリ・ソース(例えば、コア、キャッシュ・メモリ、メモリ・コントローラ等)のそれぞれに温度または電力消費センサを設けることにより、制御論理装置は、温度または電力消費センサからの信号を使用して、許容された電力消費を伴うメモリ・ソースだけに前記要求されたキャッシュ・ラインを要求元に与えることを指示する信号を与えることにより、どのメモリ・ソースが前記要求されたキャッシュ・ラインを与えるかを決定する。

(もっと読む)

データをキャッシュする技術

【課題】キャッシュメモリからメインメモリへ効率的にデータを書き戻す。

【解決手段】各セクタが有効セクタかどうかを示す論理値を配列した有効性データについて、その有効性データの各ビットとそれに隣接する他のビットの排他的論理和を算出し、その排他的論理和を配列したビット列を、設定された検出範囲にある論理値が真のビットのうち先頭のビットを除外してビットマスクし、そのビット列のうち論理値が真であるビットのビット位置を検出し、当該ビット位置が検出される毎に、当該ビット位置よりも末尾側のビット位置を前記検出範囲として設定する処理を、当該ビット位置が検出されなくなるまで繰り返し、順次検出される当該ビット位置に基づいて、無効セクタが連続する領域ごとに、当該領域に対応するメインメモリのアドレスを算出し、その算出されたアドレスに対し読出コマンドを発行してから、キャッシュセグメントを書き戻す、記憶装置を提供する。

(もっと読む)

プログラム命令の圧縮のための圧縮エントリーの最適選択

プログラム中の命令を圧縮する方法が、プログラム中の命令から一意的な諸ビット・パターンを抽出する段階と、前記一意的なビット・パターン、前記命令および/またはメモリ記憶のサイズから線形計画法定式化または整数計画法定式化を構築する段階とを含む。線形計画法定式化または整数計画法定式化を解いて解を生成しうる。本方法は、前記解に基づいて、前記一意的なビット・パターンの少なくともいくつかをメモリに記憶し前記メモリへの対応するインデックスを新しい圧縮された命令中に入れることによって、前記命令のうち少なくともいくつかを圧縮する段階を含みうる。  (もっと読む)

(もっと読む)

キャッシュ制御回路

【課題】本発明は、現在のアプリケーションの状態に対して適切なサイズにキャッシュ容量を制御可能なキャッシュ制御回路を提供することを目的とする。

【解決手段】複数のウェイを含むセットアソシアティブ方式のキャッシュメモリを制御するキャッシュ制御回路は、キャッシュメモリの複数のウェイのうち有効データが占めている割合に応じた埋まり具合と、キャッシュメモリがアクセスされた頻度に応じた使用率と、キャッシュメモリへのアクセスのミスの割合に応じたミス率とを求める測定部と、埋まり具合と、使用率と、ミス率とに応じてキャッシュメモリの複数のウェイ毎の起動及び停止を制御する制御部を含むことを特徴とする。

(もっと読む)

1 - 20 / 46

[ Back to top ]