Fターム[5B005MM01]の内容

階層構造のメモリシステム (9,317) | 階層メモリの種類 (2,100) | キャッシュメモリ (1,180)

Fターム[5B005MM01]の下位に属するFターム

命令キャッシュ (87)

データキャッシュ (101)

ソフトウェアキャッシュ (71)

複数のキャッシュメモリ (190)

Fターム[5B005MM01]に分類される特許

1 - 20 / 731

ソフトエラー耐性調整機能を備えた電子システム装置及びソフトエラー耐性調整方法

不揮発性キャッシュメモリ、不揮発性キャッシュメモリの処理方法、コンピュータシステム

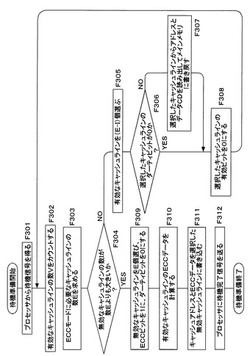

【課題】不揮発性メモリをキャッシュメモリとして使用する場合に、電力遮断状態での保持されているデータの信頼性を向上させる。

【解決手段】キャッシュデータの記憶に不揮発性メモリを用いる。この場合に、電力供給遮断の準備として、待機状態データを生成して不揮発性メモリ部上に記憶する待機準備処理を行う。また電力供給再開の際に、待機状態データを用いて不揮発性メモリ部に記憶されたキャッシュデータの復帰処理を行う。

(もっと読む)

プログラム変換装置、プログラム変換方法、および変換プログラム

【課題】プロセッサコアが夫々キャッシュメモリを有するマルチプロセッサ環境で前記キャッシュメモリを効率よく使用できるようにプログラムを変換すること。

【解決手段】プログラム変換装置は、アクセス属性決定部と、非共有化対象分類部と、変換部とを備える。アクセス属性決定部は、ソースプログラムを構成するスレッドによるメモリアクセスから排他アクセスを求め、前記求めた排他アクセスのうちからキャッシュメモリを使用するメモリアクセスを決定する。非共有化対象分類部は、前記キャッシュメモリを使用してメモリアクセスされるアクセスデータのうちから、他のアクセスデータとの間でキャッシュラインを非共有化させるアクセスデータを決定する。変換部は、前記非共有化対象分類部による決定結果に基づいてキャッシュラインを非共有化させる処理をソースプログラムに挿入する。

(もっと読む)

キャッシュ装置、メモリシステム及びデータ転送方法

【課題】キャッシュデータを効率的にメインメモリへライトバックすることができるキャッシュ装置、メモリシステム及びデータ転送方法を提供すること

【解決手段】本発明にかかるキャッシュ装置は、複数のキャッシュデータが、メインメモリ80に格納されている複数のデータと一致しているか否かを判定するライトバック制御部60と、複数のキャッシュデータのうち、不一致と判定されたキャッシュデータであって、メインメモリ80において連続するアドレスへ書き込まれる複数のキャッシュデータを格納するデータバッファ部13と、データバッファ部13へ格納されたキャッシュデータを一括してメインメモリ80へ書き込むメモリライト部14と、を備えるものである。

(もっと読む)

演算処理装置

【課題】キャッシュメモリから高速にデータを読み出すことができる演算処理装置を提供することを課題とする。

【解決手段】演算処理装置は、複数の記憶素子にそれぞれ複数のデータを記憶するキャッシュメモリと、前記キャッシュメモリからデータが読み出されたタイミングが閾値より遅いときにはエラーを検出するエラー検出回路(500)と、前記エラーが検出されないときには前記キャッシュメモリから読み出されたデータをラッチし、前記エラーが検出されたときには待機期間経過後に前記キャッシュメモリから読み出されたデータをラッチするラッチ回路(517)と、前記ラッチ回路によりラッチされたデータの処理を行う演算処理装置コアとを有する。

(もっと読む)

複数のデータ・エレメントの収集及び分散

【課題】複数のデータ・エレメントの収集及び分散におけるオーバーヘッドを低減するプロセッサを提供する。

【解決手段】効率的なデータ転送処理は、単一の命令が複数のデータ・エレメントに対する第1の記憶域と第2の記憶域との間の転送処理を指定し、プロセッサ装置140,160によりデコードする段階、前記プロセッサ内の演算実行部による実行のために単一の命令を発行する段階、単一の命令の実行中に例外の発生を検出する段階、及び該例外に応答して、該例外を分配する前に、未解決のトラップ又は割り込みを例外ハンドラに分配する段階、により達成されうる。

(もっと読む)

部分読出と非スヌープアクセスとの間のメモリ順序付け要件の充足

【課題】部分的且つ非コヒーレントなメモリアクセスの観点からキャッシュ・コヒーレンス・リンクに基づく相互接続でメモリ順序付けを保つ方法及び装置を提供する。

【解決手段】例えば部分書込のような部分的なメモリアクセスに関連するコンフリクトが検出される場合に、ライトバックフェーズがコンフリクトフェーズで挿入され、ホームエージェントへ部分的データをライトバックする。コンフリクトフェーズでライトバックフェーズを挿入するメッセージの例には、コンフリクトを認めて、コンフリクトフェーズの開始時にライトバックマーカーを、コンフリクトフェーズ前にライトバックマーカーメッセージを、コンフリクトフェーズ内でライトバックマーカーメッセージを、コンフリクトフェーズ後にライトバックマーカーメッセージ及びポスタブル・メッセージを提供するAcknowledge Conflict Write-backメッセージがある。

(もっと読む)

情報処理装置

【課題】ネットワーク透過な単一レベル記憶を実現すること。

【解決手段】本発明の一つの実施形態によれば、情報処理装置は、第1メモリと、第2メモリと、仮想アドレス空間の少なくとも一部の仮想アドレスと前記第1メモリの物理アドレスとの対応関係を管理する変換情報を参照して、前記第1メモリにアクセスする制御部と、を備える。前記仮想アドレス空間には、他の情報処理装置に格納されたデータも割り当てられる。前記制御部は、アクセス対象データが前記他の情報処理装置に格納され手いる状態でページフォールトが発生した場合、前記他の情報処理装置に格納された前記アクセス対象データを前記第1メモリに格納するとともに、前記アクセス対象データに対応する仮想アドレスと前記第1メモリの物理アドレスの対応関係を前記変換情報に登録する。

(もっと読む)

低電力モード中にキャッシュされた情報を保存する技術

【課題】コンピューティング・システムおよびマイクロプロセッサ内の電力管理分野に関するプロセッサ、システム、および、方法を提供する。

【解決手段】低電力モード中にキャッシュされた情報を保持するための技術である。プロセッサ100のローカル・キャッシュ107,113に格納された情報は、プロセッサが低電力モードに置かれる前に共有キャッシュ115に保存されるので、他のプロセッサは、低電力モードのプロセッサを、そのローカル・キャッシュへのアクセスを提供するように低電力モードから復帰させる代わりに、共有キャッシュからの情報にアクセスする。

(もっと読む)

制御システム、制御方法およびプログラム

【課題】プリフェッチに使用される電力が無駄になることを防止可能な制御システム、制御方法およびプログラムを提供する。

【解決手段】制御システム100は、処理装置と主記憶装置とキャッシュメモリとプリフェッチ部と電源部とを備えた制御システムであって、検出部81と判定部82と電源制御部83とを備える。検出部81は、処理装置が処理を実行していないアイドル状態であるか否かを検出する。判定部82は、アイドル状態であると検出された場合、プリフェッチの状態に応じて、キャッシュメモリに対する電力の供給を停止するか否かを判定する。電源制御部83は、キャッシュメモリに対する電力の供給を停止すると判定された場合は、キャッシュメモリに対する電力の供給を停止するように電源部を制御し、キャッシュメモリに対する電力の供給を停止しないと判定された場合は、キャッシュメモリに対する電力の供給を継続するように電源部を制御する。

(もっと読む)

制御システム、制御方法およびプログラム

【課題】消費電力量を低減可能な制御システム、制御方法およびプログラムを提供する。

【解決手段】制御システム100は、検出部51と推定部52と判断部53と制御部54とを備える。検出部51はアイドル状態を検出する。推定部52はアイドル時間を推定する。判断部53は、アイドル状態が検出された場合、主記憶装置への書き戻しが必要なデータの書き戻しを行ってキャッシュメモリに対する電力の供給を停止した場合の第1消費電力量が、当該データの書き戻しを行わずにアイドル時間にわたってキャッシュメモリに対する電力の供給を継続した場合の第2消費電力量よりも大きいか否かを判断する。制御部54は、第1消費電力量が第2消費電力量よりも小さいと判断された場合は、キャッシュメモリに対する電力供給を停止させる一方、第1消費電力量が第2消費電力量よりも大きいと判断された場合は、キャッシュメモリに対する電力供給を継続させる。

(もっと読む)

キャッシュメモリ装置、プロセッサ、および情報処理装置

【課題】十分な消費電力の削減が図ることができるキャッシュメモリ装置を提供する。

【解決手段】キャッシュメモリ装置100aは、記憶装置のデータをキャッシュする。キャッシュメモリ装置100aは、記憶部110aと、制御部120aと、を備える。記憶部110aは、複数のキャッシュラインを有する。制御部120aは、前記複数のキャッシュラインのうち、前記記憶装置に書き込まれていないデータを含むダーティラインの数が予め定めた所定数を超える場合に、前記ダーティラインのデータを前記記憶装置に書き込む。

(もっと読む)

マルチプロセッサ・システムにおけるキャッシュ・コヒーレンスにおいて用いるフォワード状態

【課題】修正、排他的、共有、無効、及びフォワード(MESIF)の5つの状態を有するキャッシュ・コヒーレント・プロトコルを提供する。

【解決手段】MESIFキャッシュ・コヒーレント・プロトコルは、更なる複製を行い得る、データの単一複製を指定するフォワード(F)状態を含む。F状態におけるキャッシュ・ラインは、キャッシュ・ラインの複製の要求に応答するのに用いられる。一実施例では、新たに作成される複製がF状態に置かれ、先行してF状態にあったキャッシュ・ラインは共有(S)状態又は無効(I)状態に置かれる。よって、キャッシュ・ラインが共有されている場合、1つの共有複製はF状態にあり、キャッシュ・ラインの残りの複製はS状態にある。

(もっと読む)

異なるキャッシュ・コヒーレンス・ドメインの間の情報共有技法

【課題】異なるキャッシュ・コヒーレンス・ドメイン内のエージェント間での情報共有を可能にする。

【解決手段】ある実施形態では、グラフィック装置が、情報を記憶または読み出しするために一つまたは複数の処理コアによって使用される一つまたは複数のキャッシュを使用しうる。前記一つまたは複数のキャッシュは、前記グラフィック装置に関するプログラミングおよびコヒーレンス規則に影響しない仕方で、一つまたは複数の処理コアによってアクセスされうる。

(もっと読む)

排他制御装置、方法及びプログラム

【課題】コア同士がキャッシュメモリを用いて通信を行っている場合に、コア間の通信速度の低下を防ぐこと。

【解決手段】排他制御装置は、プロセスによってコア間の通信に用いられるメインメモリの論理アドレスを物理ページ番号に変換し、プロセスと物理ページ番号とを対応付けてキャッシュ禁止テーブルに格納するキャッシュ禁止領域指定部と、物理ページ番号に対応するキャッシュラインを計算し、キャッシュラインを使用する物理ブロック番号をキャッシュ禁止テーブルに格納するキャッシュライン計算部と、キャッシュ禁止テーブルに格納された物理ページ番号が、キャッシュ禁止テーブルにおいて物理ページ番号に対応付けられたプロセス以外のプロセスに対するプロセス管理情報のページテーブルエントリに存在する場合には、キャッシュを禁止するためのフラグを当該エントリに設定するキャッシュ禁止部を有する。

(もっと読む)

アプリケーションが決定したスケジューリングによる効率的なキャッシュの再利用

【課題】マルチプロセッサコンピュータシステにおいて効率的なキャッシュの再利用を図る。

【解決手段】コンピュータシステム100においてタスクを実行すべく複数のスレッドからスレッドを決定する方法が開示される。複数のスレッドは、コンピュータシステムのキャッシュメモリと関連付けられた少なくとも1つのサブセットにグループ化される。タスクは、命令の集合により決定された型を有する。方法は、複数のスレッドのサブセットの実行履歴を取得し、命令の集合及びデータの集合毎にタスク型に依存する重み付けを決定する。次に、実行履歴及び決定された重み付けに基づいてタスクを実行するスレッドのサブセットの適合性が決定される。決定されたスレッドのサブセットの適合性を条件として、スレッドのサブセットと関連付けられたキャッシュメモリの内容を使用してタスクを実行すべくスレッドのサブセットからスレッドを決定する方法が開示される。

(もっと読む)

記憶制御システムおよび方法、置換方式および方法

【課題】キャッシュ置換方法に関し、無駄なプリチャージを削減しメモリの消費電力を削減する。

【解決手段】DRAM100内のロウバッファ102は、メモリアレイ101から所定のデータ長を単位とするいずれかのデータを読み出して格納する。LLC206は、ロウバッファ102に記憶されたデータの一部をキャッシュデータとして抽出して記憶するキャッシュメモリである。MAC601において、LLC206の追い出し制御が実施される場合に、MRQ203のキューイング状態に基づいて近い将来ロウバッファ102にどのDIMMアドレスのデータが記憶されるかを予測する。MACにおいて、LLC上の追い出し対象範囲702のキャッシュデータデータの各物理アドレスをDIMMアドレスに変換する。変換された各アドレスと予測されたデータのアドレスとが一致した場合に、その一致アドレスに対応するキャッシュデータを優先してLLCから追い出す。

(もっと読む)

同時保留中データアクセスリクエストのためのデータハザード処理

【課題】イニシエータデバイスではなく、コヒーレンシコントローラでデータハザードを管理する、データ処理システムを提供する。

【解決手段】2つの部分形式で書き込みリクエストを処理する。同じアドレスに対し同時保留の読み出しおよび書き込みが存在する時、書き込みの第1の部分に応答しないことでコヒーレンシコントローラにより延期され、イニシエータデバイス10は、書き込みが保留中に関係なく、書き込みのアドレスに受信されたいずれのスヌープリクエストも処理するように進行する。保留中の読み出しが完了すると、コヒーレンシコントローラは、書き込みの第1の部分に応答し、イニシエータデバイスは、データおよびスヌープ後のデータの状態のインジケータを送信することによって、書き込みを完了する。コヒーレンシコントローラは、必要に応じてメモリを更新するためにこの情報を使用して潜在的なデータハザードも回避することができる。

(もっと読む)

共有キャッシュメモリ制御

【課題】データ共有の効率性とキャッシュ記憶容量の使用との間でバランスのとれた共有キャッシュメモリの制御が可能なデータ処理装置を提供する。

【解決手段】データ処理システムは、複数のローカルキャッシュメモリと、共有キャッシュメモリとを有する、キャッシュ階層を含む。キャッシュライン毎に共有キャッシュメモリ内に記憶された状態データは、データのキャッシュラインがキャッシュメモリシステムの非包括的動作または包括的動作にしたがって記憶または管理されているかどうかを制御するために用いられる。スヌープトランザクションは、データのキャッシュラインが一意的であるかまたは非一意的であるかどうかを示すデータに基づいてフィルタリングされる。非包括的動作から包括的動作への切り換えは、データのキャッシュラインを要求する、受け取られたトランザクションのトランザクション種別に応じて、実行されてもよい。

(もっと読む)

半導体集積回路

【課題】性能低下を招くことなく回路面積を削減出来る半導体集積回路を提供すること。

【解決手段】第1メモリ30と、第1メモリ30に対するキャッシュメモリとして働く第2メモリ10とを備える。第1メモリ30からデータが読み出される場合の第1読み出し、第2メモリ10からデータが読み出される場合の第2読み出し、及び該データを第2メモリ10から読み出すと決定する判定、は、複数の処理ステージのうちのいずれかの処理ステージで実行される。第1読み出しにて読み出されたデータが出力されるタイミングと、第2読み出しにて読み出されたデータが出力されるタイミングとは同一である。第1読み出しで読み出されたデータは、第2メモリ10を経由しない経路を用いて出力される。

(もっと読む)

1 - 20 / 731

[ Back to top ]