Fターム[5B005NN31]の内容

階層構造のメモリシステム (9,317) | W/R制御 (1,413) | タグ処理 (435)

Fターム[5B005NN31]の下位に属するFターム

Fターム[5B005NN31]に分類される特許

1 - 20 / 48

演算処理装置および演算処理装置の制御方法

【課題】キャッシュメモリを実装した演算処理装置およびキャッシュメモリ制御装置において、プロセスIDに対応してキャッシュメモリ領域をブロック単位で任意に分割可能として、プロセッサの実効性能を向上することを可能とする。

【解決手段】各セット103のキャッシュブロック102毎に物理プロセスID(PPID)が記憶されるとともに、#1から#nの各インデックス値毎に、各PPID値に対するMAX WAY数105が記憶される。或るインデックス値における或るPPID値に対応するMAX WAY数105は、そのインデックス値において記憶可能なそのPPID値を有するキャッシュブロック102の最大数を示す。各インデックス値毎に、各PPID値のMAX WAY数105が守られるように、キャッシュミス時のウェイ数の制御が実施される。

(もっと読む)

記録再生装置

【課題】キャッシュデータを管理するキャッシュ管理情報を記録再生装置内の揮発性メモリに格納した場合、装置の電源オフ時にキャッシュ管理情報が削除される。装置に搭載された記録媒体に効率よくキャッシュ管理情報のバックアップを取る方法が望まれる。

【解決手段】キャッシュ管理情報は記録再生装置の内蔵メモリ(例えばSRAM)に記録される。記録再生装置のストレージ制御部は、例えばキャッシュ管理情報の更新を検知した場合に、キャッシュ管理情報を例えばHDDに書き込んでバックアップを取る。また、例えば記録再生装置の電源オンを検知した場合には、例えばHDDにバックアップしておいたキャッシュ情報を読み出す。

(もっと読む)

情報処理装置およびキャッシュ制御方法

【課題】大容量のキャッシュデバイスを用いても、少ない容量のメモリで、性能低下を抑えること。

【解決手段】実施形態によれば、情報処理装置は、第1の記憶装置のキャッシュ領域を第2の記憶装置のキャッシュとして用いて、第2の記憶装置へのデータの書き込みおよび第2の記憶装置からのデータの読み出しを所定のデータ長のブロック単位で処理するキャッシュ制御手段であって、キャッシュ領域内のキャッシュデータの状態を所定のデータ長のセクタ単位で示すセクタビットマップをキャッシュ領域の各ブロック毎に設け、第1の記憶装置内の管理データ領域内で、第1の記憶装置のキャッシュ領域内の全てのブロックに対応するセクタビットマップをビットマップとして管理し、メモリ内に確保されるキャッシュ領域をビットマップのキャッシュとして用いるこキャッシュ制御手段を具備する。

(もっと読む)

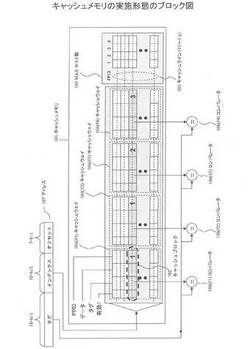

キャッシュメモリ制御装置と方法

【課題】タイミングマージンを確保しつつ、高速化を可能としキャッシュメモリのアクセス時間を短縮する。

【解決手段】第1のクロック信号で、データキャッシュメモリ20Aに供給するアドレス1、データウエイを同期させ、前記データキャッシュメモリに前記第1のクロック信号ととともに供給する第1のクロック同期部16Aと、第2のクロック信号で、タグキャッシュメモリ20Bに供給するアドレス2、タグウエイを同期させ、前記タグキャッシュメモリに、前記第2のクロック信号とともに供給する第2のクロック同期部16Bと、複数ウエイのタグとCPUのアクセスアドレスの所定ビットフィールドのアドレスとの一致・不一致の比較するアドレス比較部11−1/2を備え、前記第2のクロック信号の周波数は前記第1のクロック信号の周波数よりも高く設定される。

(もっと読む)

記憶効率の高いセクタ化されたキャッシュ

仮想アドレスキャッシュメモリ、プロセッサ及びマルチプロセッサシステム

【課題】TLBの機能をキャッシュメモリ上で実現して、回路量の削減を図ることができ、さらにタスク切り替えの応答性が向上したプロセッサを提供する。

【解決手段】仮想アドレスキャッシュメモリは、TLBの書き換えが発生したときにエントリデータの書き換えを行うTLB仮想ページメモリ21と、仮想ページタグ又はページオフセットをキャッシュインデックスとしてキャッシュデータを保持するデータメモリ23と、キャッシュインデックスに対応して前記データメモリに記憶された前記キャッシュデータのキャッシュステートを保持するキャッシュステートメモリ24と、TLBの書き換えが発生したときに、保持している物理アドレスの書き換えを行う第1の物理アドレスメモリ22と、TLBの書き換えの発生後、データメモリへの前記キャッシュデータを書き込むときに保持している物理アドレスの書き換えを行う第2の物理アドレスメモリ25とを有する。

(もっと読む)

キャッシュ装置、演算処理装置及び情報処理装置

【課題】命令キャッシュタグの消費電力を低減すること。

【解決手段】命令キャッシュタグのメモリの物理的構成要素としてレジスタファイルを用いる。レジスタファイルは、命令キャッシュタグの検索に用いるn(nは自然数)ビットのキャッシュインデックスの各ビットに対応するn段のマルチプレクサ群によってエントリを選択する。n段のマルチプレクサ群のうち、キャッシュインデックスのうち最下位からmビット目を制御信号として用いるm段目のマルチプレクサ群は、2の(m−1)乗個のマルチプレクス回路を有する。m段目のマルチプレクサ群に含まれる全てのマルチプレクス回路は、mビット目の制御信号に応じて一斉に切り替えられる。

(もっと読む)

情報処理装置、回路、情報処理方法、及びプログラム

【課題】 移動するデータ要素をパイプラインの各ステージで確実かつ高速に相互作用させるための技術を提供する。

【解決手段】 データ処理装置は、複数のノードをそれぞれ有する第1、第2パイプラインと、第1、第2パイプラインのノードのデータを用いてデータ処理を行う処理手段とを備える。ここで、第2パイプラインにおけるデータの移動方向は第1パイプラインと逆方向であり、処理手段は、第2パイプラインのデータが移動していない場合は、第1パイプラインのノードのデータと、当該ノードに対応する第2パイプラインのノードのデータとを用いたデータ処理結果を出力し、第2パイプラインのデータが移動している場合は、第1パイプラインのノードのデータと、当該ノードに対応する第2パイプラインのノードの上手のノードのデータとを用いたデータ処理結果を出力する。

(もっと読む)

キャッシュメモリ装置

【課題】設定されるウェイの数に応じて構成が変更された後のキャッシュメモリに対するデータの書き込みがデータの書き込みを実現する。

【解決手段】2n個の制御手段50の各々は、データの書き込み時において、バンク選択データ(X1,X0)およびウェイ指定データMemに基づいて、当該制御手段50に対応するバンクBが有効であるか否かを判定し、有効であると判定した場合にインデックスデータIndexにて指定される当該バンクBのキャッシュラインCにタグデータTgと当該タグデータTgに対応する外部メモリ内のデータとの書き込みを許可する。

(もっと読む)

キャッシュメモリ装置及び画像処理装置

【課題】画像データを記憶するキャッシュメモリ装置において、キャッシュヒット率を向上させたキャッシュメモリ装置及びキャッシュメモリ装置の制御方法を提供する。

【解決手段】キャッシュメモリ装置11bは、フレームの画像データを所定のサイズ毎に1キャッシュブロックとして、記憶するメモリ部22と、画像データのメモリアドレスを、フレームの水平方向において、所定のサイズ単位で互いに異なる複数のインデックスが割り当てられるように変換して、アドレスデータを生成するアドレス変換部25とを有し、アドレス変換部25において変換されて生成されたアドレスデータに基づいて、タグ、インデックス及びブロック内アドレスを指定することにより、画像データが出力データとしてメモリ部22から出力される。

(もっと読む)

セットアソシアティブ方式のキャッシュ装置及びキャッシュ方法

【課題】データメモリのアドレスの一部をウェイ情報と置き換えることで、複数のウェイの全ての出力を同時に利用する。

【解決手段】セットアソシアティブ方式のキャッシュメモリ12は、アドレスの所定の上位ビットであるタグを記憶するタグメモリ21と、リクエストアドレス(RA)の中のタグとタグメモリ21に記憶されているタグとを比較するタグ比較器22と、タグ比較器22が比較して得られたウェイ情報をColumnアドレスの一部に組み入れたデータメモリ25とを有する。

(もっと読む)

仮想アドレスキャッシュメモリ及び仮想アドレスキャッシュ方法

【課題】TLBの機能をキャッシュメモリ上で実現して、回路量の削減を図り、かつエイリアスの問題を解消する仮想アドレスキャッシュメモリを提供する。

【解決手段】仮想アドレスキャッシュメモリ12は、プロセスの仮想アドレスの所定の上位ビットの仮想ページタグを含むエントリデータを保持し、プロセッサからの仮想ページタグが一致するとヒット信号を出力するTLB仮想ページメモリ21と、仮想ページタグとページオフセットをキャッシュインデックスとしてキャッシュデータを保持するデータメモリ23と、キャッシュインデックスに対応してデータメモリ23に記憶されたキャッシュデータのキャッシュステートを保持するキャッシュステートメモリ24と、を有する。

(もっと読む)

システムインターフェースへダイレクトアクセスするメモリマネージメントユニット

1以上のプロセッサスレッドからのトランザクションリクエストをサービスするためのメモリマネージメントユニット(MMU)が開示される。MMUは、トランスレーションルックアサイドバッファ(TLB)を含む。TLBは、ストレージモジュール及びロジック回路を含む。ストレージモジュールは、複数のインターフェースの1つを指し示すビットを記憶する。ビットは、物理アドレスレンジに関連付けられることができる。ロジック回路は、物理アドレスレンジ内の物理アドレスを複数のインターフェースの1つに届けることができる。  (もっと読む)

(もっと読む)

キャッシュメモリシステム

【課題】本発明は、キャッシュシステムにおいて、way数を維持したまま、キャッシュメモリの容量を動的に変更できるようにする。

【解決手段】たとえば、キャッシュメモリの容量を削減させる場合、プロセッサ11より“削減の指示”が出力される。すると、キャッシュ増減処理ユニット26は、“現在のサイズ”と“変更後のサイズ”とに応じて、無効化するインデックスの範囲を設定するとともに、アービタ24に対して、該当するインデックスの無効化を要求する。一方、インデックス変換機25は、アービタ24からのアドレスに対応する、“現在のサイズ”にもとづいたインデックスまたは“変更後のサイズ”にもとづいたインデックスのいずれかを選択し、タグメモリ21内から対応するタグ情報を読み出して、データメモリ23上の該当するインデックスを無効化する。

(もっと読む)

半導体記憶装置及びその半導体記憶装置を用いたシステム

【課題】キャッシュコヒーレンシを維持するため、データ記憶領域と、これに対応する情報記憶領域とに対するアクセスを同時に行うことができ、かつシステムにおけるメモリのオーバーヘッドを抑制することができる半導体記憶装置を提供する。

【解決手段】複数のビット線及びワード線の交点に配置された複数のメモリセルからなり、データを記憶する複数のビット単位の単位データ領域からなるデータ記憶領域と、単位データ領域各々に対応し、単位データ領域に記憶されるデータに関する情報を記憶する単位情報領域からなる情報記憶領域とからなるメモリセルアレイと、ワード線を選択するロウアドレスデコーダと、ビット線を選択するカラムアドレスデコーダと、カラムアドレスの一部または全てを用い、情報記憶領域におけるデータ単位領域に対応した単位情報領域のビット線を選択する情報記憶領域アドレス生成回路とを有する。

(もっと読む)

キャッシュタグ試験方式

【課題】本発明はキャッシュタグを持つCPUとメモリとを含むノードが複数個と,前記複数のノードを相互に接続するクロスバーを備えたシステムにおけるオペレーティングシステムによるキャッシュタグ試験方式に関し,無駄なメモリ資源の獲得をすることなく且つノードを指定してキャッシュタグ試験を実施することを目的とする。

【解決手段】システムに含まれるCPU数を検出するCPU数チェック部と,試験の対象となるキャッシュタグを持つ自CPU搭載のノードを識別するノードチェック部と,前記CPU数チェック部とノードチェック部とにより検出した試験対象CPUを搭載するノード以外の他ノードを指定してメモリを獲得するメモリ獲得部とを備え,メモリ獲得部により獲得した試験対象のメモリ領域に対し,期待値データを格納して,試験対象のメモリ領域のデータと期待値データを比較することにより試験を行うメモリ試験部とを備えるよう構成する。

(もっと読む)

キャッシュメモリ、キャッシュメモリ装置及び割当て方法

【課題】データメモリマクロが占める面積を小さくし、配線遅延等を防止し、性能向上を図る。

【解決手段】各データメモリマクロユニットの格納位置は、ウェイ番号と、インデックス番号と、ワード番号とによって指定され、複数のデータメモリマクロユニットに対しN個のキャッシュデータを同時書き込み許可すべく、複数のデータメモリマクロユニットのいずれか1つのデータ入力端子にそれぞれ接続されている複数のマルチプレクサを備え、同一のインデックス番号及び相違するワード番号によって指定された前記それぞれのキャッシュデータは、各データメモリマクロユニットに共通に格納され、同一のインデックス番号及び相違するウェイ番号によって指定された前記それぞれのキャッシュデータは、相違するデータメモリマクロユニットに格納される。

(もっと読む)

マルチスレッドおよびマルチコア・システムのためのキャッシュ、および、その方法

一実施例に従って、本発明は一般にプロセッサのキャッシュの性能を改善する方法を提供する。本方法は、データ・ランダム・アクセス・メモリ(RAM)内に複数のデータを格納することを含む。本方法は、さらに、次のレベルのメモリ・サブシステムへ転送された全ての未処理の要求のための情報を保持することを含む。本方法は、さらに、要求が実行された後、サービスされた要求に関連する情報をクリアすることを含む。本方法は、さらに、後続の要求が、次のレベルのメモリ・サブシステムに既にインフライトしている1またはそれ以上の要求に提供されたアドレスと一致するかどうかを決定することを含む。本方法は、さらに、次のレベルのメモリ・サブシステムによってサービスされた実行済みの要求を、オリジナルの要求が次のレベルのメモリ・サブシステムへインフライトしていた間に要求を出した少なくとも1つのリクエスタと一致させることを含む。本方法は、さらに、各要求に特有の情報を格納することを含み、その情報は設定属性および経路属性を含み、設定および経路属性は、データが戻されると直ちに、戻されたデータがデータRAM内のどこに保持されるべきかを識別するために形成され、各要求に特有の情報は、さらに、スレッドID、命令待ち行列の位置、およびカラーのうちの1つを含む。本方法は、さらに、ヒットおよびミス・データの戻りをスケジュールすることを含む。もちろん、これ以外の様々な実施例も、本発明の範囲内である。  (もっと読む)

(もっと読む)

情報処理装置およびデータ検索方法

【課題】マルチレベルインクルージョンを満足しつつ、小さい回路規模で、検索を高速に行える複数のプロセッサの階層キャッシュメモリ装置およびデータ検索方法を提供する。

【解決手段】1次キャッシュメモリ装置を内蔵する複数のプロセッサと、主記憶装置と、その間に設けられる2次キャッシュメモリ装置とを有する情報処理装置において、アドレスの一部から一意に決定される順番で、1つのL1用インデックスから複数のL2用インデックスを作成する手段(111、121、131、141)を設け、当該複数のL2用インデックスにより指定される2次キャッシュメモリ装置内の記憶領域の検索を行う手段とを備えた。

(もっと読む)

画像データ処理方法、画像データ処理方法のプログラム、画像データ処理方法のプログラムを記録した記録媒体及び画像データ処理装置

【課題】本発明は、画像データ処理方法、画像データ処理方法のプログラム、画像データ処理方法のプログラムを記録した記録媒体及び画像データ処理装置に関し、例えばMPEG−4AVC/ITU−T H.264方式による動画像データの符号化装置、復号化装置に適用して、キャッシュメモリを小容量化しつつ、メモリバスのアクセス頻度を低下させることができる。

【解決手段】本発明は、水平方向及び垂直方向がそれぞれ複数の読み出し単位である領域を特定するようにアドレスデータを発行して、参照画像データをキャッシュメモリに格納する。

(もっと読む)

1 - 20 / 48

[ Back to top ]