Fターム[5B005PP11]の内容

階層構造のメモリシステム (9,317) | 一致制御 (671) | 同じ階層のメモリの一致制御 (98)

Fターム[5B005PP11]の下位に属するFターム

多重仮想メモリの一致制御 (2)

Fターム[5B005PP11]に分類される特許

1 - 20 / 96

マルチプロセッサ・システムにおけるキャッシュ・コヒーレンスにおいて用いるフォワード状態

【課題】修正、排他的、共有、無効、及びフォワード(MESIF)の5つの状態を有するキャッシュ・コヒーレント・プロトコルを提供する。

【解決手段】MESIFキャッシュ・コヒーレント・プロトコルは、更なる複製を行い得る、データの単一複製を指定するフォワード(F)状態を含む。F状態におけるキャッシュ・ラインは、キャッシュ・ラインの複製の要求に応答するのに用いられる。一実施例では、新たに作成される複製がF状態に置かれ、先行してF状態にあったキャッシュ・ラインは共有(S)状態又は無効(I)状態に置かれる。よって、キャッシュ・ラインが共有されている場合、1つの共有複製はF状態にあり、キャッシュ・ラインの残りの複製はS状態にある。

(もっと読む)

複数ノード間での通信方法、相互接続ポートおよび相互接続システム

【課題】複数のノード間での通信方法を開示する。

【解決手段】各ノードは、複数のプロセッサおよび相互接続チップセットを含み、第1のノード内のプロセッサからデータ要求を発行し、拡張ポート(またはスケーラビリティポート)を通してこのデータ要求を他のノードに渡す。また、データ要求に応答してメモリのアクセスを開始し、各ノード内の各プロセッサのプロセッサキャッシュをスヌープする。従って、該要求を発行するプロセッサを持つノード内の(あるいは別のノードの)プロセッサキャッシュまたはメモリ内のデータの格納場所を識別する。さらに、ルータシステムにて2つの直接結合されたノード間でデータを要求する方法と、相互接続システム内の3またはそれ以上のノード間でのデータ要求方法と、相互接続システム内のクロスケースの解消方法と、ノードを直接またはプロトコルエンジンを通して結合するための相互接続システムも開示する。

(もっと読む)

マルチコアプロセッサシステムおよびマルチコアプロセッサ

【課題】キャッシュの一貫性をソフトウェアで維持することができるクラスタ型のマルチコアプロセッサシステムを得ること。

【解決手段】メモリ領域は、1次キャッシュおよび2次キャッシュをともに使用する第1のアクセスによる読み書きが許可され、1つのタスクに独占的な使用権が与えられている第1の状態と、2次キャッシュのみ使用する第2のアクセスによる読み書きが許可され、1つのプロセスに独占的な使用権が与えられている第2の状態と、キャッシュを使用しない第3のアクセスによる読み書きが許可され、全てのプロセスに使用権が与えられている第3の状態とを容認する。カーネル部は、第1の状態から第2の状態に遷移させるとき、1次キャッシュを2次キャッシュにライトバックし、第2の状態から第3の状態に遷移させるとき、2次キャッシュをメモリ領域にライトバックする。

(もっと読む)

キャッシュ競合の解決

【課題】マイクロプロセッサ内及び/又はコンピュータ・システム内のキャッシュ・アクセス競合の防止。

【解決手段】処理401では、コア・キャッシュ線への読み取り要求が検出され、対応するコア・キャッシュへの読み取り要求から「ミス」が生じた場合に、それに応じて、対応するLLC線がアクセスされる。処理405では、LLC線のコヒーレンシ状態情報が保存される。コヒーレンシ状態情報が保存された後、要求がクロス・スヌープをもたらすことになり、CBSOロジックによって取り消し信号が何ら検出されなかった場合に、LLC線が無効にされていると後のトランザクションがみなすことになるようにLLC内の対応する線が処理410でアトミックに無効にされる。処理415で、適切なコア又はプロセッサへのLLCによるクロス・スヌープによって、要求されたデータがコア又はプロセッサから、要求エージェントに戻される。

(もっと読む)

競合しないロック命令の投機実行のための方法及び装置

【課題】アウト・オブ・オーダプロセッサで投機的にロック命令を実行する方法及び装置の提供。

【解決手段】1実施の形態では、所与のロック命令が実際に競合するかについて予測が行われる。競合しない場合、ロック命令は投機的に実行された通常のロードマイクロ動作を有するとして扱われる。モニタロジックは、ロック命令が実際に競合することの示唆を探す。かかる示唆が発見されない場合、投機的なロードマイクロ動作及びロック命令に対応する他のマイクロ動作がリタイアとなる。しかし、かかる示唆が実際に発見された場合、ロック命令が再始動され、予測メカニズムがアップデートされる。

(もっと読む)

マルチプロセッサシステムおよびその制御方法

【課題】キャッシュメモリを有効に活用できるマルチプロセッサシステムおよびマルチプロセッサシステムの制御方法を提供することである。

【解決手段】本発明にかかるマルチプロセッサシステムは、複数のCPU11〜14と、複数のCPU11〜14に対応して設けられた複数のキャッシュメモリ21〜24と、複数のキャッシュメモリ間のキャッシュコヒーレンシを保つスヌープ制御部30と、キャッシュメモリ間のキャッシュコヒーレンシを取らない空間52が割り当てられた共有メモリ50と、を備える。CPUにおいて処理される命令のうち所定のCPUと関連づけられた命令は、当該所定のCPUと関連づけられたキャッシュコヒーレンシを取らない空間52において実行される。

(もっと読む)

マルチコアプロセッサアーキテクチャにおけるデータ記憶およびアクセス

キャッシュに記憶されたデータブロックを送るためのシステムに関する技術が一般に記載されている。本明細書中に記載される幾つかの実施例では、システムが第1のタイルの第1のプロセッサを備えてもよい。第1のプロセッサは、データブロックの要求を発生させるのに有効であり、前記要求がデータブロックのための宛先タイルを識別する宛先識別子を含み、宛先タイルが第1のタイルと異なる。幾つかの実施例のシステムは、要求を受けるのに有効な第2のタイルを更に備えてもよく、第2のタイルは、データブロックを含むデータタイルを決定するのに有効であるとともに、要求をデータタイルへ送るのに有効である。幾つかの実施例のシステムは、第2のタイルから要求を受けるのに有効なデータタイルを更に備えてもよく、データタイルはデータブロックを宛先タイルへ送るのに有効である。  (もっと読む)

(もっと読む)

ドメインベースのキャッシュ・コヒーレンス・プロトコル

簡単にいうと、ドメインベースのキャッシュ・コヒーレンス・プロトコルを用いてキャッシュ内のデータブロックにアクセスするための技術が概説される。第1のタイル、第1のドメインの第1のプロセッサはデータブロックにアクセスするよう求める要求を評価するように構成することができる。第1のドメインの第2のタイルのキャッシュは、データブロックが第2のタイルにキャッシュされているときに、第1のタイルにデータブロックを送るように構成することができる。第1のプロセッサは、キャッシュされた位置が第1のプロセッサのドメインの外部にあるときに、別のドメインの第3のタイルに要求を送るように構成することができる。第3のプロセッサは、データブロックのキャッシュされた位置と関連付けられたデータドメインを判定し、そこに要求を送るように構成することができる。第4のタイルは、要求を受け取り、第1のタイルにデータブロックを送るように構成することができる。  (もっと読む)

(もっと読む)

ローカル物理メモリとリモート物理メモリとの間で共有されるバーチャルメモリのためのハードウェアサポートの提供

【課題】ローカル物理メモリとリモート物理メモリとの間で共有されるバーチャルメモリのためのハードウェアサポートを提供すること。

【解決手段】本発明の一態様は、バーチャルアドレスを含むメモリアクセスリクエストを受信するステップと、前記バーチャルアドレスに対応する物理アドレス(PA)がプロセッサに付属されるローカルメモリ又は非コヒーラントリンクを介し前記プロセッサに接続されるアクセラレータに付属するリモートメモリに存在するか判断するため、前記プロセッサの変換ルックアサイドバッファ(TLB)に格納される前記バーチャルアドレスに対応するエントリを解析するステップと、前記PAが前記リモートメモリに存在する場合、前記メモリアクセスリクエストを実行するため、リバースプロキシ実行リクエストを前記リモートメモリに送信するステップとを有する方法であって、前記ローカルメモリと前記リモートメモリとは、一緒になって共有バーチャルメモリスペースを構成する方法に関する。

(もっと読む)

マルチプロセッサ

【課題】キャッシュラインの転送時の消費電力を低減したマルチプロセッサを提供する。

【解決手段】メインメモリ2と、その記憶データを一時記憶するL1キャッシュメモリ11a〜11dを備える複数のプロセッサユニット1a〜1dと、L1キャッシュメモリ11a〜11dのコヒーレンシを管理するCMU3とを備え、CMU3は、L1キャッシュメモリに格納されたキャッシュラインのタグを格納するL1タグキャッシュ33a〜33dと、プロセッサユニット1a〜1dからのリフィル要求に応じてインターベンション転送を行うCMUコントローラ31と、インターベンション転送を監視することによって、転送先別に転送元を予測するPIU32とを有し、CMUコントローラ31は、PIU32の予測結果が得られた後は、予測された転送元に対応するタグキャッシュのみを活性化して、リフィル要求に対応するキャッシュラインがキャッシュされているかを判別する。

(もっと読む)

二重化情報処理システム及び同期化方法

【課題】ライトバック方式のキャッシュメモリを備えた2台の情報処理システムによって構成される二重化情報処理システムにおいて、通常処理の処理効率を低下させることなく、同期化に要する時間を短縮すると共に、同期化中および同期化後の処理能力を向上させる。

【解決手段】待機系情報処理システム200を二重化情報処理システムに組み込むために、動作系情報システム100と待機系情報処理システム200とを同期化させる際、キャッシュコピー手段300は、ライトバック方式の動作系キャッシュメモリ101の内容をライトバック方式の待機系キャッシュメモリ201にコピーし、主記憶コピー手段400は、動作系主記憶装置102の内容を待機系主記憶装置にコピーする。その後、動作系、待機系CPU103、203がタイミングを合わせて同一の処理を開始する。

(もっと読む)

レイテンシ短縮システム、レイテンシ短縮方法、および、レイテンシ短縮プログラム

【課題】 トラフィックを低減させることが可能なレイテンシ短縮システム、レイテンシ短縮方法、および、レイテンシ短縮プログラムを提供する。

【解決手段】 本発明のレイテンシ短縮システムは、複数のノードを含み、該ノードは、共有メモリと、記憶手段と、登録手段と、送信手段とを備える。登録手段は、複数の発行元から共有メモリの同一アドレスに対して同時にリクエストが発行された場合に、該リクエストを発行した発行元を特定する制御情報を記憶手段に登録する。送信手段は、同時に発行されたリクエストのうち、最初に発行されたリクエストに対して当該リクエストの発行元にデータを返信するとき、当該発行元を制御情報に基づいて決定する。

(もっと読む)

コヒーレンシ制御システム、コヒーレンシ制御装置及びコヒーレンシ制御方法

【課題】 命令実行部からのレベル1キャッシュアクセスのレイテンシを増大させることなく、バストラフィックを抑えてコヒーレンシを保証しようとする場合、ハードウェア量が大きくなるという問題点があった。

【解決手段】 第1の記憶手段のインデックスアドレスを含む論理アドレスを、このインデックスアドレスを含む第2の記憶手段の物理アドレスに変換する論理物理アドレス変換TLBと、ウェイ番号を含むロードリクエストを送信するリクエスト出力部と、受信したロードリクエストに基づいて、第2の記憶手段の領域と第1の記憶手段の領域との関連状態を記憶する対応状態記憶部と、受信したストアリクエストに含まれるタグと対応状態記憶部に記憶されている内容とに基づいて、無効化指示を送信する無効化指示部とを有する。

(もっと読む)

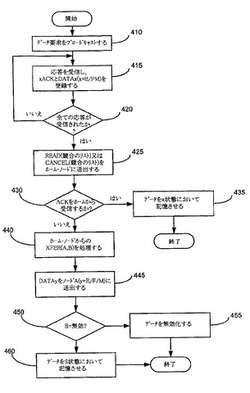

複数ノード間での通信方法、相互接続ポートおよび相互接続システム

【課題】複数のノード間での通信方法を開示する。

【解決手段】各ノードは、複数のプロセッサおよび相互接続チップセットを含み、第1のノード内のプロセッサからデータ要求を発行し、拡張ポート(またはスケーラビリティポート)を通してこのデータ要求を他のノードに渡す。また、データ要求に応答してメモリのアクセスを開始し、各ノード内の各プロセッサのプロセッサキャッシュをスヌープする。従って、該要求を発行するプロセッサを持つノード内の(あるいは別のノードの)プロセッサキャッシュまたはメモリ内のデータの格納場所を識別する。さらに、ルータシステムにて2つの直接結合されたノード間でデータを要求する方法と、相互接続システム内の3またはそれ以上のノード間でのデータ要求方法と、相互接続システム内のクロスケースの解消方法と、ノードを直接またはプロトコルエンジンを通して結合するための相互接続システムも開示する。

(もっと読む)

記憶制御装置及び記憶制御装置の制御方法

本発明の記憶制御装置は、パージメッセージの通信量を低減することができ、記憶制御装置の処理性能を高めることができる。各マイクロプロセッサは、共有メモリ内の制御情報を更新するたびにパージメッセージを作成して保存しておく。一連の更新処理が完了した後で、保存されたパージメッセージを各マイクロプロセッサに送信する。制御情報には、その性質に応じた属性が設定される。その属性に応じてキャッシュ制御及びパージ制御が実行される。  (もっと読む)

(もっと読む)

マルチプロセッサ計算機、キャッシュ整合性の保証方法、及びプログラム

【課題】キャッシュコヒーレンシ保証の際の不必要なキャッシュクリアの回数を抑制して、計算機の性能の向上を図り得る、マルチプロセッサ計算機、キャッシュ整合性の保証方法、及びプログラムを提供する。

【解決手段】メインメモリ4と、プロセッサ10−1〜Nと、キャッシュメモリ2−1〜Nとを備えるマルチプロセッサ計算機11において、メインメモリ4は、情報を資源10−1〜Mとして記憶し、各プロセッサは、一のプロセッサがある資源に対して排他的制御によってアクセスするときに、アクセス対象の資源を最後に更新したプロセッサを特定する情報を用い、アクセス対象の資源が最後に更新された時刻t1と、アクセス対象の資源を最後に更新したプロセッサのキャッシュメモリがクリアされた最新の時刻t2と、一のプロセッサのキャッシュメモリがクリアされた最新の時刻t3との関係に基づいて、キャッシュメモリをクリアする。

(もっと読む)

分散キャッシュシステム、方法、プログラム、及び計算ノード

【課題】分散キャッシュシステムの目標性能が達成されるように、複数の計算ノード間のキャッシュコンシステンシを自動的に制御すること。

【解決手段】複数の計算ノードは、ブロック単位でデータキャッシュを行う。各計算ノードは、コピーブロックとメタ情報が格納される記憶装置と、キャッシュ制御部と、転送量算出部とを備える。メタ情報は、コピーブロックのステータスとアクセス履歴情報とを含む。第1計算ノードは、第1ブロックに対するライトアクセスを受け取る。転送量算出部は、第1コピーブロックに関連付けられたメタ情報に含まれるアクセス履歴情報を参照して、計算ノード間で将来発生する第1コピーブロックの転送量を算出する。キャッシュ制御部は、目標性能と算出された転送量に基づいて、コンシステンシを緩和するか否かを決定する。コンシステンシを緩和する場合、第1コピーブロックをキャッシュしている他の計算ノードにおいて、第1コピーブロックのステータスは変更されない。

(もっと読む)

マルチプロセッサシステム

【課題】プロセッサコアの違反アクセスを効率よく検出する。

【解決手段】マルチプロセッサシステム10は、複数のプロセッサコア11に対応して設けられた複数のキャッシュシステム21を含む。キャッシュシステム21は、キャッシュラインとこのライン情報とを格納するキャッシュメモリ22を含む。キャッシュシステム21は、ライン情報と、アービタから送られるアクセス要求とを比較して違反アクセスを検出する違反検出回路24と、違反検出回路24による検出結果に基づいてキャッシュラインごとにフラグをセットし、かつプロセッサコア11に保持されたキャッシュラインに読み出しアクセス又は書き込みアクセスする際にフラグの内容を確認し、このフラグの内容に基づいて違反アクセスを検出するフラグ制御回路とを含む。

(もっと読む)

シーケンシャル・プログラムを複数スレッドに分解し、スレッドを実行し、シーケンシャルな実行を再構成するシステム、方法および装置

シーケンシャルなプログラムを複数のスレッドに分解し、これらのスレッドを実行し、スレッドのシーケンシャルな実行を再構成するためのシステム、方法および装置が記載される。複数のデータ・キャッシュ・ユニット(DCU)が、投機的に実行されるスレッドのローカルにリタイアされた命令を記憶する。マージング・レベル・キャッシュ(MLC)が、DCUのラインからのデータをマージする。コア間メモリ整合性モジュール(ICMC)が、MLC内の投機的に実行されたスレッドの命令をグローバルにリタイアさせる。  (もっと読む)

(もっと読む)

部分書込と非スヌープアクセスとの間のメモリ順序付け要件の充足

【課題】部分的且つ非コヒーレントなメモリアクセスの観点からキャッシュ・コヒーレンス・リンクに基づく相互接続でメモリ順序付けを保つ方法及び装置を提供する。

【解決手段】例えば部分書込のような部分的なメモリアクセスに関連するコンフリクトが検出される場合に、ライトバックフェーズがコンフリクトフェーズで挿入され、ホームエージェントへ部分的データをライトバックする。コンフリクトフェーズでライトバックフェーズを挿入するメッセージの例には、コンフリクトを認めて、コンフリクトフェーズの開始時にライトバックマーカーを、コンフリクトフェーズ前にライトバックマーカーメッセージを、コンフリクトフェーズ内でライトバックマーカーメッセージを、コンフリクトフェーズ後にライトバックマーカーメッセージ及びポスタブル・メッセージを提供するAcknowledge Conflict Write-backメッセージがある。

(もっと読む)

1 - 20 / 96

[ Back to top ]