Fターム[5B005RR01]の内容

階層構造のメモリシステム (9,317) | 変換制御 (263) | アドレス変換 (251)

Fターム[5B005RR01]の下位に属するFターム

変換テーブル (187)

Fターム[5B005RR01]に分類される特許

1 - 20 / 64

アドレス変換装置、アドレス変換装置の制御方法及び演算処理装置

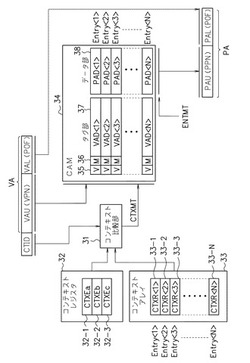

【課題】プロセス(コンテキスト)の切り替え時にエントリを無効化せずとも、アドレス変換に係る検索を適切なエントリだけを対象として行えるアドレス変換装置を提供する。

【解決手段】アクセス要求したプロセスのコンテキストとエントリのコンテキストとが一致すると判定された場合にオンとされるマッチフラグ36をエントリ毎に設け、アクセス要求で指定された仮想アドレスVAを物理アドレスPAに変換する場合に、マッチフラグ36がオンであるエントリだけを対象としてアドレス変換に用いるエントリを検索する。アクセス要求したプロセスのコンテキストに対応するものでないエントリのマッチフラグ36はオフされるので、プロセス(コンテキスト)の切り替え時にエントリを無効化しなくとも、アクセス要求したプロセスのコンテキストに対応するエントリだけを対象とした検索が可能となる。

(もっと読む)

アドレス変換方法及び装置

【課題】メモリの中の異なるページの間の境界クロシングの原因となるアドレスを識別し、プロセッサ内でのアドレス変換性能を改善する。

【解決手段】プロセッサは、第1及び第2のメモリページの間のページ境界をクロスするメモリ領域へのアクセスを認識するように構成される回路を備える。回路は、また、第1及び第2のメモリページと関連するアドレス変換情報をリンクするように構成される。このように、同一のメモリ領域へのその後のアクセスに応答して、第1及び第2のメモリページと関連するアドレス変換情報は、1つのアドレス変換に基づいて検索可能である。

(もっと読む)

パーティション分割されたシステムにおいて、デバイスがメモリにアクセスするための、ゲスト・アドレスからホスト・アドレスへの変換

【課題】パーティション分割されたシステムの仮想化機能を向上させる。

【解決手段】装置がインターフェース、パーティション分割論理190、第一のアドレス変換論理131および第二のアドレス変換論理132を含む。インターフェースがパーティション分割されたシステムにおいてメモリにアクセスする要求をデバイスから受け取る。パーティション分割論理190は、前記デバイスが第一のパーティションに割り当てられているか、第二のパーティションに割り当てられているかを判別する。第一のアドレス変換論理131は、第一のパーティション内の第一のゲスト・アドレスを第一のホスト・アドレスに変換する。第二のアドレス変換論理132は、第二のパーティション内の第二のゲスト・アドレスを第二のホスト・アドレスに変換する。

(もっと読む)

情報処理装置、メモリ制御装置、メモリアクセス方法およびプログラム

【課題】複数のバンクにアクセスする場合にキャッシュメモリを効率よく利用する。

【解決手段】キャッシュメモリ120は、複数のバンクを備えるメモリ200の一部の領域に保持されているデータをエントリ単位で保持する。バスマスタ110は、複数のバンクに保持されている同一データへのアクセス要求を行う場合には、1つのアクセスアドレスを発行する。この発行により、キャッシュメモリ120には、同一データが保持されている複数のバンクにおける各メモリアドレスに対応する1つのエントリのみが登録される。メモリコントローラ130は、バスマスタ110からアクセスアドレスが発行された場合には、そのアクセスアドレスに基づいて、同一データが保持されている複数のバンクにおける各メモリアドレスを特定する。そして、その特定された各メモリアドレスのうちの1つのメモリアドレスにアクセスする。

(もっと読む)

仮想計算機の制御方法

【課題】複数サーバで構成されるNUMA(Non-Uniform Memory Access)構成やSMP(Symmetric Multi Processing)構成では、ひとつのLPARが使用するメモリ領域が複数サーバのDIMMに分散されることがあり、CPUのメモリアクセスにおいて性能を低下させていた。

【解決手段】 ハイパバイザが、ローカルメモリとリモートメモリとCPUとの配置関係を管理するメモリモジュール配置情報に基づき、各仮想計算機に割当てたCPUと各仮想計算機に割当てたメモリモジュールとの配置関係を検知する。仮想計算機に割当てられたCPUにとってリモートメモリとなる仮想計算機を停止し、停止させた仮想計算機に割当てられていたリモートメモリとなるメモリモジュールに記憶されている情報を、ローカルメモリに移動させる。

(もっと読む)

バス変換回路

【課題】各制御装置から各カードにアクセスできるアドレス空間領域の大きさを制御装置の数に依存せずに維持したまま、競合を回避する制御手順を省略し、カード制御にかかる時間を短縮することができるバス変換回路を実現する。

【解決手段】複数の制御装置が接続される第1のバスとこの第1のバスとは異なる種類の第2のバスとの間に配置され、第1のバスを介して入力された制御装置からのパケットに含まれる第1のアドレスを第2のバスの第2のアドレスに変換するバス変換回路において、制御装置毎に第2のバスのベースアドレスを記憶し、パケットに含まれる制御装置を特定する固有値に応じて、制御装置に対応したベースアドレスを用いて第1のアドレスを第2のバスの第2のアドレスに変換する。

(もっと読む)

仮想アドレスキャッシュメモリ、プロセッサ及びマルチプロセッサシステム

【課題】TLBの機能をキャッシュメモリ上で実現して、回路量の削減を図ることができ、さらにタスク切り替えの応答性が向上したプロセッサを提供する。

【解決手段】仮想アドレスキャッシュメモリは、TLBの書き換えが発生したときにエントリデータの書き換えを行うTLB仮想ページメモリ21と、仮想ページタグ又はページオフセットをキャッシュインデックスとしてキャッシュデータを保持するデータメモリ23と、キャッシュインデックスに対応して前記データメモリに記憶された前記キャッシュデータのキャッシュステートを保持するキャッシュステートメモリ24と、TLBの書き換えが発生したときに、保持している物理アドレスの書き換えを行う第1の物理アドレスメモリ22と、TLBの書き換えの発生後、データメモリへの前記キャッシュデータを書き込むときに保持している物理アドレスの書き換えを行う第2の物理アドレスメモリ25とを有する。

(もっと読む)

ローカル物理メモリとリモート物理メモリとの間で共有されるバーチャルメモリのためのハードウェアサポートの提供

【課題】ローカル物理メモリとリモート物理メモリとの間で共有されるバーチャルメモリのためのハードウェアサポートを提供すること。

【解決手段】本発明の一態様は、バーチャルアドレスを含むメモリアクセスリクエストを受信するステップと、前記バーチャルアドレスに対応する物理アドレス(PA)がプロセッサに付属されるローカルメモリ又は非コヒーラントリンクを介し前記プロセッサに接続されるアクセラレータに付属するリモートメモリに存在するか判断するため、前記プロセッサの変換ルックアサイドバッファ(TLB)に格納される前記バーチャルアドレスに対応するエントリを解析するステップと、前記PAが前記リモートメモリに存在する場合、前記メモリアクセスリクエストを実行するため、リバースプロキシ実行リクエストを前記リモートメモリに送信するステップとを有する方法であって、前記ローカルメモリと前記リモートメモリとは、一緒になって共有バーチャルメモリスペースを構成する方法に関する。

(もっと読む)

プロセス状態検知プログラム、情報処理装置、プロセス状態検知方法

【課題】プログラムの生成、消滅の状態を判定することができるプログラム状態検知プログラムを提供する。

【解決手段】プログラムの切替えの際にオペレーティングシステムがトランスレーション・ルックアサイド・バッファの無効化を計測でき、無効化があると割り込みを発生させる機構を持つCPUを有するコンピュータに、プログラムの識別情報をオペレーティングシステムから取得してリストに記憶し、プログラムの切替えが生じた場合に発生する、CPUからの割り込みを検知した場合、オペレーティングシステムまたは機構から切替え先のプログラムの識別情報を取得し、リストと取得した識別情報を比較して、切替え先のプログラムが生成または消滅されるプログラムであるかを判定する処理を実行させるためのプログラム状態検知プログラムを提供する。

(もっと読む)

コンピュータのメモリを参照する方法およびコンピュータ

【課題】第1および第2の命令セットの命令を実行するコンピュータを提供する。

【解決手段】プログラムは、第1および第2の命令セットの命令でコード化され、第1および第2のデータ記憶規約を使用する。スイッチは、各テーブルエントリに記憶された第1のフラグ値に応答し、命令のメモリページに対応するテーブルエントリの第1のフラグ値による指示に従って代替的に第1または第2の命令セットのもとで命令を解釈するように命令プロセッサ100を制御する。遷移ハンドラは、プログラム実行が第1のデータ記憶規約を使用する命令のページから第2のデータ記憶規約を使用する命令のページに移行した時を、各ページに対応するテーブルエントリに記憶された第2のフラグ値による指示に従って認識し、コンピュータのデータ記憶構成を第1の記憶規約から第2のものに調整する。履歴記録は、最近実行された命令の分類の記録を遷移ハンドラに提供する。

(もっと読む)

演算処理装置およびアドレス変換方法

【課題】TLBの実装効率を小さくした演算処理装置およびアドレス変換方法を提供すること。

【解決手段】アドレス変換バッファのTLB本体部をRAMで構成し、RAM上にセットアソシアティブ方式のTLBに加えてフルアソシアティブ方式のTLBを登録する。アドレス変換時には、まず、セットアソシアティブ方式のTLBから検索し、ヒットしなかった場合にフルアソシアティブ方式のTLBの検索を行なう。フルアソシアティブ方式のTLBでの検索時には、エントリを順次参照する。

(もっと読む)

無制限トランザクショナルメモリ(UTM)システムの最適化

【解決手段】 本明細書では無制限トランザクショナルメモリ(UTM)システムを最適化する方法および装置を説明する。監視部、バッファリング、および、メタデータについてのハードウェアサポートが提供され、メタデータのメタフィジカルアドレス空間は、互いに直交し、スレッドおよび/またはスレッド内のソフトウェアサブシステムとそれぞれ対応付けられるとしてよい。また、メタデータは、ソフトウェアに対してトランスペアレントなデータに対して圧縮した状態でハードウェアで保持するとしてよい。さらに、メタデータアクセス命令/処理に応じて、ハードウェアは、さまざまなモードでのトランザクション的な実行を可能にするための強制メタデータ値をサポートできる。しかし、監視部、バッファリングされたデータ、メタデータあるいはその他の情報が失われたり、または、コンフリクトが検出されると、ハードウェアは、このような損失またはコンフリクトに関してトランザクションステータスレジスタをポーリングして、損失またはコンフリクトを検出することに応じて実行をラベルにジャンプさせることができる損失命令のさまざまなバージョンを提供する。同様に、ソフトウェアにコミット条件およびコミット時にクリアすべき情報を定義させるために、さまざまなバージョンのコミット命令を提供する。また、ハードウェアサポートは、リングレベルの遷移が発生するとトランザクションの一時停止および再開を可能とする。 (もっと読む)

コヒーレンシ制御システム、コヒーレンシ制御装置及びコヒーレンシ制御方法

【課題】 命令実行部からのレベル1キャッシュアクセスのレイテンシを増大させることなく、バストラフィックを抑えてコヒーレンシを保証しようとする場合、ハードウェア量が大きくなるという問題点があった。

【解決手段】 第1の記憶手段のインデックスアドレスを含む論理アドレスを、このインデックスアドレスを含む第2の記憶手段の物理アドレスに変換する論理物理アドレス変換TLBと、ウェイ番号を含むロードリクエストを送信するリクエスト出力部と、受信したロードリクエストに基づいて、第2の記憶手段の領域と第1の記憶手段の領域との関連状態を記憶する対応状態記憶部と、受信したストアリクエストに含まれるタグと対応状態記憶部に記憶されている内容とに基づいて、無効化指示を送信する無効化指示部とを有する。

(もっと読む)

仮想マシンシステムにおけるショートカット入出力

【解決手段】一般的にアクセスされるストレージボリュームに対する読み出し要求は、要求されたデータブロックが以前のアクセスからメモリ内に既に格納されているか、又は保留の要求が終了次第メモリ内に格納されるか否かに依存し、条件付きで発行される。データ構造は、物理メモリページを追跡し、かつ、そこから物理メモリの内容が読み出されたストレージボリューム内の対応する位置及びそれにマッピングされた仮想メモリページの数を、各物理メモリページに示すために、メモリにおいて保持される。 (もっと読む)

共有メモリ仮想化装置、および共有メモリ仮想化方法

【課題】共有メモリなどメモリ空間の特性を前提としたプログラミングが可能なプラットフォームで設計されたアプリケーションプログラムを他のプラットフォームにプログラム設計を見直すことなく容易に移植することができる、共有メモリ仮想化装置を提供する。

【解決手段】特定のアドレス位置を共有メモリと想定して設計されたアプリケーションプログラム11を、プラットフォーム(実行環境21)に移植するために、アプリケーションプログラム11が、所望のメモリリージョンの特性を共有メモリとすることを指定するためのコンフィグレーションレジスタ31と、コンフィグレーションレジスタ31により指定される共有メモリのメモリリージョンの論理アドレスを、プラットフォームに固有の共有メモリ51のメモリリージョンの論理アドレスに変換するアドレス変換ライブラリ41と、を備える。

(もっと読む)

メモリ管理システム、メモリ管理方法及びプログラム

【課題】主記憶装置に格納されていない仮想ブロックがアクセスされた時点において、アクセスされた仮想ブロックについては割り当てる物理ブロックを決定する処理とその物理ブロックを初期化する処理とを行い、その仮想ブロックを含む複数の仮想ブロックについては割り当てる物理ブロックを決定する処理だけを行えるようにする。

【解決手段】主記憶部31に格納されていない仮想ブロックがアクセスされると、メモリ割り当て部14は、マッピングテーブル部12を参照して上記仮想ブロックに割り当てる物理ブロックが決定されているか否かを調べ、決定されていない場合は、アクセス対象の仮想ブロックを含む複数の仮想ブロックについて、その仮想ブロックに割り当てる物理ブロックを決定し、その情報をマッピングテーブル部12に登録する。そして、物理ブロックの初期化処理は、アクセス対象の仮想ブロックに割り当てた物理ブロックについてのみ行なう。

(もっと読む)

メモリ管理装置及び画像形成装置

【課題】 画像形成装置において、大容量の画像データ等を扱うための連続した大容量のメモリ空間の確保を容易にすること。

【解決手段】 従来の仮想メモリシステムでは、OSがメモリ空間を管理するために、取得するメモリの容量制限やOS管理におかれたメモリ取得・解放動作によって引き起こされたフラグメンテーション等により、連続した大容量のメモリを取得することが困難であったが、物理メモリ空間をOS管理領域とOS非管理領域に分けて仮想メモリ空間に割当て前記OS非管理領域へのアプリケーションプログラムからのアクセスを可能とするOS非管理メモリ領域管理部を有することにより課題を解決した。さらに、OSメモリ領域管理部はウィンドウ領域を経由して、デバッグ用途などでのカーネルから非管理領域へのアクセスも可能となる。

(もっと読む)

データキャッシュとメインメモリ間の一貫性の保証

プロセッサコア、複数のスレッドの各々によってアクセス可能なデータを記憶するキャッシュメモリ、複数のスレッドによってアクセス可能なデータを記憶するメインメモリ、非一貫性検出モジュール、及びメモリアービターを含み、複数のスレッドをサポートするマルチスレッドプロセッサにおいてメモリアクセスを制御するための装置を提供し、非一貫性検出モジュールは、プロセッサコアとメモリアービターの間に接続され、メモリアービターは、非一貫性検出モジュールとメインメモリの間に接続され、キャッシュメモリからメモリアービターに送信された読取及び書込要求に対する各スレッドのための個別の要求待ち行列が存在し、使用においては、非一貫性検出モジュールは、キャッシュメモリからメインメモリに送信された各書込要求に対するメモリアドレスの指示を書込アドレスメモリに記憶し、更に、キャッシュメモリから送信された各次の読取要求のアドレスを書込アドレスメモリ内の指示と比較し、次の読取要求のアドレスが指示に適合した場合に、読取要求に対応する障壁を適合指示が属するスレッドの要求待ち行列内に挿入し、メモリアービターは、対応する障壁がメモリアービターによって受信されるまで読取要求がメモリバスにアクセスしないように阻止する。 (もっと読む)

マルチプロセッサシステム

【課題】複数のプロセッサが周辺装置を共有しても、当該周辺装置に割り当てられたアドレス空間の重複に起因する誤動作を確実に防止し得るマルチプロセッサシステムを提供する。

【解決手段】マルチプロセッサシステム1は、複数のプロセッサとバスを介して接続されたアドレス変換部35を有する。アドレス変換部35は、複数のプロセッサのうちアクセス要求を発したプロセッサからのアドレス情報を共有メモリ空間内のアドレス情報に変換する。共有メモリ空間は、複数のプロセッサにそれぞれ対応する複数のアドレス領域を有している。アドレス変換部35は、アクセス要求を発した当該プロセッサからのアドレス情報を、当該プロセッサに対応する当該アドレス領域内のアドレス情報に変換する。

(もっと読む)

メモリ管理装置及び画像形成装置

【課題】 画像形成装置において、大容量の画像データ等を扱うための連続した大容量のメモリ空間の確保を容易にすること。

【解決手段】 従来の仮想メモリシステムでは、OSがメモリ空間を管理するために、取得するメモリの容量制限やOS管理におかれたメモリ取得・解放動作によって引き起こされたフラグメンテーション等により、連続した大容量のメモリを取得することが困難であったが、物理メモリ空間をOS管理領域とOS非管理領域に分けて仮想アドレス空間に割当て、前記OS非管理領域へのアプリケーションプログラムからのアクセスを可能とするOS非管理メモリ領域管理部を有することにより課題を解決した。

(もっと読む)

1 - 20 / 64

[ Back to top ]