Fターム[5B005TT02]の内容

階層構造のメモリシステム (9,317) | 写像 (155) | 連想写像 (128) | セット連想写像 (120)

Fターム[5B005TT02]に分類される特許

1 - 20 / 120

半導体記憶装置

ソフトエラー耐性調整機能を備えた電子システム装置及びソフトエラー耐性調整方法

アドレス変換装置、アドレス変換装置の制御方法及び演算処理装置

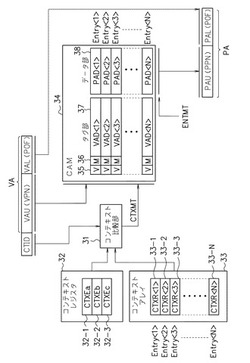

【課題】プロセス(コンテキスト)の切り替え時にエントリを無効化せずとも、アドレス変換に係る検索を適切なエントリだけを対象として行えるアドレス変換装置を提供する。

【解決手段】アクセス要求したプロセスのコンテキストとエントリのコンテキストとが一致すると判定された場合にオンとされるマッチフラグ36をエントリ毎に設け、アクセス要求で指定された仮想アドレスVAを物理アドレスPAに変換する場合に、マッチフラグ36がオンであるエントリだけを対象としてアドレス変換に用いるエントリを検索する。アクセス要求したプロセスのコンテキストに対応するものでないエントリのマッチフラグ36はオフされるので、プロセス(コンテキスト)の切り替え時にエントリを無効化しなくとも、アクセス要求したプロセスのコンテキストに対応するエントリだけを対象とした検索が可能となる。

(もっと読む)

キャッシュ装置、メモリシステム及びデータ転送方法

【課題】キャッシュデータを効率的にメインメモリへライトバックすることができるキャッシュ装置、メモリシステム及びデータ転送方法を提供すること

【解決手段】本発明にかかるキャッシュ装置は、複数のキャッシュデータが、メインメモリ80に格納されている複数のデータと一致しているか否かを判定するライトバック制御部60と、複数のキャッシュデータのうち、不一致と判定されたキャッシュデータであって、メインメモリ80において連続するアドレスへ書き込まれる複数のキャッシュデータを格納するデータバッファ部13と、データバッファ部13へ格納されたキャッシュデータを一括してメインメモリ80へ書き込むメモリライト部14と、を備えるものである。

(もっと読む)

演算処理装置

【課題】キャッシュメモリから高速にデータを読み出すことができる演算処理装置を提供することを課題とする。

【解決手段】演算処理装置は、複数の記憶素子にそれぞれ複数のデータを記憶するキャッシュメモリと、前記キャッシュメモリからデータが読み出されたタイミングが閾値より遅いときにはエラーを検出するエラー検出回路(500)と、前記エラーが検出されないときには前記キャッシュメモリから読み出されたデータをラッチし、前記エラーが検出されたときには待機期間経過後に前記キャッシュメモリから読み出されたデータをラッチするラッチ回路(517)と、前記ラッチ回路によりラッチされたデータの処理を行う演算処理装置コアとを有する。

(もっと読む)

制御システム、制御方法およびプログラム

【課題】消費電力量を低減可能な制御システム、制御方法およびプログラムを提供する。

【解決手段】制御システム100は、検出部51と推定部52と判断部53と制御部54とを備える。検出部51はアイドル状態を検出する。推定部52はアイドル時間を推定する。判断部53は、アイドル状態が検出された場合、主記憶装置への書き戻しが必要なデータの書き戻しを行ってキャッシュメモリに対する電力の供給を停止した場合の第1消費電力量が、当該データの書き戻しを行わずにアイドル時間にわたってキャッシュメモリに対する電力の供給を継続した場合の第2消費電力量よりも大きいか否かを判断する。制御部54は、第1消費電力量が第2消費電力量よりも小さいと判断された場合は、キャッシュメモリに対する電力供給を停止させる一方、第1消費電力量が第2消費電力量よりも大きいと判断された場合は、キャッシュメモリに対する電力供給を継続させる。

(もっと読む)

キャッシュメモリ装置、プロセッサ、および情報処理装置

【課題】十分な消費電力の削減が図ることができるキャッシュメモリ装置を提供する。

【解決手段】キャッシュメモリ装置100aは、記憶装置のデータをキャッシュする。キャッシュメモリ装置100aは、記憶部110aと、制御部120aと、を備える。記憶部110aは、複数のキャッシュラインを有する。制御部120aは、前記複数のキャッシュラインのうち、前記記憶装置に書き込まれていないデータを含むダーティラインの数が予め定めた所定数を超える場合に、前記ダーティラインのデータを前記記憶装置に書き込む。

(もっと読む)

キャッシュメモリの最大レジデンシー交換のための方法およびシステム

【課題】キャッシュメモリの複数のセットウエイのレジデンシーを最大にするようにキャッシュメモリアロケーションを交換する方法を提供する。

【解決手段】ビクティムウエイのファーストイン、ファーストアウト(FIFO)交換リストを形成する。FIFO交換リストの深さは、キャッシュセット内の数にほぼ等しい。タグミスアロケーションを生じた場合にのみビクティムウエイをFIFO交換リスト上に配置する。ビクティムウエイは任意の以前に選択されたビクティムウエイの後でFIFO交換リストのおわりに配置される。ビクティムウエイのイニシャルアロケーションが完了するまで引き止めておくことにより、またはビクティムウエイのイニシャルアロケーションが完了するまで再使用リクエストをリプレイ(replay)することによりビクティムウエイの不完全な先のアロケーションの場合にFIFO交換リスト上のビクティムウエイの使用が防止される。

(もっと読む)

ノーマル割り当てからの干渉がないキャッシュロッキング

【課題】キャッシュエントリの割り当てを制限するキャッシュロックの方法を提供する。

【解決手段】ブロック・ノーマル・キャッシュ割り当て(BNCA)が定義される。BNCAモードにおいて、キャッシュエントリは予め決められた命令によってのみ割り当てられる。ノーマルメモリアクセス命令(例えば、割込コードの部分として)が実行し、キャッシュミスの場合はメインメモリからデータを検索するが、キャッシュエントリの割り当てを許されない。予め決められた命令(例えば、ロックされるキャッシュエントリの確立のために使用される命令)だけがキャッシュエントリを割り当てることができる。ロックされるエントリが確立されると、プロセッサはBNCAモードを抜け、いかなるメモリアクセス命令もキャッシュエントリを割り当てることができる。BNCAモードは、構成レジスタ中の1ビットをセットすることによって指示できる。

(もっと読む)

キャッシュメモリ、及びキャッシュメモリの駆動方法

【課題】低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供する。

【解決手段】キャッシュメモリが有するメモリセット内の1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つメモリセットに対に設けられる比較回路にデータを出力可能な構成とすればよい。

(もっと読む)

データ処理システムのシステムメモリへのデータの書き込み

【課題】システムメモリへのデータの書き込みの際の遅延を減少させる方法およびシステムを提供する。

【解決手段】システムメモリの領域のユニークなセクションに各々関連する複数のキャッシュ線に対応する状態インジケータは、キャッシュ線が関連するセクションにそのキャッシュ線に格納されているデータを書き込む候補であることを示すダーティ指示を含む。ダーティ指示を含む状態インジケータの数を判定し、判定したダーティ指示の数が閾値を超える場合、キャッシュ線を選択し、そのキャッシュ線に格納されているデータをシステムメモリの領域の関連するセクションに書き込み、対応する状態インジケータにクリーン指示を格納する。クリーン指示によって、キャッシュ線がシステムメモリの領域の関連するセクションにそのキャッシュ線に格納されているデータを書き込む候補でないことが識別される。

(もっと読む)

キャッシュメモリおよびキャッシュシステム

【課題】キャッシュメモリの面積の増大を抑制しつつ、高速化する。

【解決手段】キャッシュメモリ2はタグメモリ103と、第1のダーティビットメモリ106と、有効ビットメモリ107と、データメモリ105と、を含む複数のキャッシュラインを有する複数のウエイを備える。また、キャッシュメモリ2は、前記キャッシュラインを特定するためのラインインデックスメモリ101を備える。また、キャッシュメモリ2は、前記ウエイを特定する第1のビットデータおよび前記ラインインデックスを特定する第2のビットデータを記憶するローメモリ202と、前記データメモリへのバイト単位のライトに対応したビット単位の第2のダーティビットを記憶する第2のダーティビットメモリ203と、登録された順番を規定するFIFO情報を記憶するFIFOメモリ204と、を含む複数のラインを有するDBLBシステム201と、を備える。

(もっと読む)

プログラマブルコントローラ

【課題】ラダー言語用のビット演算プロセッサを備えるプラグラマブルコントローラにおいて多発する、リードモディファイライトによるパイプライン処理の中断を防ぐ。

【解決手段】リードモディファイライトの対象データをバッファレジスタにロードするとともに対象データのアドレスをレジスタファイル152に保持しておくパイプラインステージR(リードステージ)の後ろに、ビット演算及びビットデータのマージを行うパイプラインステージEX(実行ステージ)を設け、その後ろにリードステージRにて保持したアドレスにマージ結果をストアするパイプラインステージW(ライトステージ)を設ける。

(もっと読む)

共有されるL2マッピング・キャッシュのための対称的割り当てのための方法およびシステム

【課題】タイル式メモリからデータを読み取るための方法、装置、システムおよび媒体を提供する。

【解決手段】一つのタイル式X方式キャッシュ読み取り要求について、そのタイル式X方式キャッシュ読み取り要求を分解することなくタイル式メモリから二つのキャッシュ・ラインを要求する段階305と、二つの要求されたキャッシュ・ラインに関連付けられたデータを返す段階325とを含む。また、二つのキャッシュ・ラインを並列に割り当てる段階310と、二つのキャッシュ・ラインの整合性を並列に維持する段階315と、二つのキャッシュ・ラインに関連付けられたデータをデータ・キャッシュから並列に読む段階320を含む。

(もっと読む)

キャッシュメモリ

【課題】アクセス時間を短縮する効果を得つつ、消費電力を低減することを目的とする。

【解決手段】キャッシュメモリ1は、セット番号が複数のグループに分けられ、そのグループ毎にタグメモリブロックを有するとともに、各タグメモリブロック内にそのグループに属するセット番号毎に複数の領域からなるタグアレイを有するタグメモリ7と、前記グループ毎にデータメモリブロックを有するとともに、各データメモリブロック内にそのグループに属するセット番号毎に複数の領域からなるデータアレイを有するデータメモリ8とを備える。キャッシュメモリ1は、要求されたデータのセット番号が属するタグメモリブロックの各領域とデータメモリブロックの各領域とから並列してデータを読み出す。

(もっと読む)

キャッシュメモリ装置、プログラム変換装置、キャッシュメモリ制御方法及びプログラム変換方法

【課題】性能の劣化を抑制するとともに、消費電力の増加を抑制することができるキャッシュメモリ装置を提供する。

【解決手段】複数のプログラムを切り替えながら実行するプロセッサ部200に接続されるキャッシュメモリ装置100であって、タグ格納部及びデータ格納部を含む複数のウェイを備えるセットアソシアティブ方式のキャッシュメモリ110と、複数のウェイのうちのヒットするウェイを予測するウェイ予測部120と、クロック制御部113とを備え、クロック制御部113は、第1メモリアクセス命令がプロセッサ部200で解読された場合に、ウェイ予測部120によって予測されたウェイのデータ格納部のみにクロックを供給し、第2メモリアクセス命令がプロセッサ部200で解読された場合に、ウェイ予測部120による予測結果に関わらず、予め定められたデータ格納部にクロックを供給する。

(もっと読む)

計算機システム

【課題】高速化による性能向上、および機能ごとの独立性能設計の容易化を実現しつつ、大容量のキャッシュメモリの搭載を必要としない計算機システムを提供する。

【解決手段】主記憶装置101と、複数の仮想プロセッサ上で実行される処理を逐次実行する処理実行部111と、複数の仮想プロセッサ間で共用される1次キャッシュメモリ113と、仮想プロセッサのプロセッサ数に応じて分割された複数の記憶領域を有し、各仮想プロセッサに各記憶領域が対応付けられ、各記憶領域が、当該記憶領域に対応付けられた仮想プロセッサが利用するデータを記憶する2次キャッシュメモリ107と、仮想プロセッサごとのコンテキストを記憶しているコンテキストメモリ103と、仮想プロセッサのコンテキストの退避及び復帰を行う仮想プロセッサ制御部104と、1次キャッシュ制御部112と、2次キャッシュ制御部106とを備える。

(もっと読む)

記憶効率の高いセクタ化されたキャッシュ

情報処理装置

【課題】アプリケーションに応じて自動的にウェイ数を適切に増減し、キャッシュの利用効率やヒット率を改善する。

【解決手段】データに処理を施す処理部とデータが記憶されているメモリとの間に設けられ、メモリのデータがコピーされる複数のデータアレイと複数のデータアレイにおけるウェイの古さ順を示す情報を保持する情報アレイとを有するキャッシュ部を備え、複数のデータアレイの各々はウェイ数が1以上であって、そのうち少なくとも1つはエントリ数が異なり、分割されたメモリの記憶領域に対し、複数のデータアレイにてそれぞれ1つのエントリが割り当てられるようにして、実行するアプリケーションに応じてエントリ単位で動的にウェイ数を増減し最適なウェイ数に自動で変更することができるようにする。

(もっと読む)

キャッシュメモリ

【課題】キャッシュ全体のヒット率を向上させるキャッシュメモリを提供することを課題とする。

【解決手段】キャッシュメモリにおいて、キャッシュメモリに登録されているデータに優先度を付与する優先度付与手段10と、キャッシュメモリに設けられ、優先度に基づいて入れ替え対象のデータが選択される優先度有効領域12と、キャッシュメモリに設けられ、優先度に関係なく入れ替え対象のデータが選択される優先度無効領域11と、データを優先度無効領域11に登録するときに、優先度無効領域11にデータを追加登録することによって入れ替えられるデータの優先度と優先度有効領域12に登録されているデータの優先度とを比較し、当該比較結果に基づいて入れ替えられるデータを優先度有効領域12に登録するか否かを判定する判定手段10を備えることを特徴とする。

(もっと読む)

1 - 20 / 120

[ Back to top ]