Fターム[5B013AA11]の内容

Fターム[5B013AA11]に分類される特許

1 - 20 / 104

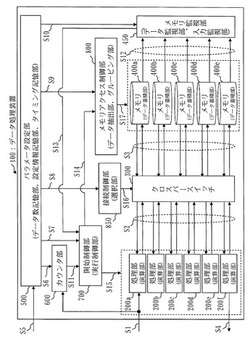

データ処理装置およびデータ処理方法およびプログラム

【課題】演算部の演算開始タイミングを変化させてデータ処理を行うデータ処理装置を実現する。

【解決手段】メモリ400aは、先行して演算を実行する処理部200aが生成したデータを蓄積する。メモリ監視部450は、メモリ400aが蓄積するデータのデータ数を監視し、後続して演算を実行する処理部200bが演算に必要なデータ数が蓄積されたら、メモリ400aが蓄積するデータを処理部200bに出力させる。処理部200bはデータが出力されるタイミングで演算を開始し、データが出力されるタイミングの変化に対応して、処理部200bの演算開始タイミングが変化する。

(もっと読む)

プロセッサインストラクションの発行の絞り込み

【課題】選択された問題のあるインストラクションの発行を絞り込むことにより電力消費を減少するためのシステム及び方法を提供する。

【解決手段】プロセッサ内の電力スロットルユニットは、高電力消費推定値に基づいて選出される関連インストラクション形式に対するインストラクション発行カウントを維持する。電力スロットルユニットは、所与のインストラクション発行カウントが所与のスレッシュホールドを越えることを決定する。それに応答して、電力スロットルユニットは、各発行レートを制限するための所与のインストラクション形式を選択する。電力スロットルユニットは、その選択された所与のインストラクション形式の各々に対する発行レートを選出し、そしてその関連発行レートを、選出された発行レートに制限する。所与のインストラクション形式及び関連発行レート限界の選択は、プログラム可能である。

(もっと読む)

マルチスレッドプロセッサ

【課題】従来のマルチスレッドプロセッサでは、ハードウェアスレッドの最低実行時間を保証しながら、柔軟なハードウェアスレッドの選択ができない問題があった。

【解決手段】本発明のマルチスレッドプロセッサは、複数のハードウェアスレッドと、優先順位に応じてハードウェアスレッドを指定する第1のスレッドスケジューラ19と、指定されたハードウェアスレッドにより生成された命令を実行する演算回路10と、を有し、第1のスレッドスケジューラ19は、優先順位が高いハードウェアスレッドを優先的に選択し、選択されたハードウェアスレッドにより生成される命令が演算回路において実行される度に、実行された命令を生成したハードウェアスレッドに対する優先順位の更新し、最も優先順位が高いハードウェアスレッドの優先順位が最低になるまでの間に少なくとも一つの他のハードウェアスレッドを選択するものである。

(もっと読む)

演算処理装置及び演算処理装置の制御方法

【課題】効率的なスレッド選択を可能にする演算処理装置を提供することを課題とする。

【解決手段】複数のスレッドの命令アドレス又は予測対象の分岐命令の分岐先アドレスを選択して複数のスレッドのアドレスを出力する第1のセレクタ(SL1〜SLn)と、第1のセレクタが出力した複数のスレッドのアドレスのうち1個を選択する第2のセレクタ(313)と、第1のサイクルステージで、第2のセレクタが選択したアドレスの分岐命令が分岐するかを示す分岐方向を選択されたアドレスに基づき予測して出力するとともに、第1のサイクルステージより後の第2のサイクルステージで、予測対象の分岐命令の分岐先アドレスを選択されたアドレスに基づき予測して出力する分岐予測回路(204)と、分岐予測回路が出力した分岐方向に基づき、第1セレクタ及び第2のセレクタによるスレッドのアドレスの選択を制御するスレッド調停回路(311)とを有する。

(もっと読む)

情報処理装置、情報処理方法

【課題】各プロセッサ間で効率的に演算結果を共有可能な情報処理装置を提供する。

【解決手段】プログラムを記憶するプログラム記憶手段11と、コア毎の演算結果を記憶する演算結果記憶手段45と、コア数分の命令の命令セットを実行順にプログラム記憶手段から読み出し一次記憶部に記憶する命令読み出し手段21と、命令セットに含まれる命令を各コアの命令キューに記憶する命令配信手段32と、一次記憶部に記憶された第一の命令セットに含まれる命令を第一のコアが演算した演算結果を演算対象とする命令が第一の命令セットよりも後に実行される第二の命令セットに含まれ第一のコアと異なる第二のコアが実行するか否かを判定する命令依存関係判定手段33と、命令依存関係判定手段が第二のコアが第二の命令セットに含まれる命令を実行すると判定した場合第一のコアの演算結果記憶手段の値を第二のコアの演算結果記憶手段に複写する複写手段34と、を有する。

(もっと読む)

半導体集積回路

【課題】性能低下を招くことなく回路面積を削減出来る半導体集積回路を提供すること。

【解決手段】第1メモリ30と、第1メモリ30に対するキャッシュメモリとして働く第2メモリ10とを備える。第1メモリ30からデータが読み出される場合の第1読み出し、第2メモリ10からデータが読み出される場合の第2読み出し、及び該データを第2メモリ10から読み出すと決定する判定、は、複数の処理ステージのうちのいずれかの処理ステージで実行される。第1読み出しにて読み出されたデータが出力されるタイミングと、第2読み出しにて読み出されたデータが出力されるタイミングとは同一である。第1読み出しで読み出されたデータは、第2メモリ10を経由しない経路を用いて出力される。

(もっと読む)

プロセッサ、及びプロセッサの制御方法

【課題】複数のパイプラインを有するプロセッサにおいて、処理効率を低下させることなくバンク競合を回避する。

【解決手段】メモリの複数のバンクに第1のバンクアクセス順序でアクセスする第1の処理部と、前記第1の処理部のアクセスの開始に続いて第2のバンクアクセス順序で前記複数のバンクにアクセスを開始する第2の処理部と、前記第1の処理部及び前記第2の処理部による前記複数のバンクへのアクセスが競合する場合に、前記第2のバンクアクセス順序を前記競合が生じない第3のバンクアクセス順序に並べ替えて前記第2の処理部を前記複数のバンクにアクセスさせる制御部とをプロセッサに備えることで、処理効率を低下させることなくバンク競合を回避できる。

(もっと読む)

処理パイプラインの制御

【課題】処理パイプライン内の処理バブルの低減が可能なデータ処理装置を提供する。

【解決手段】グラフィクス処理ユニットは、第1パイプライン部分18と第2パイプライン部分20とを有するテクスチャパイプライン6を含む。第1パイプライン部分18内の主題命令は、その主題命令によりメモリからロードされる記述子データが、共有記述子キャッシュ内に貯えられるまで、第1パイプライン部分18内で再循環される。記述子が、共有キャッシュ内に保存されている場合、主題命令は、追加の処理操作が実行される第2パイプライン部分20に渡され、それらの追加の処理操作が完了するまで再循環される。記述子データは、その記述子データを利用するのに必要とされるテクスチャパイプライン6内の係属中の主題命令がなくなるまで、共有記述キャッシュ内に固定される。

(もっと読む)

プロセッサ、システムおよびプロセッサの動作方法

【課題】実行サイクルが動的に変化する命令を実行するときに、不要な命令が実行されることを防止し、プロセッサの演算処理の性能を向上する。

【解決手段】プロセッサは、実行サイクル数が動的に変化する第1の命令を実行するために、最大の実行サイクル数に対応する数の複数の第1の命令である命令群が格納されている命令メモリから第1の命令をフェッチするフェッチ部と、命令群の次の命令が格納されている命令メモリのアドレスが保持されるアドレスレジスタと、フェッチ部によりフェッチされた命令を解読するデコード部と、デコード部により解読された命令を受けて演算を実行し、第1の命令の実行に必要な演算の完了を判断したときに終了信号を出力する演算部とを備え、フェッチ部は、終了信号に応答してアドレスレジスタ内のアドレスを用いて次の命令を命令メモリからフェッチする。

(もっと読む)

演算処理装置及び演算処理方法

【課題】レジスタからの読み出しデータにおける誤り検出時に、プログラム実行動作を停止することなく、継続して実行可能である演算処理装置を提供する。

【解決手段】演算処理装置は、レジスタから読み出したデータのエラーを検出し訂正する訂正制御部と、命令の実行要求に応じてキャッシュ領域又はノンキャッシュ領域にアクセスするとともに、実行要求された一の命令がノンキャッシュ領域にアクセスするロード命令であることを通知するキャッシュ制御部と、一の命令がノンキャッシュ領域にアクセスするロード命令であることがキャッシュ制御部により通知されると、一の命令をキャッシュ制御部に実行させる間、他の命令の実行を待たせることにより、ノンキャッシュ領域にアクセスするロード命令の実行中にエラーが検出されないようにする命令実行制御部とを含む。

(もっと読む)

非同期式回路

【課題】2相式の非同期式回路の処理速度を向上させると共に、回路規模の増大を抑制する。

【解決手段】非同期式回路200は、段階的に接続された複数の回路ブロックを備え、夫々の回路ブロックが、演算回路と、該演算回路に対して2相式制御を行う制御回路を有する。モード制御回路230は、1段目の回路ブロックに対して、該回路ブロックが休止相を開始したときに初期化を開始し、最下段の回路ブロックが休止相を開始したときに稼働相を開始し、2段目の回路ブロックに対して、1段目の回路ブロックが初期化を開始したときに稼働相を開始し、1段目の回路ブロックが稼働相を開始したときに初期化を開始するように制御を行う。

(もっと読む)

情報処理装置

【課題】命令実行の許可タイミングを、より適切に決定すること。

【解決手段】プログラムメモリと、該プログラムメモリに格納された命令を実行する命令実行手段と、前記プログラムメモリを含む記憶装置のアドレスに対応した読み込み補正時間を出力するアドレス/補正時間変換手段と、前記プログラムメモリから命令のフェッチを開始した時刻と、該命令のアドレスに基づき前記アドレス/補正時間変換手段により出力される読み込み補正時間とに基づき前記命令実行手段による命令実行を許可又は禁止する命令実行許可手段と、を備える情報処理装置。

(もっと読む)

ベクトルマスク設定技術

【課題】本発明の課題は、マイクロプロセッサアーキテクチャの命令セットアーキテクチャにおいて使用される効果的なベクトルマスク生成技術を提供することである。

【解決手段】本発明によると、上記課題は、ベクトルマスクを格納するための第1処理を検出する第1ロジックと、前記第1処理より以前のベクトルマスク値を生成するための最新の第2処理を特定する第2ロジックと、前記第2処理が特定される場合、前記第1処理の実行を回避する第3ロジックとから構成されることを特徴とするプロセッサにより解決される。

(もっと読む)

ベクトル処理回路、命令発行制御方法、及びプロセッサシステム

【課題】本実施例に係るベクトル処理回路は、データ語長が異なる命令に対してレジスタ干渉の有無の判定を正確に行い、後続命令の発行タイミングを適切に調整し、命令実行の効率化を図ることを目的とする。

【解決手段】本実施例に係るベクトル処理回路で、各パイプライン演算器が、1つの命令に対して、ソースとして指定された複数の配列要素のデータを複数のサイクルに分けて演算し、演算結果をディスティネーションとして指定された複数の配列要素に複数のサイクルに分けて格納し、命令発行制御回路が、命令のデータ語長に応じて配列要素のデータサイズを変化させ、先行命令のデータ語長が後続命令のデータ語長より長いとき、先行命令の非先頭のサイクルで処理される少なくとも1つの配列要素と後続命令の先頭サイクルで処理される配列要素との間でレジスタ干渉の有無を判定し、レジスタ干渉の判定結果に基づいて後続命令の発行タイミングを調整する。

(もっと読む)

情報処理装置及び情報処理方法

【課題】データの信頼性を確保したまま演算レジスタへの高速読み出しを実現する。

【解決手段】この情報処理装置は、ロードリクエスト生成部と、個々のロードリクエストに対するロードデータを格納し、演算レジスタに転送するロードバッファと、ロードリクエスト生成部によって生成されたロードリクエストを入力し、ロードリクエストに対するロードデータをメインメモリから読み出すと共に、メインメモリによって生成された、ロードデータをロードバッファから読み出す順番を示す付随情報を、ロードデータに先立って送出するようメインメモリを制御するメモリネットワークと、付随情報に基づいて、付随情報に対応するロードデータの到着の遅れを検出し、ロードデータの到着の遅れに基づいて、ロードバッファから演算レジスタへの読み出しの開始時間を調整する整列判定部と、を備える。

(もっと読む)

プロセッサ内のマルチスレッド間通信

【課題】プロセッサコアで実行するマルチスレッドにおいて、非常に低いオーバーヘッドでスレッド間の同期を可能にする。

【解決手段】SMT動作実施形態において、第2のスレッドの実行中に、第1のスレッドに関連するレジスタにアクセスする方法を含む。この方法は、ソースオペランドに関連する同期インジケータが第2のスレッドのプロデューサ演算が終っていないことを示す場合、第2のスレッドのレジスタファイルからソースオペランドにアクセスする第1のスレッドの命令を実行しないようにし、同期インジケータが第2のスレッドのプロデューサ演算が終了したことを示す場合、命令を実行する段階を備える。他の実施形態において、マルチコアであってもよい。

(もっと読む)

情報処理装置、キャッシュ装置およびデータ処理方法

【課題】パイプラインを用いて処理を行う情報処理装置において、繰り返し必要とされるデータが情報処理装置から破棄されないように、置き換え制御を工夫しておこなうことで、より効率的な技術を提供する。

【解決手段】情報処理装置は、第1パイプラインと第2パイプラインと処理手段とリオーダ手段とを有する。第1パイプラインは、複数の第1ノードを有し、当該第1ノードに対して第1方向にある第1ノードへ当該第1ノードの保持する第1データを移動させ、第2パイプラインは、第1パイプラインの第1ノードの各々に対応する複数の第2ノードを有し、当該第2ノードに対して第1方向と逆の第2方向にある第2ノードへ当該第2ノードの保持する第2データを移動させ、処理手段が、第1データと第2データとを用いてデータ処理を行い、

リオーダ手段が、第2パイプラインの出力した第2データの属性情報に基づき、出力した第2データの何れかを保持し、保持した第2データを第2パイプラインに入力する。

(もっと読む)

プロセッサシステム、命令列最適化装置、および命令列最適化プログラム

【課題】複数のプロセッサを備えたプロセッサシステムの消費電力を処理能力を低下させることなく低減する。

【解決手段】命令解析部402は記憶部100に記憶されている所定量の一連の命令コードを先読みして解析し、各命令がCPU103とHWE104で並列に実行可能な場合に、標準実行時間推定部403、換算実行時間算出部404が標準実行時間の推定、換算実行時間の算出をし、割り当て・クロック周波数決定部405はCPU103およびHWE104を最高クロック周波数で動作させた場合に待ち時間が生じる方に最高クロック周波数よりも低い周波数のクロック信号を供給することにより消費電力が最小になるようにプロセッサの割り当て、クロック周波数を決定し、クロック制御部106は出力するクロック信号の周波数を切り替え、命令割り当て制御部102は命令コードをCPU103等に転送して実行させる。

(もっと読む)

信号処理装置

【課題】所望の処理性能を満足した上で、低消費電力化を図ることができるようにする。

【解決手段】各ロジック部11における許容処理時間と各ロジック部11の処理時間を比較し、その比較結果を参照して、複数のロジック部11間の接続箇所毎に、挿入されているフリップフロップ12を省いて、その接続箇所における前段のロジック部11と後段のロジック部11を直結するか否かを判定するパス長判定部を設け、セレクタ13がパス長判定部により直結する旨の判定がなされた接続箇所では、挿入されているフリップフロップ12を省いて、その接続箇所における前段のロジック部11と後段のロジック部11を直結する。

(もっと読む)

アイドル状態検出回路、半導体集積回路、信号処理装置、アイドル状態検出方法

【課題】キャッシュミスに起因するプロセッサのアイドル状態を正確に検出する。

【解決手段】プロセッサ(11)は、パイプライン処理により命令を実行する命令実行ユニット(110)と、命令実行ユニットによって利用される命令およびデータを格納する一次キャッシュ(111)とを備える。アイドル状態検出回路(10)において、実行命令検出部(101)は、命令実行ユニット(110)によって現在実行されている命令および次に実行される予定の命令が存在しない命令なし状態を検出する。リード待ち検出部(103)は、命令実行ユニット(110)がリードデータを待っているリード待ち状態を検出する。判定部(104)は、命令なし状態およびリード待ち状態のうち少なくとも1つが検出された場合に、プロセッサ(11)がアイドル状態であると判定する。

(もっと読む)

1 - 20 / 104

[ Back to top ]