Fターム[5B013DD02]の内容

Fターム[5B013DD02]の下位に属するFターム

付加処理機構 (116)

Fターム[5B013DD02]に分類される特許

1 - 20 / 96

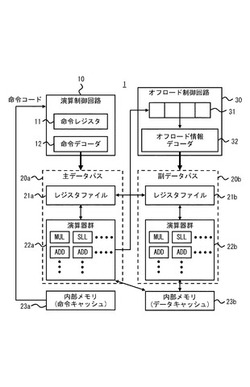

情報処理装置

【課題】従来の情報処理装置は、同時発行命令数により並列演算数に制限があった。

【解決手段】本発明の情報処理装置は、命令キャッシュと、データキャッシュと、並列動作可能な複数の演算器を備える第1、第2の演算器群22a、22bと、第1の演算器群22aに対する1以上の演算命令を生成する第1の演算制御回路10と、固定命令レジスタ31の命令コードに基づき第2の演算器群22bに対する1以上の演算命令を生成する第2の演算制御回路30と、を有し、第1の演算器群22aは、第1の演算制御回路10が第1の特定命令コードに基づき生成した演算命令に応じて固定命令レジスタ31に命令コードを設定し、第1の演算制御回路10が第2の特定命令コードに基づき生成した演算命令に応じて第2の演算器群22bに処理データを与え、第2の演算器群22bは、第2の演算制御回路30が生成した演算命令に基づく演算を繰り返し実行する。

(もっと読む)

演算処理装置および演算処理装置のスロット制御方法

【課題】演算スロットの使用効率の向上を図る。

【解決手段】複数の異なる演算スロット10〜13を有し、マルチサイクル動作を行う演算処理装置であって、演算する命令をプリデコードしてその種類を識別するプリデコード部5と、前記命令の種類に対応した重み設定値を格納する重み設定レジスタ7と、前記識別された命令の種類および前記重み設定値を受け取り、前記演算する命令に対して重みづけ値を計算する重みづけ計算部6と、前記重みづけ計算部の計算結果に基づいて、前記複数の異なる演算スロットのいずれかを選択するスロット選択部4と、を有する。

(もっと読む)

演算処理装置および演算処理方法

【課題】レジスタからのリードパスの数が増大することを抑制しつつ、演算性能を高める。

【解決手段】演算器11は、2つのオペランドのそれぞれとしてレジスタからの読み出しデータと即値のいずれかの入力を受けることが可能である。演算器12は、2つのオペランドのうち、一方のオペランドとしてレジスタからの読み出しデータと即値のいずれかの入力を受けることが可能であり、他方のオペランドとして即値のみが入力される。制御部13は、入力された演算実行命令に基づき、この演算実行命令に係る演算における2つのオペランドのそれぞれがレジスタからの読み出しデータと即値のいずれであるかを判定し、判定結果に応じて、入力された演算実行命令に係る演算を演算器11,12のいずれかに実行させる。

(もっと読む)

情報処理装置、エミュレーション処理プログラム及びエミュレーション処理方法

【課題】エミュレートする処理が分岐命令であることによる処理速度の低下を抑制できる。

【解決手段】情報処理装置1では、第1のプロセッサ11が、受信した命令アドレスの次の命令アドレスを算出する算出部11aと、算出した命令アドレスと当該命令アドレスに基づいて読み出した命令情報とを第2のプロセッサ12に送信する第1の送信部11bとを含み、第2のプロセッサ12が、実行した処理の実行結果に含まれる第1の命令アドレスを第1のプロセッサ11に送信する第2の送信部12aと、第1のプロセッサ11から受信した第2の命令アドレスが、第1の命令アドレスと同じである場合に、第1のプロセッサ11から受信した命令情報に基づく処理を実行し、第2の命令アドレスが第1の命令アドレスと同じでない場合に、第1の命令アドレスに基づいて命令情報を読出し、読み出した命令情報に基づく処理を実行する実行部12bとを含む。

(もっと読む)

プロセッサ

【課題】逐次実行部(RISCプロセッサ100)の処理と並列実行部(VLIWコプロセッサ200)の処理とを効率良く融合させる。

【解決手段】RISCプロセッサ100において同時にフェッチされた4つの命令のうち第2番目と第4番目の命令の特定フィールドが命令プリデコーダ170によってプリデコードされる。この特定フィールドはオペコードフィールドと同時発行命令数フィールドを含む。オペコードフィールドがVLIWコプロセッサ命令を示す場合、プログラムカウンタ管理部110は同時発行命令数フィールドに応じてプログラムカウンタの増分値を制御する。VLIWコプロセッサ200では同時発行命令数フィールドに応じた並列度によりVLIWコプロセッサ命令が実行される。

(もっと読む)

マルチスレッドプロセッサ

【課題】従来のマルチスレッドプロセッサは、処理能力を十分に引き出すことができない問題があった。

【解決手段】本発明のマルチスレッドプロセッサは、第1の命令コードを格納する第1の命令バッファ231と、第2の命令コードを格納する第2の命令バッファ232〜23mと、を備える命令供給部10と、第1、第2の命令バッファから発行される命令コード選択する命令セレクタ11と、命令セレクタ11が選択した命令コードをデコードする命令デコーダ12と、デコード結果に基づく情報処理を行う命令実行部13と、を有する。命令供給部10は、優先的に第1の命令バッファに第1の命令コードを格納し、第1の命令バッファに格納される第1の命令コードの数が命令供給部10が並列して発行可能な命令コード数の最大値の2倍以上となった場合に第2の命令バッファに第2の命令コードを格納するスレッド制御部24を有する。

(もっと読む)

半導体装置

【課題】プログラム可能な半導体装置において、クロック周波数を保証しつつ、複数の演算命令の組み合わせで形成される演算処理を効率的に実行できる。

【解決手段】本開示の一実施形態は、一定のクロック信号に同期して演算を行う半導体装置であって、演算制御情報を出力する制御部13と、データを記憶する記憶部11と、第1のデータに対して第1の演算制御情報に従い演算を行う演算ユニット100と、第2のデータに対して第2の演算制御情報に従い演算を行う演算ユニット101とを備える。演算ユニット100は、演算回路を複数個備える。演算ユニット101は、論理ゲート段数n(n>m)の演算回路を少なくとも1個備える。

(もっと読む)

画像処理装置、画像形成システム及び画像処理プログラム

【課題】 複数のDRPがパイプライン処理方式によって実行する場合に、上位制御装置からDRPの識別がつくように各DRPに識別番号が割り付けられ得る画像処理装置を提供する。

【解決手段】 入力された印刷ジョブに基づく画像処理を複数のDRP61〜68にパイプライン処理方式によって実行させる場合に、複数のDRP61〜68の個数に基づいて、識別番号をこれらのDRPに割り付ける識別番号割付部32aと、複数のDRP61〜68の中の最終段のDRP68が、画像処理の処理結果を外部に出力する印刷データ出力部13と接続されているか否かに基づいて、識別番号割付部32aによる割付処理を変更する割付処理第1変更部32bと、印刷データ出力部13と接続されていない場合に、複数のDRP61〜68が1枚の基板にのみ設置されているか否かに基づいて、識別番号割付部32aによる割付処理をさらに変更する割付処理第2変更部32cとを有する。

(もっと読む)

マルチスレッド処理装置

【課題】スーパースカラ動作によって効率処理を行うと共に、処理のリアルタイム性を確保することが可能なマルチスレッド処理装置を提供すること。

【解決手段】複数の処理手段を有し、該複数の処理手段のいずれかを利用してハードウエア・マルチスレッディングを行うマルチスレッド処理装置であって、前記ハードウエア・マルチスレッディングに係る複数のスレッドのそれぞれについて、前記複数の処理手段のうち二以上の処理手段を用いたスーパースカラ動作の許可又は不許可が規定されていることを特徴とする、マルチスレッド処理装置。

(もっと読む)

エネルギー効率のよいマルチコアプロセッサのための共用メモリ

本明細書では、プロセッサリソースを共用するように適合されたマルチコアプロセッサに関連した技術が説明される。一例示的マルチコアプロセッサは複数のプロセッサコアを含むことができる。マルチコアプロセッサはさらに、複数のプロセッサコアのうちの2つ以上に選択的に結合される共用レジスタファイルを含むことができ、共用レジスタファイルは、選択されるプロセッサコア間で共用リソースとして働くように適合される。 (もっと読む)

データ処理装置、およびパラメータ設定方法

【課題】データ信号に対して順次に信号処理を行う信号処理回路が信号処理に用いるパラメータの設定に係るソフトウェアおよびハードウェアの設計、実装を容易とすることが可能なデータ処理装置、およびパラメータ設定方法を提供する。

【解決手段】識別情報を記憶しパラメータを記憶可能なレジスタを備え、モード制御信号に基づいてパラメータの記憶処理または信号処理を順次行う複数の信号処理部と、記憶部と、記憶部からパラメータ情報または処理データを選択的に読み出すデータ読み出し部と、信号処理部から出力されるデータ信号に対応するデータを記憶部に選択的に記録するデータ書き込み部と、モード制御信号を信号処理部へ出力する制御部とを備え、信号処理部は、パラメータの記憶処理を行う場合データ信号が識別情報と対応するときに、データ信号に含まれるパラメータをレジスタに記録するデータ処理装置が提供される。

(もっと読む)

画像分割システム及び方法

【課題】デジタル信号処理技術を改良するため、カメラから取り込んだ画像のデジタル信号処理を促進、改善する。着目した対象物と背景を区別するなどの画像分割を行うのに適している。

【解決手段】画像分割装置は、FPGAなどのデバイスで好適に集積化して実現され、画素データを記憶するバッファメモリ12と、バッファメモリと通信し係数がプログラム可能でデジタルフィルタ14と、バッファメモリと通信して画素データのヒストグラムを生成するヒストグラム生成モジュール16と、バッファメモリと通信して画素データに関する統計を作成する統計生成モジュール18と、複数の閾値のなかから1つを選択する閾値選択モジュール20と選択された閾値をバッファメモリに記憶されたデータに適用して選択された閾値より大きな超過データを生成する適用閾値モジュール22を備える。

(もっと読む)

デジタル信号プロセッサ

【課題】性能および有用性を増進させるデジタル信号プロセッサを提供する。

【解決手段】可変長命令セットを利用するための通話を処理するデジタル信号回路において、DSPは3つのデータバスの組を含み、その上でデータはレジスタバンク120と3つのデータメモリ102,103,104と交換されることができる。レジスタバンク120は、少なくとも二つのプロセスユニット128,130によりアクセス可能なレジスタを有して使用され得る。命令フェッチユニット156は、命令メモリ152中に格納される可変長の命令を受信することを含むことができる。この命令メモリ152は3つのデータメモリ102,103,104の組から離されている。

(もっと読む)

プロセッサ及びプロセッサにおける命令発行の制御方法

【課題】並列発行可否判定の必要な命令と不要な命令をプロセッサにおいて効率よく連続的に処理可能とする。

【解決手段】プロセッサ1は、実行ユニット121〜124と、命令ユニット10を含む。命令ユニット10は、命令間の依存関係に基づいた並列発行可否判定を行うべき対象命令であるか否かを、命令ストリームに含まれる命令単位で識別する。そして、命令ユニット10は、命令ストリームに含まれる第1の命令が対象命令である場合に、第1の命令とこれに引き続く少なくとも1つの命令との間での依存関係の検出結果に基づいて、命令ユニット121〜124に並列発行する命令数を調整する。さらに、命令ユニット10は、第1の命令が対象命令でない場合に、第1の命令を含む予め定められた固定数の命令からなる命令グループを、命令グループ内での依存関係の検出結果に拘わらず無条件に実行ユニット121〜124に並列発行する。

(もっと読む)

情報処理装置および情報処理プログラム

【課題】動的再構成可能な演算手段によって複数の情報処理を行うにあたり、再構成時間の短い粗粒度の再構成可能回路は、帰還回路のレイテンシが大きいため性能低下が発生する。このため、時間を考慮した回路構成を行うこと。

【解決手段】本発明は、動的に回路が再構成される第1演算部を複数備える第1回路構成部10と、固定の回路から成る第2演算部を複数備える第2回路構成部20と、情報を処理するにあたり、第1回路構成部10ではレイテンシによる性能低下が発生する回路において、第2回路構成部20で補間する回路構成を制御する回路構成制御部30とを有する情報処理装置である。

(もっと読む)

大命令幅プロセッサにおける処理効率の向上

1つ以上の処理ユニット(40)と、実行パイプライン(32)と、制御回路(28)とからなるプロセッサ(20)。実行パイプラインは、少なくとも段階を成す第1と第2のパイプラインステージを有し、パイプラインの連続するサイクルの中で処理ユニットにより遂行される動作を特定するプログラム命令が、第1のパイプラインステージによりメモリから取得され、そして前記第2のパイプラインステージに運ばれ、第2のパイプラインステージは処理ユニットに対し特定の動作を遂行するようにさせる。制御回路は、パイプラインの第1のサイクルにおいて第2のパイプラインステージ内に存在するプログラム命令が、パイプラインの次のサイクルにおいて再び実行されると判定した時に、前記実行パイプラインに対し、前記メモリから前記プログラム命令を再取得することなく、前記パイプラインステージの1つの中の前記プログラム命令を再使用させるように接続される。 (もっと読む)

マルチスレッド式データ処理システム

異なるハードウエアリソースを備えた複数のハードウエアスレッド(32,34)を有するマルチスレッド式プロセッサの命令を実行する方法及び装置を提供し、これは、複数の命令のストリームを受信する段階(38、44)、及びどのハードウエアスレッドが実行のための命令を受信することができるかを判断する段階(40、46)、命令を実行するために利用可能であると判断されたスレッドが、その命令によって要求される利用可能なハードウエアリソースを有するか否かを判断する段階(36)、及び判断の結果に基づいて命令を実行する段階(50)を含む。 (もっと読む)

半導体装置、および、半導体装置によるデータ処理方法

【課題】パイプライン型に接続した複数のリコンフィギュラブル回路が、データを演算していない時間がより少なくなるように実行回路を構築できること。

【解決手段】コントローラ10と、後段に複数段直列に接続された演算ユニット12とを備えた半導体装置であって、コントローラ10は、データと再構成情報とを初段の演算ユニット12に入力し、演算ユニット12は、再構成情報により特定される回路情報による実行回路で構築され入力されたデータを演算する演算器120と、再構成情報を次の演算に必要な回路情報を特定するように更新する回路情報識別子更新部123と、演算器120による演算を繰り返すかを判断し、回数分の演算を完了したと判断した場合、データと再構成情報とを次段の演算ユニット12に入力し、完了していないと判断した場合、データと再構成情報とを再度自身に入力するように制御する繰り返し制御部126と、を備えた。

(もっと読む)

スレッドに最適化されたマルチプロセッサアーキテクチャ

一態様において本発明はシステムであり、(a)単一のチップ上の複数の並列プロセッサと、(b)チップ上に配置されていて、かつプロセッサの各々によってアクセス可能なコンピュータメモリとを備えていて、プロセッサの各々は、de minimis命令セットを処理するように動作可能であり、プロセッサの各々は、プロセッサの中の少なくとも3つの特定のレジスタの各々専用のローカルキャッシュを有している。別の態様において本発明はシステムであり、(a)単一のチップ上の複数の並列プロセッサと、(b)チップ上に配置されていて、かつプロセッサの各々によってアクセス可能なコンピュータメモリとを備えていて、プロセッサの各々は、スレッドレベルの並列処理のために最適化された命令セットを処理するように動作可能であり、各プロセッサは、チップ上のコンピュータメモリの内部データバスにアクセスし、内部データバスはメモリの1行の幅である。  (もっと読む)

(もっと読む)

リアルタイムデータ処理のための方法&装置

【解決手段】プログラマブルマイクロプロセッサのための改善された命令セット&コア設計、制御、及び通信が開示され、これは、今日の及び先行技術のプロセッサにおける集中型のプログラムシーケンシングを、新規の分散型のプログラムシーケンシングで置き換えるための戦略を伴う。新規の分散型のプログラムシーケンシングでは、各機能ユニットは、自身の命令フェッチ&デコードブロックを有し、各機能ユニットは、プログラム格納のための自身のローカルメモリを有し、計算ハードウェア実行ユニット及びメモリユニットは、設定及び切り替え相互接続が異なるハードウェアユニットを確立する様々なアプリケーション命令シーケンスに応じて異なる順序に再設定可能なパイプラインステージを伴うプログラマブル埋め込みプロセッサとして、柔軟にパイプライン化される。 (もっと読む)

1 - 20 / 96

[ Back to top ]