Fターム[5B015KB43]の内容

Fターム[5B015KB43]に分類される特許

1 - 12 / 12

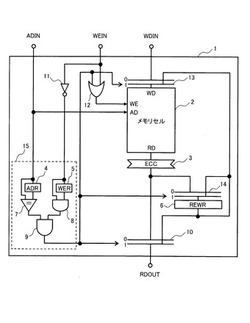

半導体記憶装置およびその制御方法

【課題】プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置を提供することである。

【解決手段】本発明にかかる半導体記憶装置は、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセル2と、メモリセル2に対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段15と、メモリセル2から読み出されたデータのエラーを訂正するエラー訂正手段3と、エラー訂正後のデータを保持するデータ保持手段6と、を備える。メモリセル2は、検出手段15の検出結果に応じて、データ保持手段6に保持されているデータを前記アドレスに対応づけて書き込む。データ保持手段6は、前記アドレスに応じた読み出しデータとしてデータ保持手段6に保持されているデータを出力する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置におけるマルチビットエラーの発生を抑制する。

【解決手段】複数のカラムを有し、互いに異なる1つのデータの入出力端子に各々が対応づけられるブロック(1I/Oビットに対応するセルアレイ)26A、26Bを複数有し、それらをカラム方向に隣り合わせて配置した第1のメモリセルアレイ、及びそれと同じく構成された第2のメモリセルアレイを備え、第1のメモリセルアレイのブロック26A−0、26A−2と第2のメモリセルアレイのブロックブロック26B−1、26B−3とを組とし、第1のメモリセルアレイのブロック26A−1、26A−3と第2のメモリセルアレイのブロック26B−0、26B−2とを組としてアドレスを割り当て、あるアドレスに対するアクセスにおいて、各メモリセルアレイにてそれぞれ1つおきのブロックの出力がデータとして出力されるようにする。

(もっと読む)

分散ブロックRAM

【課題】リコンフィギュラブル装置における組み込みメモリブロック等のメモリブロックを提供する。

【解決手段】組み込みメモリブロック等のメモリブロック30、40は、共通グローバルバスとインタフェース回路とを用いて互いに接続される。インタフェース回路により、メモリブロックは選択的に接続されて深さと幅とが拡張されたメモリブロックを形成することができ、独立ブロックとして使用することが可能になる。インタフェース回路は、メモリブロック内のメモリアレイを、同一の共通グローバルバス上で連結された所望のメモリ入出力ラインに接続し、それによって拡張メモリブロックにアクセスする便利な入出力ラインが使用可能になる。共通グローバルアドレスバスにより、メモリブロックがアドレス情報を互いに送信することができ、使用されないアドレス入力を、ブロック選択情報又は共通の列情報等の情報を送信するために再び用いることができる。

(もっと読む)

半導体記憶装置の入力回路およびその制御方法

【課題】電力消耗量を減らすことができる半導体記憶装置の入力回路およびその制御方法を提供する。

【解決手段】本発明に係る半導体記憶装置の入力回路は、複数の外部信号を選択的にラッチして出力するように構成された複数のラッチ、および半導体記憶装置の動作モードに応じて前記複数のラッチの動作を制御するように構成されたラッチ制御部を備える。また、制御信号に応じて複数の外部信号を選択的にラッチし、ラッチされた信号を出力するように構成された複数のラッチ;および前記ラッチされた信号を用いて半導体記憶装置の動作モードを判断し、前記判断した動作モードによって前記制御信号を生成するように構成されたラッチ制御部を備えることを他の特徴とする。

(もっと読む)

半導体記憶装置、およびアドレスラッチの高速化方法

【課題】DDRの高速化方式において、従来別々とされていたアドレスピン及びコマンドピンを共通化し、Rise/Fall両エッジでコマンド及びアドレスデータを取り込む際に、従来のDDR方式において、1/2tCK分のアクセスペナルティの問題が生じることを解決する。

【解決手段】アドレス信号(ADD)を、FallエッジF1に同期してスルーラッチタイプのラッチ回路により取り込み保持するように構成する。これにより、アドレスラッチにおいて、FallエッジF1から決まるアクセス時間をセットアップ分(tS)だけ高速化することができ、1/2tCK分のペナルティを緩和することが可能になる。

(もっと読む)

半導体装置

【課題】使い勝手が良くて高速動作及び高速応答性を実現した半導体装置を提供する。

【解決手段】メモリアレイを複数のワード線と複数の相補ビット線の交点に設けられた複数のスタティック型メモリセルで構成する。データ入出力回路は、上記スタティック型メモリセルに対するデータ入力及びデータ出力を行う。アドレス選択回路は、上記メモリアレイにおける上記スタティック型メモリセルの選択及び上記メモリアレイと上記データ入出力回路との間の信号伝達経路の選択を行う。アドレス入力回路は、上記アドレス入力回路は、第1タイミングでロウ系アドレス信号を取り込み、第2タイミングでカラム系アドレス信号を取り込む入力回路と、上記アドレス選択回路に供給される上記ロウ系アドレスを保持するロウ系レジスタと、上記アドレス選択回路に供給される上記カラム系アドレス信号を保持するカラム系レジスタとを有する。

(もっと読む)

半導体メモリ集積回路

【課題】1チップで、高速動作と低消費電力動作の両方に対応でき、その切り替えを容易に行える、半導体メモリ集積回路を提供する。

【解決手段】ラッチ回路11にXアドレスを保持させるラッチ回路制御信号Gを生成する回路として、高速用制御回路12と低電流用制御回路13とを設ける。高速用制御回路12は、バンクアクティブ信号Aに無関係に、XアドレスBをそのままスルーしてラッチ回路11に保持させる。低電流用制御回路13は、バンクアクティブ信号Aが入力された後に、XアドレスBをラッチ回路11に保持させる。 入力側切替回路14および出力側切替回路15は、切替信号Fに応じて、高速用制御回路12を使用するか、または低電流用制御回路13を使用するかを切り替える

(もっと読む)

同期型バースト半導体メモリ装置

【課題】同期型バースト半導体メモリの性能を向上させる。

【解決手段】外部クロック信号に同期され、動作する半導体メモリ装置300において、データビットを貯蔵する複数のメモリセルを持つメモリセルアレイ326と、外部アドレスに応じて読出/書込動作のための一連の第1内部アドレスを発生する第1内部アドレス発生器310と、外部アドレスに応じて読出/書込動作のための一連の第2内部アドレスを発生する第2内部アドレス発生器312と、これらの出力中、一つを選択するアドレス選択器316と、外部から印加される読出及び書込命令情報に応じて第1及び第2内部アドレス発生器310,312とアドレス選択器316の動作を制御する制御器304と、外部から印加される読出及び書込命令情報に応じてアドレス選択器316の出力をデコーディングし、メモリセル326を選択するアドレスデコーダー318とを含む。

(もっと読む)

半導体集積回路への入力信号の制御方法

【課題】クロック同期型の半導体メモリにおける不要な入力信号の受信による消費電流を抑制することができる、消費電流の少ない半導体集積回路を提供する。

【解決手段】メモリアレイ1にデータを記憶する同期型SRAMS1は、クロック信号CKの立ち上がりに同期して動作する。この同期型SRAMS1には、ラッチ機能を有し、入力信号の取り込みを制御する入力回路5〜9、内部クロック回路11、入力受信信号生成回路12等が設けられている。ここで、入力信号はクロックの変化後に取り込まれ、入力信号が確定するまでの不要な消費電流が抑制される。また入力信号を受信する期間は、入力回路5〜9が入力信号の受信を開始してラッチするまでの僅かな期間とされる。

(もっと読む)

半導体装置

【課題】本発明は、チップ面積の増加が少なく、かつ高速な入力初段ラッチを備えた半導体装置を提供することを目的とする。

【解決手段】半導体装置は、入力信号を受け取り第1のクロック信号の半サイクル期間だけ該入力信号を保持する第1のラッチと、該第1のラッチの出力に接続される遅延要素と、該遅延要素の出力に接続され第2のクロック信号の半サイクル期間だけ該遅延要素から供給される信号を保持する第2のラッチと、該第1のクロック信号の該半サイクル期間で該第1のラッチがラッチした信号が後続する該第2のクロック信号の該半サイクル期間で該遅延要素を介して該第2のラッチにラッチされるように該第1のクロック信号及び該第2のクロック信号の少なくとも一方のタイミングを調整する回路とを含み、前記第1のラッチ及び第2のラッチは、転送ゲートと2個のインバータを有する第3のラッチとで構成されることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】 アクセス遅延が生じず、かつ誤動作を防ぐことが可能な半導体記憶装置を提供する。

【解決手段】 制御回路40はアドレス比較回路22から出力される外部アドレス信号とラッチアドレス信号との比較結果(信号DIFA0〜DIFAn)を受け、外部アドレス信号とラッチアドレス信号とが異なることの検知を行なうと、外部アドレス信号を再度ラッチするようアドレスラッチ回路20に指示する。ノイズを含む外部アドレスをラッチし、そのラッチアドレスに基づいて読出し動作を開始しても、外部アドレスが正常に戻った際に再び読出動作をやり直すことが可能になるので、誤動作を防ぐことが可能になるとともに、アクセス遅延を防ぐことができる。

(もっと読む)

半導体装置

【課題】 少ない外部端子数で組込みRAMのテストが可能でかつ不良箇所の特定を簡単に行うことができ、またパッケージ情報に基づき外部端子とメモリ部の入出力端子の接続を切り替えることができる半導体装置を提供する。

【解決手段】 RAMの入出力を半導体装置の外部端子と接続する際、外部端子とSRAM101のアドレス端子115、およびデータ入力端子116の間に第1、第2のラッチ回路110、111を構成するフリップフロップを設け、SRAM101に同時刻でテストベクタを入力できるようにデータを前記第1、第2のラッチ回路110、111でラッチすることにより、アドレス端子115およびデータ入力端子116をアドレス/データ外部端子107に共通化できるため、外部端子数が少ない場合でもRAMの検査を可能とする。

(もっと読む)

1 - 12 / 12

[ Back to top ]