Fターム[5B015QQ18]の内容

Fターム[5B015QQ18]に分類される特許

1 - 20 / 44

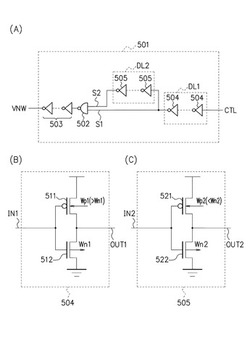

メモリ装置

【課題】高速にデータを書き込むことができるメモリ装置を提供することを課題とする。

【解決手段】メモリ装置は、第1及び第2のpチャネルトランジスタと、第1のpチャネルトランジスタ及び第2のpチャネルトランジスタのバックゲートに第2のバックゲート信号を出力するバックゲート信号生成回路(501)とを有し、バックゲート信号生成回路は、第1の遅延回路(DL1)と第2の遅延回路(DL2)とを有し、第1の遅延回路は、第3のpチャネルトランジスタ及び第3のnチャネルトランジスタを含む第1のインバータ(504)を有し、第3のpチャネルトランジスタは、第3のnチャネルトランジスタよりゲート幅が広く、第2の遅延回路は、第4のpチャネルトランジスタ及び第4のnチャネルトランジスタを含む第2のインバータ(505)を有し、第4のpチャネルトランジスタは、第4のnチャネルトランジスタよりゲート幅が狭い。

(もっと読む)

半導体記憶装置

【課題】ほとんどの場合において読み出し動作のアクセス時間をより速くする。

【解決手段】少なくとも第1および第2のポートのワード線と少なくとも第1および第2のポートのビット線とに接続され、クロック信号に同期して読み出し動作が行われるメモリセル(セルアレイ10内に配置)と、第1および第2のポートのロウアドレス同士を比較し、ロウアドレスの一致を検出するアドレス一致検出回路17と、アドレス一致検出回路17の検出結果に応じて調整されたタイミングを有するクロック信号を生成するタイミング生成回路16aと、を備える。

(もっと読む)

半導体記憶装置

【課題】メモリセルの特性バラツキに反映されたタイミング調整を可能とする。

【解決手段】メモリセル群は、対応の行のメモリセルに接続された複数のワード線と、対応の列のメモリセルに接続された複数の一対のビット線とをそれぞれが有する。一方のメモリセル群内のメモリセルへの書込もしくは読出が行われる場合には、他方のメモリセル群は非選択状態にある第1と第2のメモリセルアレイと、上記メモリセルとは接続関係が異なり、上記第1のメモリセルアレイの列に隣接して列状に設けられ、上記第1および第2のメモリセルへのデータの書込のいずれにおいても活性化される複数の第1ダミーセルと、上記メモリセルとは接続関係が異なり、上記第2のメモリセルアレイの列に隣接して列状に設けられ、上記第1および第2のメモリセルからの読出のいずれにおいても活性化される複数の第2ダミーセルとを有する。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】スタンバイ状態への設定と解除が頻繁に繰り返されることにより、消費電力が増大することを避けることのできる半導体装置を提供する。

【解決手段】内部回路50と、第1制御信号を受けて内部回路への電源供給を制御する電源制御回路40と、第2制御信号を受けて第1制御信号を出力する制御信号発生回路30と、を備え、制御信号発生回路30は、第2制御信号の非活性期間が第1の期間未満であるときに第1制御信号を非活性状態とせず、第1の期間以上であるときに第1制御信号を非活性状態とする。

(もっと読む)

半導体メモリの読取電流に追従するためのプログラム可能な追従回路

ワード線駆動回路

【課題】1本のワード線ごとにブースト用容量を設けることなく、ワード線を駆動する駆動電圧を昇圧させる。

【解決手段】インバータI0〜Im、IdのPチャンネル電界効果トランジスタM21のソース側に接続されたブースト用容量C1と、Pチャンネル電界効果トランジスタ21のソース側と電源電位VDDとを分離するPチャンネル電界効果トランジスタM1とを設ける。

(もっと読む)

メモリデバイスを動作させるシステムおよび方法

メモリデバイスを動作させるシステムおよび方法が、開示される。特定の実施形態では、第1のビット線および第2のビット線に結合されるビットセルを含む装置が、開示される。本装置はまた、第1のビット線および第2のビット線に結合されるセンス増幅器も含む。本装置は、第1の信号を受け取ることに応答してセンス増幅器イネーブル信号をセンス増幅器に提供するように構成されるループ回路を含む。本装置はまた、第2の信号を受け取ることに応答してワード線イネーブル信号をワード線ドライバーに提供するように構成されるワード線イネーブル回路も含む。ループ回路は、ワード線イネーブル回路が第2の信号を受け取る前に第1の信号を受け取る。  (もっと読む)

(もっと読む)

タイミング調整回路および半導体記憶装置

【課題】遅延量の分解能を必要に応じて精度よく設定する。

【解決手段】第1〜第m(mは2以上の整数)の遅延パスと、第1〜第mの遅延パスのいずれか一の遅延パスを選択する選択回路と、を含み、第i(i=1〜mの整数)の遅延パスは、nを1以上の整数とし、(n−iをmで割った商)+1個の、遅延時間がTである遅延素子(ただし、n<iの場合には遅延素子は存在しないものとする)と、遅延時間がT/m*iである第iのパス遅延回路と、を含む。

(もっと読む)

半導体記憶装置

【課題】高周波数動作化や高速化が可能な半導体記憶装置を提供する。

【解決手段】複数のメモリセルを有するSRAMコア47と、ロウアドレス及びカラムアドレスを含むアドレスをクロックに同期してインクリメントし、インクリメントしたアドレスを順次出力するアドレスカウンタ41aと、アドレスカウンタ41aから出力されたアドレスにおいて、ロウアドレスが切り替わるアドレスの前のアドレスを検知し、検知信号を出力するカウンタアドレス検知回路42aと、カウンタアドレス検知回路42aから出力される検知信号に応じて、メモリセルに接続されたビット線に対してプリチャージ動作を行うイコライズ制御回路46aとを備える。

(もっと読む)

半導体記憶装置

【課題】同期動作の高速化が可能な半導体記憶装置を提供する。

【解決手段】第1のバンク数を有するBootRAMと、第1のバンク数より多い第2のバンク数を有するDataRAMと、BootRAMおよびDataRAMに設けられたビット線に対して行うプリチャージ動作を制御するイコライズタイマ制御回路42とを備える。イコライズタイマ制御回路42は、クロックに同期して動作する同期動作をBootRAMに対して行う際、アドレスADDを受け取った後、最初の第1プリチャージ動作の終了後から次の第2プリチャージ動作が開始されるまでの間に、第2プリチャージ動作を第1プリチャージ動作と異なる動作時間に切り替える。

(もっと読む)

半導体記憶装置

【課題】レプリカ遅延時間を量子化し、その結果に基づいて最適なセンスアンプ回路の活性化タイミングを生成する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のワード線、ワード線に交差する複数のビット線、ワード線及びビット線の各交差部に設けられた複数のメモリセルからなるメモリセルアレイと、ビット線の信号レベルを検知・増幅する複数のセンスアンプ回路と、レプリカワード線、レプリカワード線に交差するレプリカビット線、レプリカワード線及びレプリカビット線の各交差部に設けられたレプリカメモリセルからなり、メモリセルの読み出し動作を模擬するレプリカ回路と、基準タイミングから前記レプリカビット線が変化するまでの時間であるレプリカ遅延時間を量子化し、その結果に基づいて、センスアンプ回路の活性化タイミングを生成するタイミング発生回路とを有する。

(もっと読む)

複数の電圧領域を使用した回路内信号経路遅延の自己同調

信号経路の自己同調または時間調整を含む、複数の電圧領域に提供される回路および方法が開示される。上記回路には複数の信号経路が設けられている。各信号経路は、複数の電圧領域の一部を横断する。これらの領域には、任意の数または任意の組合せによる複数の電圧領域が含まれる場合がある。信号経路のそれぞれは、複数の電圧領域のうちの少なくとも1つの電圧領域に応じた遅延を有する。これら複数の信号経路の遅延に関する遅延出力を生成するように構成された遅延回路が設けられる。このようにして、これら複数の信号経路の遅延に従い、遅延回路の遅延出力が自己同調または調整される。この自己同調は、動作中に相互の信号経路の遅延が変わりうる、第1信号経路の第2信号経路に対する遅延を制御するのに特に適している。  (もっと読む)

(もっと読む)

P型評価を有するレジスタ・ファイル回路

【課題】新規なレジスタ・ファイル(RF)の実施例が提供される。

【解決手段】1またはそれ以上の評価ノードに、プリチャージされた高レベルのノードを使用する代わりに、評価の前にディスチャージされた(低レベルの)評価ノードを使用し、ディスチャージされた状態で評価に入る。いくつかの実施例では、このような「常時低レベルの」評価ノードを用いて、論理がそのように命令する場合には、評価フェーズ中に評価ノードをチャージするために、プルダウン装置ではなくプルアップ・スタック装置を使用する。

(もっと読む)

セルフタイミング回路を有する半導体メモリ

【課題】通常メモリセルの保持データの誤読み出しを確実に防止することが可能な半導体メモリを提供する。

【解決手段】半導体メモリのセルフタイミング回路において、ダミーワード線に接続され通常レイアウトユニットから構成されたセルフタイミング用ダミーメモリセルが連続して配置された第1のダミービット線と、ダミーワード線に接続され通常レイアウトユニットと点対称又は線対称の関係を有する対称レイアウトユニットから構成されたセルフタイミング用ダミーメモリセルが連続して配置された第2のダミービット線と、第1のダミービット線及び第2のダミービット線を入力し、そのうち電位の変化速度の遅い方のダミービット線の電位変化に基づいて、セルフタイミング信号を出力するタイミング制御回路とを備える。

(もっと読む)

ローカル・クロック生成器の自己タイミング型較正を用いた拡張された電圧又はプロセス範囲にわたるSRAM性能の最適化

【課題】 ローカルに生成されたクロック信号を用いて、スタティック・ランダム・アクセス・メモリ(SRAM)のようなメモリ・アレイを動作させる方法を提供する。

【解決手段】 遅延回路が、低い電圧レベルの固定遅延経路と、レベル・コンバータと、高い電圧レベルの調整可能遅延経路とを有する。固定遅延経路は、インバータ・チェーンを含み、調整可能遅延経路は、回路出力に選択的に接続された直列接続遅延要素を含む。スタティック・ランダム・アクセス・メモリ(SRAM)のローカル・クロック・バッファのための用途において、低い電圧レベルは、ローカル・クロック・バッファのものであり、高い電圧レベルはSRAMのものである。これらの電圧は、動的電圧スケーリングに応じて変化することがあり、調整可能遅延経路の再較正を必要とする。同時読み取り動作が正しい出力を返すまでSRAMアレイの読み取りアクセス時間を徐々に増大させることによって、又は、複製SRAM経路を用いて電源の変化に伴う遅延の変動をシミュレートすることによって、調整可能遅延経路を較正することができる。

(もっと読む)

動的、かつリアルタイムなディレイ特徴化、及び設定

ストラクチャードASICのようなマスクプログラム可能な集積回路でディレイチェーンがマスクプログラム可能なスイッチで設定されるディレイを提供する。ディレイチェーンは、入力を受け、マスクプログラムされたディレイをJTAG制御器の使用で無効化させる。これにより異なるディレイが試験可能となる。入力はヒューズブロックから供されても良く、この場合、ヒューズブロックが マスクプログラム可能なスイッチを無効化し、マスクでプログラミングの後のディレイ変更が可能となる。 (もっと読む)

メモリ回路におけるデュアル電力スキーム

【解決手段】半導体メモリデバイスは、低レベルアドレス信号を高レベルアドレス信号に変換するように構成されたアドレス信号レベルシフタを含む。デコーダ(102)は、前記高レベルアドレス信号を受信し、それに応じてワード線信号を供給するように構成される。書き込みドライバ(305)は、低レベルデータ入力信号を受信し、前記受信した入力に応じてビット線(109)を構成する。メモリセル(111)は、前記ワード線信号、及びそこにデータを記憶するために構成されたビット線に応答する。 (もっと読む)

メモリ装置

【課題】ビット線やワード線のクロスカップリングノイズを低減する。

【解決手段】メモリセルに読み出し制御信号を伝える1つ以上の読み出しワード線15、16、17と、読み出しワード線にそれぞれ対応し読み出し制御信号の活性化に応じてメモリセルの情報を外部に伝送する1つ以上の読み出しビット線18、19、20と、メモリセルに書き込み制御信号を伝える1つ以上の書き込みワード線11、12と、書き込みワード線にそれぞれ対応し書き込み制御信号の活性化に応じて外部の情報をメモリセルに伝送する1つ以上の書き込みビット線13、14とを備え、読み出しビット線と書き込みビット線とを可能な限り交互に配置し、前記読み出し制御信号と前記書き込み制御信号とを同時に活性化しないように制御する。

(もっと読む)

半導体記憶装置

【課題】配線層の増加を招くことなくデータ入出力可能な半導体記憶装置を提供することを目的とする。

【解決手段】互いに交差する複数のワード線及び複数のビット線並びにこれらワード線及びビット線の各交差部に接続されたメモリセルを有し前記ビット線方向に配列された複数のセルアレイと、前記複数のセルアレイ間に設けられ隣接セルアレイのビット線間を接続するビット線ゲートと、前記メモリセルに対するアクセス時に前記ビット線ゲートにより接続されたビット線間を介したデータ転送経路を形成する制御回路とを備える。

(もっと読む)

半導体集積回路装置、リダンダンシシステム

【課題】ヒューズデータの転送は行うが、ヒューズボックスから外部へのヒューズデータの転送(データ出力)は行わないヒューズデータの迂回動作を行うことができ、利便性を向上できる半導体集積回路装置およびリダンダンシシステムを提供する。

【解決手段】半導体集積回路装置は、ヒューズデータをラッチするヒューズラッチ回路12と、ヒューズカウンタ回路13と、前記ヒューズデータを外部に転送する転送回路16と、前記ヒューズデータを転送しない場合に前記ヒューズデータを外部に転送せず自身の中で迂回させる迂回データパスを形成する迂回データパス回路17とを備える制御回路15とを具備するヒューズボックス11において、前記迂回データパス回路17は、前記ヒューズカウンタ回路から送信される制御信号を受信すると、前記ヒューズラッチ回路から次のヒューズデータを要求するリクエスト信号REQを前記ヒューズカウンタ回路13に動作させる。

(もっと読む)

1 - 20 / 44

[ Back to top ]