Fターム[5B018GA01]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | エラー検出 (217)

Fターム[5B018GA01]に分類される特許

1 - 20 / 217

メモリアクセス制御装置および方法

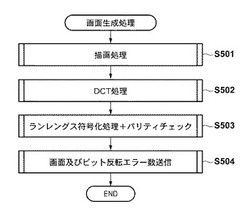

描画サーバ、センタサーバ、符号化装置、制御方法、符号化方法、及びプログラム

【課題】符号化処理を利用した効率的なメモリ検査を行う。

【解決手段】検査対象のメモリについてパリティ情報を付加したデータをメモリに書き込んだ後、該データをメモリから読み出してランレングス符号化処理を行って符号化データを生成する。符号化装置は、書き込まれたデータについてビット列を参照して符号化データを生成する際に、該ビット列と付加されているパリティ情報とを比較してビット反転エラーを検出する。

(もっと読む)

遠隔装置に搭載される情報処理装置及び情報処理装置の起動方法

【課題】コンピュータプログラムを予め記憶したROMを必要とせず、かつコンピュータプログラムの破損を容易に解消させる、ことを目的とする。

【解決手段】情報処理装置10は、遠隔操作によって動作する遠隔装置に搭載され、コンピュータプログラムを実行するCPU20、及び該コンピュータプログラムを記憶する書き込み可能なRAMを備え、地上局50が備える送受信装置52から送信されるコンピュータプログラムを受信し、受信したコンピュータプログラムをRAMへ転送し、RAMにコンピュータプログラムが記憶されている状態でCPU20を起動させる。

(もっと読む)

メモリデバイス群間でのチェックビットメモリデバイスの共有

【課題】 メモリデバイス群間でのチェックビットメモリデバイスの共有を提供する。

【解決手段】 エラー検出および訂正(EDC)範囲をサポートするメモリシステム。メモリシステムは、データを格納する少なくとも2つのメモリデバイス群と、両方のメモリデバイス群のためにエラーチェック情報(例えば、エラー訂正コード)を格納する別のメモリデバイスとを備えたメモリモジュールを含む。また、メモリモジュールは、データが第1のメモリデバイス群によって転送されるかまたは第2のメモリデバイス群によって転送されるかに基づいて、エラーチェック情報にアクセスするためのアドレスを決定するメモリバッファも含む。あるいは、メモリコントローラは、メモリバッファの必要性を低減または排除するために、エラーチェック情報にアクセスするためのアドレスを決定することができる。

(もっと読む)

不揮発性メモリシステムのためのウィーブシーケンスカウンタ

【課題】不揮発性メモリ(NVM)システムのためのウィーブシーケンスカウンタ(WSC)を形成するシステム及び方法を提供する。

【解決手段】WSCは、NVMの各ページがプログラムされるシーケンスを識別する。「ウィーブ(weave)」とは、複数のブロックを、一度にプログラムするためにオープンにし、従って、それらのブロックのページを「織る」ようにプログラムするのを許すことを指す。ホストウィーブシーケンスカウンタ(HWSC)を形成するシステム及び方法も開示される。新たなデータがNVMへ最初にプログラムされるたびに、そのデータが特定のHWSCに関連付けられる。データに関連付けられたHWSCは、データが新たなページへ移動されたときでも(例えば、ウェアレベリングの目的、等のために)、変化することがない。

(もっと読む)

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置を提供する。

【解決手段】メモリ・システム100は、ホスト110とメモリ・デバイス120との間でデータを転送するためにデータ・フレームを使用する。いくつかの場合には、システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。いくつかの実施形態では、データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

メモリ制御装置

【課題】 冗長化した半導体メモリのデータ記録制御を行う従来のメモリ制御装置は、半導体メモリに格納した符号化データを復号する場合に、半導体メモリの故障情報を利用していないため、宇宙環境での冗長化されたデータの記録再生に係る信頼性を十分に高められなくなっている。

【解決手段】 ハミング符号を用いて複数の半導体メモリに冗長化してデータを記録し、ハミング符号を復号して、データが誤りの場合にはメモリ故障と判定してデータ誤りのある半導体メモリを除いてから多数決処理を行うことにより、冗長化前の正しいデータを再生することができる。

(もっと読む)

フィールド機器

【課題】不揮発性メモリへの書き込み途中で電源がオフとなったことで発生したSUM値不一致の現象と、EEPROMデバイスやハードウェアの異常によりEEPROMのデータの信頼性が欠如した状態を明確に切り分けて判断することができるフィールド機器を実現する。

【解決手段】フィールド機器のCPUがアクセスするデータを保存するための不揮発性メモリが、サブブロックで構成され、前記CPUが各サブブロックに前記データを保存した際にデータのSUM値を前記不揮発性メモリに保持させるフィールド機器において、

前記不揮発性メモリは、前記サブブロックに対応して2個のSUM値を保持する領域を有し、

前記CPUは、前記サブブロックに変更データを保存する際に、1つ目のSUM値を更新した後に前記変更データを前記サブブロックに書き込み、さらに2つ目のSUM値を更新する。

(もっと読む)

半導体装置及びそのデータ異常判定方法

【課題】記憶手段を有する第1チップと、記憶手段に対してメモリデータの読み出しを指示する指示手段、及び、少なくとも多数決により、読み出された制御用データの信頼性を判定する判定手段を有する第2チップと、を備える半導体装置において、データ信頼性を向上しつつ、第2チップの体格増大を抑制する。

【解決手段】制御用データは、記憶先のアドレスの一部に対応するチェック用データが付加されてなるメモリデータとして、1つの制御用データにつき異なる3つのアドレスに記憶される。1つの制御用データに関する各アドレスにおいて、チェック用データに対応する一部を除く部分は、互いに異なるとともに複数の制御用データで同じとされる。また、3つのメモリデータに関し、制御用データ同士、チェック用データ同士、及び該チェック用データに対応するアドレスの一部同士は、それぞれ同じ或いはミラー反転の関係にある。

(もっと読む)

マイクロコンピュータ及び異常メモリアクセス検出方法

【課題】余計な命令コードを追加することなく、マイクロコンピュータにおける異常メモリアクセスの発生を検出すること。

【解決手段】メモリへのアクセス発生時、XOR処理器は、アクセス対象データのデータ幅に依存して異なる係数とアクセス対象データとのXOR演算を行う。パリティ生成回路は、XOR演算の演算結果に基づいて、アクセス対象データに関連するパリティビットを生成する。書き込みアクセス時、パリティ処理回路は、パリティ生成回路によって生成されたパリティビットをメモリに書き込む。読み出しアクセス時、パリティ処理回路は、パリティ生成回路によって生成されたパリティビットとメモリから読み出されるパリティビットとを比較し、それらが不一致である場合、割り込み信号をCPUに出力する。

(もっと読む)

メモリシステム

【課題】

実施形態は、信頼性を向上可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、複数のワード線と、複数のビット線と、制御ゲートに前記ワード線が接続され、ドレイン端に前記ビット線が接続されたメモリセルと、複数の前記メモリセルを含むページ、複数の前記ページを含むブロックを有するメモリセルアレイと、前記ページごとに不良の前記ビットの個数が第1閾値以下である良ブロックに関するデータが保持された記憶領域とを備え、前記第1閾値は、不良ブロックか否かの判定に用いる第2閾値よりも小さいことを特徴とする。

(もっと読む)

メモリコントローラ及び情報処理装置

【課題】読み出しデータの3bitエラーを考慮した上で、訂正可能エラーを判別することを可能にするメモリコントローラ及び情報処理装置を提供する。

【解決手段】ECC機能付きメモリモジュールに接続され、メモリモジュールへのアクセスを制御するメモリコントローラにおいて、メモリモジュールから読み出された複数の読み出しデータについて、読み出しデータに対応するECCの符号情報を、メモリモジュールより読み出して、エラービットの有無及びエラービットの位置の検出を行うエラー検出部と、複数の読み出しデータを一時的に格納するバッファと、バッファに格納された複数の読み出しデータに、エラー検出部によって訂正可能エラーが検出されたデータが複数含まれ、かつ、検出されたデータのエラー検出位置が同じ場合に、複数の読み出しデータ全体として訂正可能なエラーを含むと判定する判定部と、を備える。

(もっと読む)

メモリ書き込み確認装置、メモリ書き込み確認方法およびプログラム

【課題】データの正常性だけでなく、書き込みアドレスの正常性も確認する。

【解決手段】書き込み部11は、メモリ12にデータを書き込み、計算部13は、書き込み部11がメモリ12に書き込んだデータのデータ・チェックサム値とデータを書き込んだアドレスのアドレス・チェックサム値とを計算し、データ・チェックサム値とアドレス・チェックサム値を合計したチェックサム合計値を計算する。表示部14は、データ・チェックサム値とチェックサム合計値を表示する。

(もっと読む)

異常検出装置、および異常検出プログラム

【課題】データ記録領域に記録されたデータの異常を検出する異常検出装置において、効率的かつ確実にデータの異常を検出できるようにする。

【解決手段】異常検出ECUは、RAMへのデータの書き込み時およびRAMからのデータの読み出し時に、所定の同様のアルゴリズムに従って書き込むデータの内容に応じた値であるCRC値を生成させ、これらのCRC値を比較し、この比較結果が不一致であればデータに異常がある旨の判定をする(S330,S340,S370)。この異常検出ECUによれば、RAMへデータを記録するとき(書き込み時)と利用するとき(読み出し時)とでデータが変化していないかどうかを確認するので、確実にデータの異常を検出することができ、周期的にデータの異常を検出する構成と比較して、データの異常を検出する処理を実施する回数を少なくすることができるので、効率的にデータの異常を検出する処理を行うことができる。

(もっと読む)

メモリエラーパターン記録システム、メモリモジュール、及びメモリエラーパターン記録方法

【課題】コントローラやメモリモジュールを交換してもメモリモジュールに発生したエラーを再現する。

【解決手段】メモリモジュール1が、メモリデバイス12−1〜12−Nと、メモリデバイス12−1〜12−Nへのアクセスパターンであってエラーが発生するアクセスパターンを記憶する不揮発性メモリ17と、コントローラ2によるメモリデバイス12−1〜12−Nへのアクセスによってエラーが発生したか否かを判定するエラー検出回路15と、エラー検出回路15によって、エラーが発生したと判定された場合、不揮発性メモリ17にコントローラ2によるアクセスパターンを記録するアクセス情報記録回路16とを備える。

(もっと読む)

NORフラッシュメモリの読み取り方法

【課題】NORフラッシュメモリの読み取り方法を提供する。

【解決手段】

本発明は、NORフラッシュメモリの読み取り方法を提供し、組込み式Linuxオペレーションシステムで使用され、巡回冗長検査値を照合し、カウンタに予め設けられた繰り返し読み取り回数の閾値により、ジャーナリングファイルシステムデータの繰り返し読み取りを継続するか否かを決定する。

(もっと読む)

半導体ディスク装置

【課題】複数の半導体ディスク3a、3bによりデータを記録する半導体ディスク装置1において、高信頼性を維持し、処理量およびオーバーヘッドを少なくする。

【解決手段】複数の半導体ディスク3a、3bによりミラーリング構成を成し、一の半導体ディスク3aの任意のアドレスにてセクタエラーを検出したときに、他の半導体ディスク3bから当該アドレスのデータを読み出して、前記一の半導体ディスク3aの前記アドレスに上書きするとともに、バックグラウンドにて一の半導体ディスク3aまたは3bの全アドレスのセクタエラーを検出しセクタエラーが検出されたときは他の半導体ディスク3bまたは3aから当該アドレスのデータを読み出して前記一の半導体ディスク3aまたは3bの前記アドレスに上書きするベリファイ動作を全ての半導体ディスクについて行うようにした。

(もっと読む)

画像処理装置及び画像記録装置

【課題】 第1演算部と挿脱可能な外部メモリに接続される第2演算部とを備え、外部メモリの不具合を検出してユーザに通知することができる画像処理装置を提供する。

【解決手段】 プリンタ装置1の画像処理装置2は、メインCPU5と、サブCPU6と、外部メモリ11を挿脱可能なメモリスロット10とを備え、メモリスロット10は、外部メモリ11のSPD領域11bにアクセス可能な端子10bを有し、該端子10bはメインCPU5に接続されている。そして、メインCPU5は、サブCPU6の起動に先立ち、端子10bを介してSPD領域11bにアクセスし、外部メモリ11のエラーチェックを行うように構成されている。

(もっと読む)

電子機器、及び、電子機器の制御方法

【課題】セクターが形成される不揮発性メモリーにおいて、セクターの使用効率を向上する。

【解決手段】フラッシュメモリー28の記憶領域に、複数のセクターを形成し、これら複数のセクターに、バンク単位で巡回的にデータを書き込み、複数のセクターうち1のセクターに対してバンクを書き込む際に、書き込みエラーが発生した場合、1のセクターに既に正常に書き込みが終了しているバンクを他のセクターにコピーし、新たなバンクの書き込みは、他のセクターに対して行うようにした。

(もっと読む)

擬似エラー発生装置

【課題】半導体メモリに擬似的にエラーを発生させる擬似エラー発生装置を提供する。

【解決手段】乱数によって決定されるメモリのアドレスのデータの情報ビットと冗長ビットの両方を、エラー検出やエラー訂正しないで読み取り、同じく乱数によって決定されるビット位置のビットを反転させ、同じメモリの同じアドレスにビット反転させたデータを書き込む。反転させるビット数は、どのようなエラーを擬似的に発生させたいかによって、1ビット、2ビット以上など、適切に設定する。

(もっと読む)

1 - 20 / 217

[ Back to top ]