Fターム[5B018GA10]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | その他 (15)

Fターム[5B018GA10]に分類される特許

1 - 15 / 15

データ処理装置およびその制御方法

メモリコントローラ、半導体記憶装置および復号方法

【課題】複雑な処理を行わずに回路規模を低減することができるメモリコントローラを得ること。

【解決手段】メモリコントローラであって、メモリ部へ書き込むデータとデータに対する誤り検出符号とデータおよび誤り検出符号に対するt(tは2以上の整数)シンボル訂正可能な誤り訂正符号とをn個のチャネルごとにメモリ部へ書き込み、データと誤り検出符号と誤り訂正符号とを読み出しデータとしてチャネルごとにメモリ部から読み出すメモリインタフェースと、チャネルごとの読み出しデータに対してs(s<t)シンボル訂正可能な第1の誤り訂正復号化処理を実施するn個の第1の誤り訂正復号化部と、第1の誤り訂正復号化処理の復号結果に基づいてチャネルごとに誤り検出処理を行うn個の誤り検出部と、誤りが検出されたチャネルの読み出しデータに対してtシンボル訂正可能な誤り訂正復号化処理を実施する第2の誤り訂正復号化部と、を備える。

(もっと読む)

半導体システム

【課題】複数のエリアを有する半導体システムにおいて不使用エリアにおける消費電力を削減する。

【解決手段】内部電源発生回路70b〜70dを其々有する複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFと、を備えた半導体システムであって、前記インターフェースチップIFはコアチップCC0〜CC7の不使用チップ情報DEFを保持する不使用チップ情報保持回路33を備える。コアチップCC0〜CC7は其々対応する不使用チップ情報DEFを不使用チップ情報保持回路33から受け、該不使用チップ情報DEFが不使用状態を示すときには内部電源発生回路70b〜70dを非活性とし、使用状態を示すときには内部電源発生回路70b〜70dを活性とする。これにより、不使用チップにおける無駄な電力消費が削減される。

(もっと読む)

マスタ基板作成装置及び記録媒体

【課題】パソコンに保存されたSPDデータをパソコンに接続できない検査装置に保存する作業を短時間で簡単に行い、DIMM等の基板検査の作業効率を向上させることができる低コストで構築可能な検査システムを提供する。

【解決手段】パソコン1に接続されたマスタ基板作成装置10を用いて該パソコン内のSPDデータをそのEEPROMに記録したマスタ基板2を作成し、該マスタ基板を検査装置のソケットに装着して該マスタ基板から該SPDデータをダウンロードする。上記マスタ基板作成装置は、パソコンと接続するセントロコネクタ11と、DIMMを装着可能な2つのソケット13a,13bと、該セントロコネクタを介して入力されたSPDデータを該ソケットに装着されたDIMM上のEEPROMに書き込む書込制御部が設けられている。

(もっと読む)

メモリ装置

【課題】数十年以上の単位で記録データを長期的に安定に保存でき、しかも保存データを確実に読み出し可能なメモリ装置を提供する。

【解決手段】第1回路200は、データ記録回路210と、第2回路300からの読み出しまたは書き込み指示を受けて、アドレス信号に応じてデータ記録回路に対するデータの書き込みおよび読み出し制御を行う書き込み読み出し制御回路230と、を含み、第2回路300は、第1回路とのデータ転送制御を行うデータ転送制御回路310と、データ転送制御回路の作業用メモリ320と、を含み、データ転送制御回路310は、第1回路200のデータ記録回路210への書き込みデータを、いったん作業用メモリ320に蓄積し、蓄積したデータを順次に第1回路側の書き込み読み出し制御回路230に転送する。

(もっと読む)

性能要因調整に基づくメモリ・デバイスの軟データ生成の方法および装置

性能要因調整に基づくメモリ・デバイスの軟データ生成の方法および装置を提供する。少なくとも1つの軟データ値が、少なくとも1つの読取値を入手することと、入手された少なくとも1つの読取値とメモリ・デバイスの1つまたは複数の性能要因に基づく調整とに基づいて軟データ値を生成することとによって、メモリ・デバイスについて生成される。読取値は、たとえば、データ・ビット、電圧レベル、電流レベル、または抵抗レベルを含むことができる。読取値は、軟データまたは硬データである。可能な性能要因は、耐久性、読取サイクルの個数、保持時間、温度、プロセス・コーナー、セル間干渉影響、メモリ・アレイ内の位置、およびアグレッサ・セルのパターンを含む。1つまたは複数のパターン依存性能要因および/または位置固有性能要因を考慮することもできる。生成される軟データ値は、1つまたは複数の対数尤度比を生成するのに使用される軟読取値とすることができ、あるいは、対数尤度比自体とすることができる。  (もっと読む)

(もっと読む)

情報処理装置およびデータ退避方法

【課題】 電源停止処理時における退避するデータ数を削減し、速やかに電源停止処理を行える情報処理装置を提供する。

【解決手段】 情報処理装置1は、所定の処理を実行するデバイス12と、退避すべきデータを記憶する退避メモリ18と、退避すべきレジスタ14のアドレスを記憶するバス監視用テーブル22と、処理部に接続されたバスを流れるデータを監視し、データの送信先あるいは送信元がバス監視用テーブル22で示されたアドレスである場合、当該データを退避メモリ18に書き込むバス監視部20とを備える。

(もっと読む)

ディスクアレイコントローラ

【課題】 ホストシステムのOSに依存することなく相対的に大容量のログ情報とともに最新の時刻情報を記録でき、信頼性の高いディスクアレイコントローラを提供する。

【解決手段】 ホストシステムからのアクセス要求に応じて、ディスクアレイ構成の各ディスクドライブに対するデータの入出力を制御手段と、ディスクドライブにおいてホストシステムが関与するユーザデータ記録領域以外のリザーブ領域に特定領域を設定し、各ディスクドライブでのイベント発生に従ったログ情報を特定領域に記録する記録手段と、この特定領域に時刻情報を書き込むための時刻情報記録領域を設け、ホストシステムの動作中に時刻情報記録領域に対して定期的に最新時刻の書き込みを行う時刻情報更新手段とを持つRAIDコントローラ。

(もっと読む)

ストレージシステム及びストレージシステムのライト性能低下防止方法

【解決課題】ストレージシステムのライト性能の低下を抑制する。

【解決手段】フラッシュメモリと、キャッシュメモリと、フラッシュメモリのデータの読み出し、書き込み及び消去と、キャッシュメモリのデータの読み出し及び書き込みを制御し、フラッシュメモリ内に不良なブロックが発生したことを検出するコントローラと、データのライト処理を要求するコマンドを発行するホスト計算機とを含むストレージシステムにおいて、コントローラは、フラッシュメモリ内に不良ブロックが発生したことを検出すると、フラッシュメモリに格納された所定のデータをキャッシュメモリに移動し、その移動したデータを更新するためのコマンドをホスト計算機から受信しても、そのコマンドに基づくデータをフラッシュメモリへ書き込むことを禁止する。

(もっと読む)

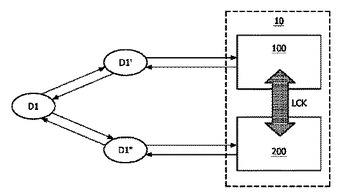

安全な不揮発性メモリ装置およびその内部データを保護する方法

本発明は、不揮発性メモリ装置に関し、この不揮発性メモリ装置は、格納すべき外部データ(D1)を不揮発性メモリ装置に供給する入力と、第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)と、を備え、第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)を、単独のチップ(10)上に設け、第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)は異なるタイプの構成とし、これにより第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)の双方に分散して(D1′、D1″)格納した外部データ(D1)から、データを取得するためには、第1不揮発性メモリブロックおよび第2不揮発性メモリブロックは互換性のない外部攻撃技術を必要とする。本発明は、さらに不揮発性メモリ装置内のデータを保護する方法に関する。  (もっと読む)

(もっと読む)

行列ストライプキャッシュを利用したRAIDシステムの入出力性能を向上させる方法

【課題】行列ストライプキャッシュを利用したRAIDシステムの入出力性能を向上させる方法を提供する。

【解決手段】行列ストライプキャッシュ(MSC)によって入出力を行単位で決定した後、列単位で各要素を読出しと書込み毎に結合を試みて入出力の数を減らして断片化された書込みの性能を向上させ、低下モードの小さな読出し性能を犠牲にして一般モードの読出し性能を向上させる。本発明は、ディスクに書込みを行う単位MSCから行結合前の読出し書込み行列であるrxw行列を生成し、第1ステップで生成された行結合前rxw行列から行結合によって最終読出し書込み行列である行結合されたrxw行列を生成し、第2ステップで生成された行結合されたrxw行列をパターンとして読出しを実行し、行結合されたrxw行列の各行毎にXOR演算を実行し、行結合されたrxw行列の各列毎に書込みを実行する。

(もっと読む)

半導体記憶装置

【課題】複数のメモリチップ間で初期化動作期間にばらつきが生じたとしても、それぞれのビジー状態を示すビジー信号を出力するI/O端子を介して複数のメモリチップ間で電源電圧と接地電圧との間がショートすることを防止する。

【解決手段】複数のメモリチップMC1 、MC2 と、これらに対応して設けられ、電源投入後に電源電圧の値が仕様保証範囲に達した際にビジー状態にされ、複数のメモリチップの初期化動作が完了するまでの間中ビジー状態が維持され、複数のメモリチップの初期化動作が全て完了した後にビジー状態が解除されるビジー信号がそれぞれ出力されるI/O端子13を具備したことを特徴としている。

(もっと読む)

不揮発性論理回路及びそれを有するシステムLSI

【課題】 マイコンやDSP回路などの論理回路を組み合せたシステムにおいてシステムが複雑になるにつれて、起動時の各論理回路の初期化時間が長時間化する課題があった。

【解決手段】 複数の論理回路から構成され、データバス線との間においてデータの入出力が行われる論理回路ブロックであって、前記データバス線に接続された入出力部に不揮発性データ保持回路を有することを特徴とする不揮発性論理回路とすることで、初期化データをインターフェース部分に持たせ、データバスを用いずに短時間で論理回路を初期化することが可能となる。また、インターフェース部の入出力データを不揮発性メモリに記憶することで、電源投入時に以前の状態に戻すレジューム動作が可能となるなどの優れた特性改善効果が得られる。

(もっと読む)

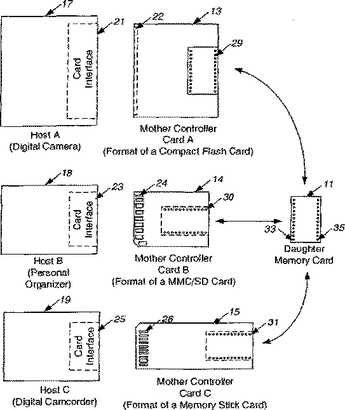

メモリコントローラを備える様々な異なる規格のカードとともに用いられる汎用不揮発性メモリカード

マザー/ドーターカード不揮発性メモリシステムは、メモリを含むドーターカードと、メモリコントローラおよびホストインタフェース回路を備えるマザーカードとを備える。ドーターメモリカードは、そのコストを最小限にするために、可能な限り少ないメモリセルアレイを備え、多くの異なる発行されたメモリカード規格または知的所有権下にあるメモリカード規格に従う物理的属性およびホストインタフェースを有するいろいろなマザーコントローラカードと接続するためのインタフェースを有する。メモリカード内の保護された位置にメモリの動作パラメータが蓄積されるときに種々のタイプのメモリカードを使用することができ、マザーカードコントローラはこれらのパラメータを読み出し、かつそれに応じてその動作を適応させる。無線周波数識別機能を提供するために、無線周波数アンテナをカード表面にその電気接点とともに備えることができる。  (もっと読む)

(もっと読む)

フラッシュメモリのアクセス方法

【課題】フラッシュメモリに格納されているデータが更新されたとき、旧いデータを格納するブロックには“旧”のフラグを書き込んでいた。しかし、多値メモリではフラグに書き込むことが困難であり、新旧を判断する他の方法が求められている。

【解決手段】フラッシュメモリを用いたメモリカードに、論理アドレスに関連付けられて格納されているデータを更新するとき、更新される前のデータが格納されたブロックの物理アドレスを起点に、昇順方向にたどって使用可能で未使用の最初のブロックに最新のデータを格納する。そして、ある論理アドレスの最新のデータが格納されたブロックを求めるときは、フラッシュメモリの使用可能で未使用のブロックの中で物理アドレスが最大の値を求め、降順方向にたどって求める論理アドレスのデータが格納されたブロックの最初のブロックに格納されていると判断する。

(もっと読む)

1 - 15 / 15

[ Back to top ]