Fターム[5B018HA21]の内容

記憶装置の信頼性向上技術 (13,264) | 手段 (2,627) | 故障位置情報(エラーポインタ) (87)

Fターム[5B018HA21]に分類される特許

1 - 20 / 87

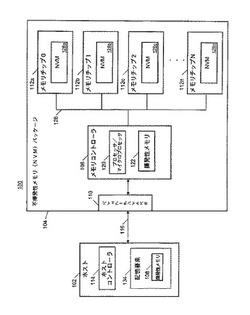

不揮発性メモリの正常性情報を取得して使用するためのシステム及び方法

【課題】不揮発性メモリ(「NVM」)の正常性情報を取得して使用するためのシステム及び方法を提供する。

【解決手段】正常性情報は、NVMの一部で検出されたエラー数、又は不揮発性メモリの一部から読み取りを行うために又はこのメモリの一部をプログラムするために必要な時間量などの、NVM装置の一部の性能及び信頼性に関連する様々な情報を含むことができる。動作中、ホスト装置上にアドレス固有の正常性情報を受動的に記憶し、コマンドの一部としてメモリコントローラに提供することができる。メモリコントローラは、このコマンドから正常性情報を抽出し、この情報を使用してアクセス要求を実行することができる。アクセス要求の完了後、メモリコントローラは正常性情報を更新し、この情報をホスト装置へ返送することができる。

(もっと読む)

不揮発性メモリシステムのためのウィーブシーケンスカウンタ

【課題】不揮発性メモリ(NVM)システムのためのウィーブシーケンスカウンタ(WSC)を形成するシステム及び方法を提供する。

【解決手段】WSCは、NVMの各ページがプログラムされるシーケンスを識別する。「ウィーブ(weave)」とは、複数のブロックを、一度にプログラムするためにオープンにし、従って、それらのブロックのページを「織る」ようにプログラムするのを許すことを指す。ホストウィーブシーケンスカウンタ(HWSC)を形成するシステム及び方法も開示される。新たなデータがNVMへ最初にプログラムされるたびに、そのデータが特定のHWSCに関連付けられる。データに関連付けられたHWSCは、データが新たなページへ移動されたときでも(例えば、ウェアレベリングの目的、等のために)、変化することがない。

(もっと読む)

故障位置判定回路、記憶装置、および情報処理装置

【課題】記憶装置で発生したエラーに対して、簡易かつ的確にエラーを解析し、エラーの状況を取得できるようにする。

【解決手段】故障解析回路は、故障がある記憶領域に記憶された故障データと交替レジスタのデータとを比較する比較回路と、比較回路による比較結果データからエラービット位置を特定する位置特定回路と、を備える。

(もっと読む)

診断装置、診断方法および診断プログラム診断方法

【課題】コンピュータシステムのメモリ部の障害の被疑部位を高速かつ正確に特定する診断装置を提供する。

【解決手段】コンピュータシステム100のメモリ部3にアクセスしてエラーが発生した際に、診断装置10は、エラー発生時のメモリ読み出しアドレスおよびメモリ読み出しデータのエラービットをそれぞれ読み出しアドレス保持回路15およびエラービット保持回路12に保持し、診断読み出しアドレス生成回路16および診断読み出しコマンド生成回路14からメモリ読み出し制御部2に指示してエラー発生時の同一メモリ読み出しアドレスに再度アクセスするリトライ動作を実施させ、リトライ結果として、エラービット比較回路13において再度同一のエラービットが発生するか否かの比較結果131に基づいて、診断制御回路17は、固定障害か否かを判別し、固定障害と判別した場合エラーが発生した部位を中心に切り分けテストを行い、障害被疑部位を特定する。

(もっと読む)

自動車用電子制御装置

【課題】不揮発性メモリの記憶領域に故障が発生しても、情報の蓄積に支障がないようにする。

【解決手段】イグニッションスイッチがOFFになったことを契機として、不揮発性メモリに故障情報を書き込むときに、故障が発生していない記憶領域を選定し(S1)、記憶領域の全領域に消去データを書き込み(S2,S3)、消去データの確認により消去できたか否かを判定する(S4,S5)。記憶領域が消去できなかった場合、故障が発生していない他の記憶領域に素子異常情報を書き込む(S16)。また、イグニッションスイッチがONになったことを契機として、不揮発性メモリから故障情報を読み込むときに、チェックサムを利用して異常を検知し、故障が発生していない他の記憶領域に素子異常情報を書き込む。そして、素子異常情報を計数した計数値が所定の閾値以上である記憶領域は、故障が発生していると判定し、その使用を禁止する。

(もっと読む)

メモリコントローラ及び情報処理装置

【課題】読み出しデータの3bitエラーを考慮した上で、訂正可能エラーを判別することを可能にするメモリコントローラ及び情報処理装置を提供する。

【解決手段】ECC機能付きメモリモジュールに接続され、メモリモジュールへのアクセスを制御するメモリコントローラにおいて、メモリモジュールから読み出された複数の読み出しデータについて、読み出しデータに対応するECCの符号情報を、メモリモジュールより読み出して、エラービットの有無及びエラービットの位置の検出を行うエラー検出部と、複数の読み出しデータを一時的に格納するバッファと、バッファに格納された複数の読み出しデータに、エラー検出部によって訂正可能エラーが検出されたデータが複数含まれ、かつ、検出されたデータのエラー検出位置が同じ場合に、複数の読み出しデータ全体として訂正可能なエラーを含むと判定する判定部と、を備える。

(もっと読む)

ディスクアレイ制御装置及びそのダンプファイル採取方法

【課題】本発明は、信頼性を向上させ得るディスクアレイ装置を提案する。

【解決手段】ホスト計算機から送信されるデータを物理ディスクに読書きすると共に、ログデータを不揮発性メモリに格納する第1の制御部と、前記第1の制御部の動作内容が記憶されるメモリと、外部記憶媒体を接続するためのコネクタと、障害が発生したときに押下されるスイッチと、前記コネクタに前記外部記憶媒体が接続されていることを条件に、前記メモリに記憶されている前記第1の制御部の動作内容をダンプファイルとして直接前記メモリから採取して、前記コネクタを介して前記ダンプファイルを前記外部記憶媒体に格納する第2の制御部とを備えることを特徴とする。

(もっと読む)

コンピュータ、制御方法、及びプログラム

【課題】アクセス数の少ないメモリモジュールへのアクセス頻度に拘らず、エラーが発生したメモリモジュールに対してメモリチェックを行い、メモリモジュールの故障を早期に発見する。

【解決手段】コンピュータ100は、エラー検出部110、ログ収集部120、診断部130、メモリチェック部140、障害処理部150、及び障害ログ情報格納部160を備え、メモリチェック部140は、診断機能によって特定されたメモリエラーが発生した位置に対してメモリチェックを行い、メモリアクセスを行い、メモリエラーが発生するかどうかの確認を行う。

(もっと読む)

記憶装置、及び制御方法

【課題】フラッシュメモリの交換、取り外しに適切に対応する。

【解決手段】実施の形態の記憶装置は、識別情報記憶手段と、位置情報記憶手段と、判定手段と、制御手段と、を備える。識別情報記憶手段は、ホストからのアクセスの対象となる不揮発性メモリを識別する識別情報を複数記憶する。位置情報記憶手段は、不揮発性メモリの不良領域を識別する位置情報を記憶する。判定手段は、自装置に接続されている複数の不揮発性メモリに格納されている識別情報のそれぞれが、識別情報記憶手段に記憶されている複数の識別情報のいずれかと一致するか否かを判定する。制御手段は、判定手段により不揮発性メモリの識別情報が識別情報記憶手段に記憶されている複数の識別情報のいずれも一致しないと判定された場合に、一致しない識別情報で識別される不揮発性メモリに対して、位置情報記憶手段に記憶された不良領域の位置情報の利用を抑止するともに、当該不揮発性メモリに対する、ホストからのアクセスを抑止する。

(もっと読む)

メモリエラー箇所検出装置、及びメモリエラー箇所検出方法。

【課題】ソフトエラー等による一時的な論理アドレスと物理アドレスとの誤変換によるデータの位置誤算出を防ぐことができて信頼性を保てるストレージ制御装置を提供する。

【解決手段】ストレージシステムは、記憶装置と、ストレージ制御装置を備え、ストレージ制御装置が、ホストから書き込み指示を受け取ったとき、ホストからの書き込み指示に含まれる論理アドレスを含む読み込み指示を記憶装置へ送るデータ読み込み指示手段と、データ読み込み指示手段からの読み込み指示に基づき、記憶装置が読み取った該当位置のデータに論理アドレスが含まれている場合に、ホストから受け取った書き込み指示に含まれる論理アドレスと読み取ったデータに含まれた論理アドレスとが異なるとき、システム領域からアドレス変換情報を読み出し、読み出したアドレス変換情報をメモリに書き込むアドレス変換情報訂正手段とを有する。

(もっと読む)

記録装置、読出装置、および、記録再生装置

【課題】フラッシュメモリに対してリアルタイムデータを記録する機器において、書き込みエラーが発生したときに、書き込みを継続するための手段が、ファイルシステムとは無関係な独自形式であるため、ファイルシステムによりデータを記録するシステムには適合できない。

【解決手段】複数のアクセスユニットで構成されるメモリを有する記録装置であって、前記メモリにデータをアクセスユニット単位で記録する記録手段と、前記記録手段で前記データを前記メモリに書き込んでいるときに、書き込みエラーを検出する書き込みエラー検出手段とを備え、前記記録手段は、前記書き込みエラー検出手段で書き込みエラーが検出されたときに、ファイルの書き込みを終了する。

(もっと読む)

メモリ障害処理システム、および、メモリ障害処理方法

【課題】予備メモリ切替とページ閉塞とを効率的に連動させてシステムダウンを防止するメモリ障害処理システムを提供すること。

【解決手段】メモリチップ21および予備メモリチップ22を有するメモリ装置2と、メモリチップ21の障害の発生回数総和をカウントする発生回数総和カウント部31と、発生回数総和が総和閾値を超えると故障したメモリチップ21を予備メモリチップ22に切り替える予備メモリチップ切替部32と、切替後の障害の発生回数をキャッシュライン単位でカウントするキャッシュライン単位カウント部33と、切替後の発生回数総和が総和閾値を超える前にキャッシュライン単位発生回数がキャッシュライン単位閾値を超えるとメモリページを閉塞し、キャッシュライン単位発生回数がキャッシュライン単位閾値を超える前に切替後の発生回数総和が総和閾値を超えた以降は障害発生毎にメモリページを閉塞するページ閉塞部34とを有する。

(もっと読む)

ソリッド・ステート・ドライブ装置および平準化管理情報の退避・回復方法

【課題】大容量の平準化管理情報を短時間のうちに不揮発性メモリに退避させることを可能にする。

【解決手段】平準化管理情報記憶部13は、レーン接続バス30を介して8つのレーン21それぞれに含まれるバッファ記憶制御部22のBM220に接続され、各レーン21には、バッファ記憶制御部22とNVMチップ23とを接続するチップ接続バス24が設けられている。各レーン21のバッファ記憶制御部22は、平準化管理情報退避・回復処理部14の指示のもとに、平準化管理情報記憶部13から転送される退避データを、チップ接続バス24を介して、互いに独立に並行してNVMチップ23へ転送する。その退避データの中には、平準化管理情報だけでなく、その平準化管理が平準化管理情報記憶部13に記憶されていたときの先頭アドレスが含まれている。

(もっと読む)

欠陥フラッシュメモリダイの動作不能化

【課題】複数のフラッシュメモリダイを含むデバイス内の欠陥フラッシュメモリダイを動作不能化する製品ならびに関連する方法およびシステムを提供する。

【解決手段】動作不能化されていないフラッシュメモリダイに基づくフラッシュメモリのデータ記憶容量を示すラベルを、複数のフラッシュメモリダイを含むパッケージに付すことができる。ダイレベル、パッケージレベル、および/またはボードレベルにおいて、様々な動作不能化方法を適用することができる。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】コントローラ側に特別な制御を要求することなく、正常な一部のコアチップだけに有効なチップ識別番号を割り当てて正常なコアチップのみを動作させる。

【解決手段】半導体装置10は、複数のコアチップCC0〜CC7及びインターフェースチップIFを備え、各コアチップCC0〜CC7は、第1のチップアドレスの値をインクリメントした第2のチップアドレスを生成する層アドレス発生回路46と、インターフェースチップIFから供給される第3のチップアドレスと第2のチップアドレスとを比較し、両者が一致した場合にチップ選択信号を活性化させる層アドレス比較回路47を備えている層アドレス発生回路は46、不使用チップ信号DEFが非活性状態である場合には、第2のチップアドレスを他のコアチップに供給し、不使用チップ信号DEFが活性状態である場合には、第1のチップアドレスをそのまま他のコアチップに供給する。

(もっと読む)

制御装置

【課題】半導体記憶装置において、処理性能の向上が可能な制御技術を提供する。

【解決手段】命令解釈部60は、コマンドを解釈し、セクタアドレスを抽出する。アドレス変換テーブル記憶部70は、セクタアドレスの集合とページアドレスと管理情報とを対応付けて記憶する。特殊セクタ記憶部80は、特殊セクタアドレスを記憶する。アドレス変換テーブル管理部61は、コマンドがデータのアクセスを要求する場合、セクタアドレスを用いてアドレス変換テーブル記憶部70の管理情報を参照して、ページ内に特殊セクタがあるか否かを判定する。判定結果が否定的であれば、アクセス制御部64は、フラッシュメモリ素子にアクセスし、判定結果が肯定的であれば、特殊セクタ管理部62は、セクタアドレスが特殊セクタアドレスとして特殊セクタ記憶部80に記憶されているか否かを判定し、判定結果に応じて、特殊応答データ作成部63は、応答データを作成する。

(もっと読む)

メモリ診断方法及びメモリ回路

【課題】メモリ回路において、運用中に自動でメモリ全体の故障検出を行うことを目的とする。

【解決手段】ネットワークから受信したフレームのフレーム間ギャップを含む空きタイムスロットで、メモリのテストを行うためのテストアドレスを順次変化させて生成するテストアドレス生成手段と、メモリのテストアドレスから読み出したデータを退避する退避手段と、メモリのテストアドレスにテストデータを書き込むテスト書き込み手段と、メモリのテストアドレスからテストデータを読み出すテスト読み出し手段と、テスト読み出し手段で読み出されたテストデータを予め保持している基準データと比較して障害の有無を判定する判定手段と、退避手段に退避されているデータを前記メモリの前記テストアドレスに書き戻す書き戻し手段とを有する。

(もっと読む)

不揮発性記憶システム

【課題】不揮発性メモリシステムにおける経時的に発生する書込み不良に対する救済効率を向上させる。

【解決手段】複数の不揮発性記憶装置(FLS1〜FLS16)と制御装置(CTR)とを有する。制御装置は、動作対象の不揮発性記憶装置に対する書込みエラーを検出したとき、書込みエラーに係る記憶領域を複数の不揮発性記憶装置の内の他の不揮発性記憶装置の記憶領域に代替させたことを示すチップ間代替情報を当該エラーに係る記憶領域の不揮発性記憶装置に設定することが可能であり、動作対象の不揮発性記憶装置からチップ間代替情報を得たとき当該チップ間代替情報が示す他の不揮発性記憶装置を動作対象に変更可能なものである。更に、チップ間代替は、複数の不揮発性記憶装置全てに対して可能である。

(もっと読む)

ストレージデバイス内のエラーデータを追跡するシステムおよび方法

エラーデータを追跡するシステムおよび方法を開示する。この方法が、第1のエラー訂正コード演算のエラー場所に関連づけられた第1のチェックサムを受信するステップと、第2のエラー訂正コード演算のエラー場所に関連づけられた第2のチェックサムを受信するステップとを含む。第1のチェックサムは、第2のチェックサムと比較され、その比較結果に基づいてメモリアレイの領域に動作が開始される。  (もっと読む)

(もっと読む)

メモリ制御装置、メモリモジュール及びメモリ制御方法

【課題】出荷後において記憶装置に不良領域が生じた場合でも継続して使用することができるメモリ制御装置、メモリモジュール及びメモリ制御方法の提供。

【解決手段】記憶領域を有する記憶装置へのアクセスを制御するメモリ制御装置であって、前記記憶領域に含まれる、データの格納が不可能な不良領域を検出し、検出された不良領域のアドレス情報を含んだ不良情報を所定の記憶領域に記憶し、前記不良領域への書込みが実行されたデータを、所定の記憶領域に記憶された不良情報に基づき、不良領域以外の記憶領域に書込む。

(もっと読む)

1 - 20 / 87

[ Back to top ]