Fターム[5B018KA12]の内容

記憶装置の信頼性向上技術 (13,264) | エラー処理 (1,086) | 障害回復 (704) | 再試行(リトライ) (52)

Fターム[5B018KA12]に分類される特許

1 - 20 / 52

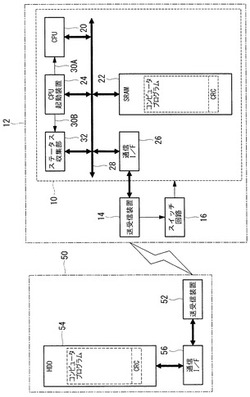

遠隔装置に搭載される情報処理装置及び情報処理装置の起動方法

【課題】コンピュータプログラムを予め記憶したROMを必要とせず、かつコンピュータプログラムの破損を容易に解消させる、ことを目的とする。

【解決手段】情報処理装置10は、遠隔操作によって動作する遠隔装置に搭載され、コンピュータプログラムを実行するCPU20、及び該コンピュータプログラムを記憶する書き込み可能なRAMを備え、地上局50が備える送受信装置52から送信されるコンピュータプログラムを受信し、受信したコンピュータプログラムをRAMへ転送し、RAMにコンピュータプログラムが記憶されている状態でCPU20を起動させる。

(もっと読む)

診断装置、診断方法および診断プログラム診断方法

【課題】コンピュータシステムのメモリ部の障害の被疑部位を高速かつ正確に特定する診断装置を提供する。

【解決手段】コンピュータシステム100のメモリ部3にアクセスしてエラーが発生した際に、診断装置10は、エラー発生時のメモリ読み出しアドレスおよびメモリ読み出しデータのエラービットをそれぞれ読み出しアドレス保持回路15およびエラービット保持回路12に保持し、診断読み出しアドレス生成回路16および診断読み出しコマンド生成回路14からメモリ読み出し制御部2に指示してエラー発生時の同一メモリ読み出しアドレスに再度アクセスするリトライ動作を実施させ、リトライ結果として、エラービット比較回路13において再度同一のエラービットが発生するか否かの比較結果131に基づいて、診断制御回路17は、固定障害か否かを判別し、固定障害と判別した場合エラーが発生した部位を中心に切り分けテストを行い、障害被疑部位を特定する。

(もっと読む)

メモリシステム

【課題】読み出し動作開始から読み出し動作完了までの処理時間を可及的に低減する。

【解決手段】制御部は、不揮発性メモリに格納されているデータを読み出す際、読み出し電圧管理情報に記録されている読み出し電圧の値を用いて不揮発性メモリからデータを読み出して、誤り検出部が読み出されたデータに誤りを検出したとき、誤り検出部が読み出されたデータに誤りを検出しなくなるまで読み出し電圧を変更して前記不揮発性メモリからデータの再読み出しを行い、誤り検出部が読み出されたデータに誤りを検出しなくなったとき、読み出し電圧管理情報に記録されている読み出し電圧を更新する。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】半導体記憶装置に対する書き込み/読み出しに影響を与えることなく、読み出し時にエラー訂正されたデータを、メモリ本体に再書き込みする。

【解決手段】実施形態に係る半導体記憶装置1は、エラー訂正部9、第1の記憶部10、第2の記憶部11、制御部13を含む。エラー訂正部9は、メモリ本体8から読み出されたデータに対するエラー訂正を行う。第1の記憶部10は、エラー訂正部9によって訂正されたデータを記憶する。第2の記憶部は、エラー訂正部9によって訂正されたデータに対応するアドレスを記憶する。制御部13は、メモリ本体8に対する読み出し/書き込みが実行されていないタイミングにおいて、第1の記憶部10に記憶されているデータと第2の記憶部11に記憶されているアドレスに基づいて、メモリ本体8に対して再書き込みを行う。

(もっと読む)

メモリ装置、情報処理システム、メモリ制御方法、およびプログラム

【課題】特別な温度範囲が広い高価な不揮発性メモリを使わずに、温度保証範囲が狭い安価な汎用品不揮発性メモリを用いて広範囲な温度保証を実現することが可能なメモリ装置、情報処理システム、メモリ制御方法、およびプログラムを提供する。

【解決手段】メモリ装置は、不揮発性メモリと、不揮発性メモリに対してアクセスを行うメモリコントローラと、メモリ装置の温度を検出する温度検出部と、を有し、メモリコントローラは、不揮発性メモリに対するアクセス開始時に不揮発性メモリに識別情報の転送を要求し、要求に対する応答がない場合であって、温度検出部の検出温度が第1の閾値より低い場合、不揮発性メモリの温度を上げるように温度上昇制御を行い、温度上昇制御により温度検出部の検出温度があらかじめ設定された仕様範囲内にある場合には、不揮発性メモリに対して識別情報の転送を再要求する。

(もっと読む)

データ記憶装置及び誤り検出訂正方法

【課題】エラー訂正不能と判定された場合に、ECC処理の再実行を効率的に行なうことを実現し、リード処理効率を向上できるデータ記憶装置を提供することにある。

【解決手段】実施形態によれば、データ記憶装置は、リードモジュールと、誤り検出訂正モジュールと、コントローラとを具備する。リードモジュールは、不揮発性メモリからアクセス対象のデータ及び当該データを特定する指定データを読み出す。誤り検出訂正モジュールは、前記リードモジュールにより読み出されたデータ及び前記指定データに対する誤り検出訂正処理を実行する。コントローラは、前記誤り検出訂正モジュールによる誤り訂正が不能である場合に、前記指定データの修正処理を実行し、修正処理後の指定データに基づいた再度の誤り検出処理を実行する。

(もっと読む)

フラッシュメモリに対してデータの読み出しおよび書き込みを行う制御装置

【課題】記録先のブロック中に順次データを記録していき、当該記録先のブロックがデータで満杯になると、次のブロックのデータを消去して新たな記録先のブロックとし、前回の記録先のブロックのデータのうち、一部の必要なデータを現在の記録先のブロックにコピーし、その後、現在の記録先のブロックに順次データを記録していくというフラッシュメモリの書き込み制御において、ブロックの故障に起因してブロック間のデータのコピー頻度が増大するのを防ぐ。

【解決手段】現在の記録先のブロックが満杯状態になって次のブロックの消去を試みたときに(ステップ150)、消去が失敗したか否かを判定し(ステップ160)、消去に失敗したと判定したことに基づいて、次のブロックが故障したと判定し、使用対象から除外する(ステップ175)。

(もっと読む)

複数のアクセスコマンドを並行して実行するメモリ装置及び同装置におけるメモリアクセス方法

【課題】ブロック単位のメモリアクセス処理を、小容量のメモリ領域を用いた管理で高速に実行できるようにする。

【解決手段】実施形態によれば、メモリ装置のメモリインタフェースは、複数のアクセスコマンドに従ってメモリに並行してアクセスする。コマンド生成手段は所定のアクセス処理において、メモリインタフェースに複数のアクセスコマンドを投機的に投入する。アクセスコマンド返却手段は、メモリインタフェースに既に投入済みの、エラー発生時点で未実行のアクセスコマンド群を、対応するパージレスポンスにより返却する。コマンド進捗管理手段は、返却された未実行のアクセスコマンド群のうちの最も古いアクセスコマンドを指すようにコマンド進捗管理情報を更新する。コマンド生成手段は、更新された情報に基づき、返却された未実行のアクセスコマンド群をメモリインタフェースに再投入する。

(もっと読む)

メモリコントローラ及び情報処理システム

【課題】メモリモジュールの故障に対して早急な処置を行うことを可能とし、情報処理システムの信頼性を向上させることを可能にするメモリコントローラ及び情報処理システムを提供する。

【解決手段】メモリコントローラ及び情報処理システムにおいて、メモリモジュールから読出されたデータのエラー検出を行うエラー検出部と、メモリコントローラを通常モードから故障検査モードに切り替え、複数の単位メモリ領域におけるそれぞれの検査対象のデータ記録済アドレスからデータを読出し、該読出しデータのエラーを前記エラー検出部により検出させて、故障検査を実行させる故障検査制御部と、故障検査制御部による検査結果における各単位メモリ領域のエラー検出状況に基づいて、メモリモジュール内部の故障に起因するメモリ故障と、メモリモジュール外部のデータ伝送路の故障に起因する伝送路故障を判定する判定部を備える。

(もっと読む)

フラッシュメモリ内のエラーから復旧するための方法

【課題】一つ以上のフラッシュメモリ・セルからデータを読み取るための、そして読み取りエラーから復旧するための、方法、デバイスおよびコンピュータで読み込み可能なコードを提供する。

【解決手段】エラー検出訂正モジュールによるエラー訂正が失敗した場合、エラー訂正が成功するまで、少なくとも一度、一つ以上の修正基準電圧を用いて、フラッシュメモリ・セルの再読み出しを行う。エラー訂正が成功した後、当座の間フラッシュメモリ・セルにデータ(例えば、読み出したデータの信頼可能な値)を再書き込みすることなく、以降の読み出しリクエストを処理する。エラーを訂正した読み取りに関する基準電圧をメモリに記憶して、以降の読み出しリクエストに応答するときに読み出してもよい。修正基準電圧は、予め定めた基準電圧である。又は、必要に応じランダムに算出した値を用いて、あるいはエラー検出訂正モジュールが提供する情報に応じて決定してもよい。

(もっと読む)

フラッシュメモリ用のLDPC消失復号化

電子機器

【課題】実装面積、消費電力、および処理時間の増大を抑えつつ、MNUをはじめとするソフトエラーによって発生する不具合を防止することができる電子機器10を提供する。

【解決手段】本発明の電子機器10は、所定数の命令毎に設けられたチェックポイントを実行する都度、演算装置14内の順序回路に含まれるフリップフロップの状態を示すデータを取って置き、ソフトエラーの予兆を検出した場合に、直前のチェックポイントにおける命令の実行後に取って置いたデータに基づいて演算装置14内の順序回路に含まれるフリップフロップの状態を設定し、直前のチェックポイントに対応する命令の次の命令から実行を再開する。

(もっと読む)

半導体メモリシステム

【課題】メモリ装置及びメモリ装置の制御方法を提供する。

【解決手段】メモリコントローラで命令を生成する段階;クロック信号に応答して命令の個数をカウントする段階;命令及び命令に対応するカウント数を保存する段階;メモリコントローラから、命令、命令のカウント数及びデータをメモリ装置に伝送する段階;メモリコントローラから伝送された命令、命令のカウント数及びデータを前記メモリ装置で受信する段階;受信された命令のカウント数を保存する段階;受信された命令のカウント数をメモリコントローラに伝送する段階;を含み、メモリコントローラに命令のカウント数を伝送する段階は、エラー状態の指示で行われ、メモリ装置から受信される命令のカウント数による命令及びデータを、メモリコントローラからメモリ装置に再伝送する段階をさらに含むメモリ装置の制御方法。

(もっと読む)

演算処理装置及び演算処理装置の制御方法

【課題】ロード動作を高速化する。

【解決手段】データを記憶する第1の記憶部と、第1の記憶部から読み出したデータについてエラーの発生を検出するエラー検出部と、第1の記憶部から読み出したデータを、ロード要求に基づいて格納する第2の記憶部と、エラー検出部が、ロード要求により第1の記憶部から読み出したデータについて、エラーの発生を検出した場合、第1の記憶部へのロード要求の再送要求を、データのエラーが検出されたサイクルと同じサイクルにおいて生成する再送要求生成部と、エラーが検出されたデータと再送要求が与えられたとき、第1の記憶部にロード要求を再送する命令実行部と、を有する演算処理装置を提供する。

(もっと読む)

メモリシステム

【課題】プログラムディスターブ、リードディスターブの影響やデータリテンションの劣化の影響を除去して信頼性を向上することが可能なメモリシステムを提供する。

【解決手段】複数のメモリセルを含む複数のブロックを有するメモリセルアレイと、前記メモリセルの読み出しレベルを変更可能な電圧生成部と、を有する不揮発性半導体記憶装置と、前記不揮発性半導体記憶装置の書き込み、読み出し、消去を制御する制御部とを具備し、前記制御部は、前記不揮発性半導体記憶装置の使用開始時と時間経過後とで読み出しレベルを変える。

(もっと読む)

エラーを管理するための加速書き込み後読み出しを伴う不揮発性メモリおよび方法

不揮発性メモリにおけるデータエラーは、使用されると、またセル当たりに格納されるビットの密度が高くなると、必然的に増える。メモリは、より少数のエラーで動作するけれども記憶密度がより低い第1の部分と、より高い密度で動作するけれども記憶装置の堅固性がより低い第2の部分とを有するように構成される。1つのエラー管理は、第2の部分へのコピー後のコピーの読み出しおよび検査を提供する。コピーが過多なエラービットを有するならば、第2の部分または第1の部分の中の別の位置において反復される。コピーの読み出しおよび検査は、そのサンプルだけを読み出すことによって加速される。サンプルは、それ自体のECCを有する、それがサンプリングしているコピーの中の最悪エラー率を表すと推定されるコピーのサブセットから選択される。一実施形態では、サンプルは、1つのグループの各マルチビットメモリセルの1つのビットから取られる。  (もっと読む)

(もっと読む)

バッテリーパック、及びデータフラッシュの動作の制御方法

【課題】データフラッシュの動作の制御方法とその機能を持つバッテリーパックを提供する。

【解決手段】本発明の一実施形態によるデータフラッシュの動作の制御方法は、2個のデータフラッシュの記録、コピー及び削除を、該当データフラッシュの特定領域に保存されている状態フラッグによって行うことによって、一つのデータフラッシュが満たされる場合、他のデータフラッシュに一部のデータをコピーするか、またはデータフラッシュを削除する途中で、リセットが発生する場合に発生するデータフラッシュ故障を防止できる。

(もっと読む)

データ送信方法、システム及びサーバ

【課題】リカバリ処理等のためのデータ送信が中断された場合に、データ送信にかかる時間を従来よりも短縮する。

【解決手段】サーバは、複数のデータブロックの各々に固有な第1固有情報を生成して記憶した後に、各データブロックを順次、情報処理装置へ送信する。情報処理装置は、サーバから送信された各データブロックを順次受信する。情報処理装置は、サーバがデータブロックの送信を中断した場合には、サーバからデータブロックの送信再開指示を受けた後に、サーバから第1固有情報を取得し、受信済みのデータブロックの各々に固有な第2固有情報を生成し、データブロックを受信した順に、第1固有情報と第2固有情報とを比較し、第1固有情報と第2固有情報とが一致しないデータブロックの送信をサーバに要求する。

(もっと読む)

記憶装置、基板、液体容器、不揮発性のデータ記憶部の制御方法、ホスト回路と着脱可能な記憶装置を含むシステム

【課題】ホスト回路と電気的に接続される記憶装置の不良を低減する。

【解決手段】ホスト回路と電気的に接続される記憶装置はホスト回路から第1の実データを受信する。記憶装置は第1の実データと関連付けられた第1のパリティデータを取得する。記憶装置は複製である第2の実データと第2のパリティデータとを生成する。半導体記憶装置は第1の実データと第1のパリティデータとを第1の記憶領域に書き込むと共に、第2の実データと第2のパリティデータとを第2の記憶領域に書き込む。半導体記憶装置は第1の実データと第1のパリティデータと第2の実データと第2のパリティデータをデータ記憶部から読み出してホスト回路に対して送信する。

(もっと読む)

情報処理装置

【課題】不揮発性メモリのアクセス速度や装置への過負荷等といった性能面への影響を低減可能とする。

【解決手段】ブート実行手段320は、各種制御プログラム101i〜103iをロードエリア210にロードし、かつ照合用エリア220に対して制御プログラム101iのイメージ1010iをコピーする。照合復旧・前処理プログラム102iは、制御プログラム101iのイメージと照合用エリア220上の同イメージ1010iを照合する。一致する場合に制御プログラム101iを実行させる。相違がある場合に不揮発性メモリ100上の制御プログラム101iのイメージをロードエリア210に再ロードし、照合用エリア220上にコピーし、制御プログラム101iを実行させる。その後、照合復旧・後処理プログラム103iは、再度照合処理を実行し、一致する場合に照合復旧・前処理プログラム102i+1を実行させる。

(もっと読む)

1 - 20 / 52

[ Back to top ]