Fターム[5B018KA17]の内容

記憶装置の信頼性向上技術 (13,264) | エラー処理 (1,086) | 障害回復 (704) | アドレス単位の切替え (30)

Fターム[5B018KA17]に分類される特許

1 - 20 / 30

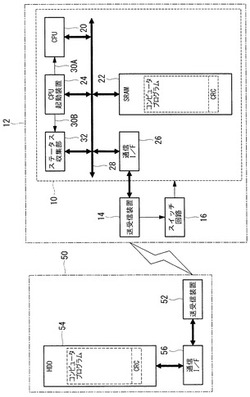

遠隔装置に搭載される情報処理装置及び情報処理装置の起動方法

【課題】コンピュータプログラムを予め記憶したROMを必要とせず、かつコンピュータプログラムの破損を容易に解消させる、ことを目的とする。

【解決手段】情報処理装置10は、遠隔操作によって動作する遠隔装置に搭載され、コンピュータプログラムを実行するCPU20、及び該コンピュータプログラムを記憶する書き込み可能なRAMを備え、地上局50が備える送受信装置52から送信されるコンピュータプログラムを受信し、受信したコンピュータプログラムをRAMへ転送し、RAMにコンピュータプログラムが記憶されている状態でCPU20を起動させる。

(もっと読む)

制御装置、記憶装置、制御方法

【課題】不揮発性メモリのデータ信頼性向上と読出アクセス時間の高速化及び安定化

【解決手段】不揮発性メモリに記憶されたデータについて、近い将来リフレッシュが必要となるか否か、つまりリフレッシュ機会が近接しているか否かを推測する。この推測にはアクセス時のビットエラー数などを記憶した評価用情報を用いる。そしてリフレッシュ機会が近接していると判定されるデータについて、そのデータをオリジナルデータとして、オリジナルデータと同一のクローンデータを、不揮発性メモリ内に生成する。その場合、アクセス実行の際にオリジナルデータとクローンデータのいずれか一方がアクセス対象となるように、管理情報を更新する。

(もっと読む)

メモリ記憶装置

【課題】ホスト装置が不揮発性メモリから記憶情報を読出さずに不揮発性メモリのデータ保持に対する信頼性を向上させる。

【解決手段】本発明に係るメモリ記憶装置は不揮発性メモリ(2)とメモリコントローラを有する。メモリコントローラは、ホストインタフェース回路(10)、メモリインタフェース回路(12)及び制御回路(11,13,14)を有する。制御回路は第1〜3処理を制御可能である。第1処理は書込みデータにエラー訂正コードを付加したデータをメモリインタフェース回路から書込み制御情報と共に出力する。第2処理は読出し制御情報に従いエラー検出・訂正したデータをホストインタフェース回路から出力する。第3処理は読出し制御情報に従いエラー検出・訂正したデータを書込み制御情報と共に出力する。メモリコントローラは、第3処理において、エラー発生回数が所定回数を超えたときエラー訂正された読出しデータの記憶領域を変更する。

(もっと読む)

半導体記憶装置

【課題】大容量の不揮発性メモリのアクセス時間とランダム・アクセス・メモリのアクセス時間との整合を図り、大容量不揮発のメモリを含む半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、フラッシュメモリと、クロック同期型DRAMと、前記フラッシュメモリ及び前記クロック同期型DRAMに結合され、前記クロック同期型DRAM及び前記フラッシュメモリに対するアクセスを制御するための制御回路と、前記制御回路に結合された複数の入出力端子とを含む。前記入出力端子を介した前記フラッシュメモリに対するアクセスは、前記クロック同期型DRAMを経由して行う。

(もっと読む)

メモリシステムおよびコンピュータシステム

【課題】本発明は、“リードディスターブ”現象が発生したとしても、データ読み出し処理に影響を及ぼすことの無いメモリシステムを提供する。

【解決手段】本発明に係るメモリシステムは、演算装置50に加えて、ユーザ情報を含む情報を記憶するために設けられ、互いに重複しない第1物理アドレスが個々に割り当てられる複数の第1ブロックと、複数の第1ブロックのうちの初期欠陥ブロックの第1物理アドレスを個々に記憶するために設けられる複数の第2ブロックとを備える。演算装置50は、入力された所定の論理アドレスに対応する所定のミラー論理アドレスと、第2ブロックに格納される情報とに基づいて、所定の論理アドレスに対応する第1物理アドレスを求める。

(もっと読む)

記憶装置及びデータ格納領域管理方法

【課題】記憶装置の長寿命化を図り、ビットコストを低減させる。

【解決手段】コントローラ及び複数の記憶素子によって構成される半導体記憶媒体を備える記憶装置であって、複数の記憶素子には、第1の記憶素子と、第1の記憶素子よりもデータの消去回数の上限値が小さい第2の記憶素子とが含まれ、データの格納先として指定される第1のアドレスと、データが格納される領域の第2のアドレスとの対応を含む領域変換情報が含まれ、格納されたデータの書き換え頻度が領域ごとに記録され、第1のアドレスに対応する領域を選択し、選択された領域の書き換え頻度が所定の第1の閾値以上であるか否かを判定し、書き換え頻度が所定の閾値以上の場合には第1の記憶素子によって提供される領域を選択し、書き換え頻度が所定の閾値よりも小さい場合には第2の記憶素子によって提供される領域を選択し、第1のアドレスに選択された領域のアドレスを対応させる。

(もっと読む)

メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】仮想ブロックを形成して複数個のフラッシュメモリに並行したデータの書き込みや読み出しを行うように構成されたフラッシュメモリシステムにおいて、仮想ブロックの管理及び仮想ブロックに対するアクセスを効率良く行うことができるように仮想ブロックを形成する。

【解決手段】メモリコントローラは、互いに異なるフラッシュメモリに属する同じアドレスの物理ブロックを複数個結合させた暫定仮想ブロックを複数個形成し、複数個の暫定仮想ブロックから不良の物理ブロックが含まれる暫定仮想ブロックを抽出し、抽出された複数個の暫定仮想ブロック間で不良の物理ブロックと良品の物理ブロックとを交換することにより、不良の物理ブロックが含まれていない第2の暫定仮想ブロックを形成し、抽出されなかった暫定仮想ブロック及び上記第2の暫定仮想ブロックを管理対象とする。

(もっと読む)

ECCに基づいてフラッシュメモリのデータページを更新する記憶装置及びその方法

【課題】フラッシュメモリのデータページを更新する記憶装置及びその方法を提供する。

【解決手段】記憶装置は、フラッシュメモリと、誤り訂正符号(ECC)検出器と、コントローラとを含む。フラッシュメモリのデータページ毎は、データ及び前記データに対応するECCを記憶する。ECC検出器は、毎のデータページのスペア領域のECCに用いるビット数を検出する。コントローラは、前記複数のデータページ中の第1データページのECCに用いるビット数が予定値より高い時、前記第1データページに記憶したデータ及び前記ECCを、ECCに用いるビット数が前記予定値より低い第2データページに記憶する。

(もっと読む)

ディスク装置及びその制御方法

【課題】書き換え回数に制限のある不揮発メモリを含むディスク装置において、不揮発メモリの交替領域を使い果たした後も不揮発メモリを効率的に使用する。

【解決手段】本発明は、書き換え回数に制限のある不揮発メモリ、ディスク、及び不揮発メモリの論理アドレス(LBA:Logical Block Address)と物理アドレスとの対応関係を管理するメモリ管理テーブルを含む制御部を有する。制御部は、不揮発メモリにデータを書き込むべきLBAに対応する物理アドレスの領域の不良発生に応答して、データを書き込むべきLBAとは異なる不揮発メモリのLBAに対応する物理アドレスにデータを書き込み、メモリ管理テーブルにおいて、データを書き込んだ物理アドレスをデータを書き込むべきLBAに対応付ける。

(もっと読む)

メモリ制御装置

【課題】メモリセルの状態が異常状態になっても、メモリ装置を正常に作動させることが可能なメモリ制御装置を提供すること。

【解決手段】このメモリ制御装置は、第1のアドレス制御部及び第2のアドレス制御部を有する。メモリ制御装置は、第1のアドレス制御部を用いることにより、アドレス情報に基づいてメモリセルを特定する。メモリ制御装置は、アドレス情報及び書込用情報を含む書込指示情報に応じて、上記特定されたメモリセルに書込用情報を保持させる。メモリ制御装置は、メモリセルが保持している情報に基づいて当該メモリセルの状態が異常状態であるか否かを検出する。メモリ制御装置は、メモリセルの状態が異常状態であると検出された場合に、メモリセルを特定するために用いるアドレス制御部を第1のアドレス制御部から第2のアドレス制御部へ変更する。

(もっと読む)

メモリシステム

【課題】エラー検出訂正システムを搭載したメモリデバイスを、テストフリー化することを可能としたメモリシステムを提供する。

【解決手段】メモリシステムは、メモリ装置と、前記メモリ装置に搭載されて、エラー訂正が不可能な場合にエラー訂正不可能信号を発生するエラー検出訂正システムと、前記エラー検出訂正システムが発生するエラー訂正不可能信号に基づいて、エラー訂正不可能な不良領域アドレスに代わって、前記メモリ装置のアドレス進行とアドレス発生初期にぶつからないように進行する内部アドレスを発生するアドレス発生回路と、前記メモリ装置のアクセス時に参照され、前記エラー検出訂正システムが発生するエラー不可能信号に基づいて、前記不良領域アドレスに代わって発生すべき代替領域アドレスとして前記アドレス発生回路が発生する内部アドレスを記憶する内容参照メモリと、を有する。

(もっと読む)

半導体記憶装置、半導体記憶装置の制御方法および制御プログラム

【課題】ハードディスクドライブなどの大容量記憶装置の代替使用に際し、フラッシュメモリの課題を解決しつつ、記憶装置の意味づけを装置寿命かアクセス速度かの最適な状態に設定する。

【解決手段】各種データを記憶する第1半導体メモリ領域31および当該第1半導体メモリ領域31内の不良ブロックを代替する第1不良ブロック代替領域32を有するフラッシュメモリ27と、FeRAMで構成され、フラッシュメモリ27のデータの一部をキャッシュとして保持する第2半導体メモリ領域33を有するキャッシュメモリ28と、第2半導体メモリ領域33の一部を、第1半導体メモリ領域31内の不良ブロックを代替する第2不良ブロック代替領域34として管理する。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリに不良セルが生じた場合でも、半導体メモリを交換することなく半導体メモリを用いた装置は正常な動作を続けることができる半導体メモリ装置を提供すること。

【解決手段】メモリ制御回路を介して半導体メモリにアクセスするように構成された半導体メモリ装置において、半導体メモリの不良セルを検出する不良セル検出部と、メモリ制御回路に設けられ、不良セル検出部の検出結果に基づき半導体メモリの不良セルを救済するための救済セルを割り当てる不良セル救済処理部、を備えたもの。

(もっと読む)

メモリアクセス制御方法及び回路、並びに情報処理装置

【課題】本発明は、メモリアクセス制御方法及び回路、並びに情報処理装置に関し、メモリの寿命が近い状態を事前に検知可能とすることを目的とする。

【解決手段】メモリ内のデータのエラーを訂正して得られた訂正データとそのアドレスを保持するエラー訂正レジスタ群の空き容量を示す情報を検出し、この情報に基づいて警告を出力する出力ように構成する。

(もっと読む)

メモリ及びデータの書き込み、読み出し方法

【課題】

解決しようとする課題は、ソフトウエアプログラムと連携して動作するメモリにおいて、記録保持するデータが破壊された場合、プログラムからのデータ参照要求に対し、正常なデータを効率良く読み出すことができない問題である。

【解決手段】

メモリのアドレス単位の単位データ毎にパリティを付加して主データ、副データの組み合わせで繰り返して記録し、ソフトウエアプログラムからの問い合わせに対し、前記単位データ毎に主データのパリティと副データのパリティを評価して読み出す。

(もっと読む)

ダイナミックに修復可能なメモリに関する方法及びシステム

【課題】 ダイナミックに修復可能なメモリに関する方法及びシステムを提供する。

【解決手段】 動作中に生じる不良の検出及び修復が可能なメモリ・システムに関するシステム及び方法が開示される。本発明の複数の実施形態は、メモリのメモリ・セルでのエラーを検出するように動作し、そして不良メモリ・セルを置き換えるように動作するメモリ・システムを提供する。より詳しくは、ある実施形態では、メモリのあるアドレスでの不良は、そのメモリの動作中に検出されることができる。このメモリ・セルは、次に冗長メモリ・セルにより置き換えられることができる。不良メモリ・セルを置き換えることによって、そのメモリ・システムは、その不良メモリ・セルに起因する後続のエラーに出会うことなく利用され続けることができる。

(もっと読む)

電子制御装置

【課題】高速読み書きが容易に行なえる不揮発性メモリMRAMを用いた電子制御装置の安全性を向上する。

【解決手段】外部ツール108から制御プログラムが書込まれるMRAM120Aは、訂正符号付き書込回路122と復号化読出回路123と、エラー発生アドレス番号がエラーデータとして書込まれるエラーレジスタ125a・125bとを備え、エラー発生アドレスを指定して確認読出しを行なったときに依然としてエラーが発生していると重複異常判定を行なって異常報知される。MRAM120Aのプログラムメモリ領域は通常は書込禁止状態にあり、外部ツール108が接続されると禁止状態が解除される。エラーレジスタ125a・125bは書込禁止対象とならないデータメモリ領域に設けられている。

(もっと読む)

タイマ制御装置およびその障害検出方法

【課題】運用中においてもソフトウェアの負荷に影響を与えずタイマの正常性を確保する。

【解決手段】タイマ制御装置10は、CPU11から指定されたタイマカウント値をメモリ13に格納し、該タイマカウント値を一定周期で減少または増加させ、該タイマカウント値が所定値になった場合にタイムアウトをCPU11へ通知する。タイマ制御装置10は、タイマカウント値のメモリ13への格納時に、メモリ13におけるタイマカウント値の格納領域の正常性をチェックするデータチェック部20を備える。データチェック部20は、格納領域に全て1を書き込んで読み出して全て1であるかチェックし、格納領域に全て0を書き込んで読み出して全て0であるかチェックして、格納領域の正常性をチェックする。

(もっと読む)

記憶媒体制御装置

【課題】NAND型フラッシュメモリなどのブロック単位で管理される不揮発性記憶媒体を用いるときに、利用効率を低下させることなく、適正なデータ読み出しを可能とする。

【解決手段】NAND型フラッシュメモリが接続されるメモリコントローラ20には、論理アドレスを、フラッシュメモリの物理ブロックアドレスに変換するアドレス変換部24を設けている。このアドレス変換部では、不良ブロックに対する代替ブロックを設定する代替ブロックテーブルを用いて、論理アドレス又は論理ブロックアドレスに対して、適正な物理ブロックアドレスに変換する。これにより、不良ブロックの発生を考慮して、同一のデータを複数のブロックに格納することなく、要求されるデータを適正に読み出すことができる。

(もっと読む)

半導体記憶装置

【課題】アンチヒューズによる救済方式の問題点を解決すること。

【解決手段】DRAM10、SPD(EEPROM)20が搭載されるとともに、SPD20にDRAM10の不良アドレス情報が格納されたメモリモジュール30と、不良アドレス情報をSPD20から読み出してDRAM10に不良アドレス情報を転送するメモリコントローラ40と、を備える。DRAM10は、メモリセルアレイ50と、不良アドレス情報を格納するための救済アドレスレジスタ12、14と、メモリセルアレイ50の欠陥があるメモリセルに対して代替される冗長メモリセル11と、を有する。DRAM10は、転送された不良アドレス情報を救済アドレスレジスタ12、14に格納した後、通常のアクセス動作時に、外部から入力された外部アドレス情報が、救済アドレスレジスタ12、14の不良アドレス情報と一致したときに冗長メモリセル11にアクセスする。

(もっと読む)

1 - 20 / 30

[ Back to top ]