Fターム[5B018KA22]の内容

記憶装置の信頼性向上技術 (13,264) | エラー処理 (1,086) | 障害回復 (704) | 正常データの再ロード(転送) (181)

Fターム[5B018KA22]に分類される特許

1 - 20 / 181

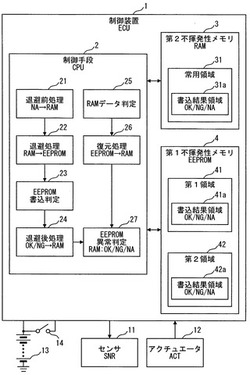

メモリ管理装置

【課題】RAMのデータを保存するEEPROMの異常を検出する。

【解決手段】制御装置1は、EEPROM4を管理するメモリ管理装置を提供する。電源オフに応答して、RAM3のデータがEEPROM4に複写される。RAM3の書込結果領域31aには、EEPROM4への書込処理が正常終了したか否かが書込まれる。電源オンの後に、RAM3のデータに異常があると、EEPROM4に退避してあるデータに基づいてRAM3のデータが復元される。EEPROM4への書込処理の異常終了が所定回数継続すると、EEPROM4の故障を判定する。さらに、制御装置1は、EEPROM4への書込処理の前に、書込結果領域31aを初期化する。これにより、EEPROM4への書込処理の途中で電源が遮断され、制御装置1が再起動された場合でも、そのことを書込結果領域31aに基づいて判定できる。

(もっと読む)

故障位置判定回路、記憶装置、および情報処理装置

【課題】記憶装置で発生したエラーに対して、簡易かつ的確にエラーを解析し、エラーの状況を取得できるようにする。

【解決手段】故障解析回路は、故障がある記憶領域に記憶された故障データと交替レジスタのデータとを比較する比較回路と、比較回路による比較結果データからエラービット位置を特定する位置特定回路と、を備える。

(もっと読む)

メモリ制御装置及びメモリ制御プログラム

【課題】省エネ復帰時間を短縮しながらハングアップすることなく確実に復帰させることを目的とする。

【解決手段】省エネモード中の電源を監視して(100)、閾値以上の電圧が検出された場合には、省エネ復帰から通常復帰に切り換えて、メモリに記憶された展開情報を利用せずに、メモリを初期化して新たに情報を展開して復帰する通常復帰が行われるように制御し(104〜112)、閾値以上の電圧が検出されない場合にはメモリに記憶された展開情報を利用する省エネ復帰が行われるように制御する(104)。

(もっと読む)

情報更生装置、メモリ制御システム、情報更生方法およびコンピュータプログラム

【課題】 記憶容量が不足する事態を抑制しながら、メモリにおける情報保持性能の信頼性を高める。

【解決手段】 更生部2を備える。当該更生部2は、メモリから読み出された情報に含まれるビット誤りの数を誤りビット数として前記メモリにおける予め定められたメモリ領域毎に計数する機能を備えている。また、更生部2は、その誤りビット数が予め定められた閾値以上である前記メモリ領域には、当該メモリ領域とは別のメモリ領域に事前に書き込まれていたバックアップ情報を上書きする機能を備えている。

(もっと読む)

メモリコントローラ

【課題】フラッシュメモリに格納されるデータの信頼性を確保するとともに、構成を簡略化することができるメモリコントローラを提供することを課題とする。

【解決手段】メモリコントローラ3は、読み出しコマンドを受け付けた場合、通常アクセス領域41から格納データ50を読み出し、格納データ50のエラーを訂正する。格納データ50のエラーがECC回路34のエラー訂正能力の範囲内である場合、メモリコントローラ3は、エラー訂正された格納データ50に含まれる実体データを出力する。格納データ50のエラーがエラー訂正能力を超えている場合、メモリコントローラ3は、格納データ50のバックアップデータである格納データ70を、バックアップ領域42から読み出し、格納データ70に含まれる実体データを出力する。ホストコントローラ3は、格納データ70を用いて、通常アクセス領域41に格納された格納データ50を修復する。

(もっと読む)

電子機器

【課題】不揮発性メモリにおける記憶ブロック間のデータ消去回数のばらつきを抑える。

【解決手段】電子制御装置は、フラッシュROMを備える。フラッシュROMは、複数の記憶ブロックを備え、記憶ブロック単位でのデータ消去が可能な周知のメモリである。電子制御装置のMPUは、フラッシュROMの記憶ブロック群を、書込頻度が低いデータ記憶用の低頻度ブロック群と、書込頻度が高いデータ記憶用の高頻度ブロック群とにグループ化する。そして、高頻度ブロックのデータ消去回数に基づき、データ消去回数が100の倍数となる度、低頻度ブロックを、記憶ブロック一つ分ずらすようにして、高頻度ブロックと入れ替える。この動作によって、フラッシュROM内の記憶ブロック群を再グループ化する。一般的に高頻度ブロックのデータ消去回数のほうが低頻度ブロックよりも多くなるが、再グループ化により記憶ブロック間のデータ消去回数のばらつきは抑えられる。

(もっと読む)

情報処理端末及び管理サーバ

【課題】フラッシュメモリに書き込まれたデータの信頼性を向上することができる技術を提供することを課題とする。

【解決手段】メモリカード7Aは、コンテンツデータAを記録するメモリ71と、メモリコントローラ72とを備える。メモリコントローラ72は、メモリ71のエラーブロックのアドレスを記録したエラー発生データ75Aを作成する。エラー発生データ75Aは、情報処理端末4を介して、集計サーバ1に送信される。集計サーバ1は、複数の情報処理端末から受信したエラー発生データ75Aを集計して、メモリ71において検査対象となる検査領域を設定し、検査領域が記録された個別検査領域データ16Aを作成する。情報処理端末4は、個別検査領域データ16Aを集計サーバ1から取得して、メモリコントローラ72に出力する。メモリコントローラ72は、個別検査領域データ16Aに基づいて、メモリ71で検査する領域を決定する。

(もっと読む)

コンピュータ、その制御方法及びプログラム

【課題】MBRとバックアップセクタデータを検証し、正常にリードできない又は不正であるときに、自動的に復旧し起動処理を実行する。

【解決手段】シャットダウンを検知した場合に、MBRとバックアップMBRのリードを行い、MBRのデータとバックアップMBRのデータとが同一でないときにMBRをバックアップMBRにコピーするか、バックアップMBRが正常にリードできない又は不正であるときにMBRをバックアップMBRにコピーするかする。コンピュータの電源をオンした場合に、バックアップMBRが正常にリードできない又は不正であるときにMBRをバックアップMBRにコピーする。

(もっと読む)

RAM値保証装置およびRAM値保証プログラム

【課題】RAMの記憶容量を抑制しながらRAMの記憶値を保証できるようにしたRAM値保証装置およびRAM値保証プログラムを提供する。

【解決手段】CPUは、OSによりプログラムカウンタ6の示すアドレスを監視し、非保証プログラム領域9から保証プログラム領域10にプログラムカウンタ6のアドレスが遷移することを確認すると、保証RAM領域12のデータとバックアップRAM領域13のデータとを比較し、当該データが異なっているときには保証RAM領域12のデータをバックアップRAM領域13のデータで更新する。CPU8はOSによりプログラムカウンタ6の示すアドレスを監視し、更新許可領域10aから更新許可領域10bにプログラムカウンタ6のアドレスが遷移することを確認すると、その遷移直前にRAM_A群バックアップ13aの更新を許可し、RAM_A群バックアップ13aのデータをRAM_A群12aのデータで更新し、更新処理後にRAM_A群バックアップ13aの更新を禁止する。

(もっと読む)

画像処理装置、リフレッシュ方法およびプログラム

【課題】画像処理装置に設けられた不揮発性メモリに対して、比較的に簡素な構成で適切にリフレッシュを行うことができるようにする。

【解決手段】画像処理装置は、自装置で用いられるデータを保存する不揮発性メモリと、自装置の動作状況を認識する認識手段101と、認識手段101が認識した動作状況をと、記憶部に予め記憶された自装置の動作状況ごとの温度変化を示す動作温度情報とを用いて、不揮発性メモリのリフレッシュの要否を判定する判定手段102と、リフレッシュが必要であると判定手段102が判定した場合、不揮発性メモリをリフレッシュするリフレッシュ手段103と、を備える。

(もっと読む)

情報処理装置

【課題】ストレージデバイスとして利用される不揮発性の記録媒体が寿命を迎えてもシステムを正常に起動することができる情報処理装置を提供すること。

【解決手段】情報処理装置は、起動中のシステムを終了して次に起動する際に必要なバックアップ対象情報が格納される不揮発性のメインメモリと、システムの起動及び終了に係る各処理を行うホスト制御部とを備える。メインメモリは、当該メインメモリに書き込まれたバックアップ対象情報を保持するメモリセル群と、メモリセル群への書き込みエラーが発生したとき、当該メインメモリが寿命を迎えたか否かを判断する制御部とを有する。ホスト制御部は、メインメモリが寿命を迎えたと制御部によって判断された際、メインメモリとは異なる不揮発性の補助メモリにバックアップ対象情報を格納し、システムの起動に係る処理を行う際には補助メモリからバックアップ対象情報を読み出す。

(もっと読む)

メモリデバイスにおける読み出し不可状態を解決するための装置及び方法

【課題】ブートエラーを正すための装置及び方法を提供する。

【解決手段】装置100は、不揮発性のメモリデバイス120を有し、そのメモリデバイス120は、第1のアドレスを持つ所定のブロックに、ブートローダーを格納している。装置100は、さらに、電源投入時に、所定のブロックからブートローダーを読み出すメインコントローラー110を有している。装置100は、また、メインコントローラー110の最初のブートシーケンスを監視するとともに、所定のブロックが、読み出し不可エラー状態に陥ったことを判定するように構成された監視モジュール130を含んでいる。監視モジュール130が、所定ブロックは読み出し不可エラー状態に陥ったと判定したとき、メインコントローラー110は、バックアップブロックからバックアップブートローダーを取得する。

(もっと読む)

メモリアクセス処理システム、制御方法、及びプログラム

【課題】CPUの要求するメモリアクセスを処理すること。

【解決手段】複数のメモリモジュール110のページのうち、過熱状態にあるメモリモジュール110のページを、過熱状態にないメモリモジュール110のページへ移動させるべく、過熱状態にあるメモリモジュール110のページの仮想アドレスと、過熱状態にないメモリモジュール110のページの仮想アドレスとを入れ替えるメモリ管理部150を備える。

(もっと読む)

記憶制御装置、記憶制御プログラムおよび記憶制御方法

【課題】リストア処理における処理時間の増大を抑制することを目的とする。

【解決手段】コンピュータに、第1のデータ群に対応するデータ群である第2のデータ群を前記第1のデータ群を記憶する記憶装置に格納する処理を指示された場合に、前記記憶装置に記憶された前記第1のデータ群に含まれる各データを順次バックアップする処理と、前記第2のデータ群に含まれる各データを順次前記記憶装置に格納する処理と、を開始し、前記第1のデータ群のうち、前記バックアップする処理が終了したデータについて、バックアップする処理が終了した旨を示す情報を記憶手段に記憶し、前記第2のデータ群に含まれるデータについて前記バックアップする処理が終了した旨を示す情報が前記記憶手段に記憶されていない場合に、前記第2のデータ群に含まれる前記データを前記記憶装置に格納する処理の実行を抑止する、ことを実行させる。

(もっと読む)

データリテンション動作を実行する使用者装置、データ格納装置、及びそれのデータリテンション方法

【課題】グローバルタイムを参照してデータリテンション動作を実行する使用者装置、格納装置、及びそれのデータリテンション方法を提供する。

【解決手段】本発明のデータ格納装置の駆動方法は、データ格納装置をオフライン状態でオンライン状態に転換する段階と、オンライン状態の間にホストから現在のグローバルタイム(Global time)を受信する段階と、オンライン状態の間に現在のグローバルタイム(Current global time)を参照してデータ格納装置に格納されたデータを少なくとも1つのノーマルデータリテンション動作を通じてリフレッシュする段階と、を含む。

(もっと読む)

電子機器およびシステム管理プログラム

【課題】 電子機器においてスリープ状態と通常状態との間の状態遷移が多く発生しても、コントローラープログラムに発生するリードディスターブエラーを回避して、継続して正常に動作させる。

【解決手段】 メインコントローラー11は、画像形成装置1の動作状態をスリープ状態に移行させる。そのスリープ状態は、メインコントローラーの電源がオフとなる動作状態である。そして、メインコントローラー11は、コントローラープログラム32を記憶した不揮発性メモリー22と、コントローラープログラム32を読み出して実行するMPU24とを有し、コントローラープログラム32に従って、不揮発性メモリー22からのコントローラープログラム32のリード回数が所定の閾値に到達すると、画像形成装置1の動作状態をスリープ状態に移行させる前に、不揮発性メモリー22におけるコントローラープログラム32の記憶領域に対する修復処理を実行する。

(もっと読む)

メモリアクセス制御装置

【課題】再書き込み可能な不揮発性半導体メモリに対する負荷を抑えつつ、リードディスターブ現象により生じるエラーに対処する技術を提供することを課題とする。

【解決手段】メモリ4は、ページ単位での読み出しと、ブロック単位で消去が可能である。リードカウンタ5は、メモリ4に対するリード回数RCをブロック単位でカウントする。メモリコントローラ3は、リード回数RCがリード回数閾値RCthを上回る検査対象ブロックが存在するか否かを判定する。メモリコントローラ3は、検査対象ブロックが検出された場合、検査対象ブロックに含まれる各ページに対してエラー検出処理を行い、エラー閾値EBthを超えるエラーが検出されたエラーページが存在するか否かを検査する。エラーページが検出された場合、検査対象ブロックに対してデータの再書き込み処理を実行する。再書き込み処理終了後、検査対象ブロックのリード回数RCを初期化する。

(もっと読む)

NORフラッシュメモリの読み取り方法

【課題】NORフラッシュメモリの読み取り方法を提供する。

【解決手段】

本発明は、NORフラッシュメモリの読み取り方法を提供し、組込み式Linuxオペレーションシステムで使用され、巡回冗長検査値を照合し、カウンタに予め設けられた繰り返し読み取り回数の閾値により、ジャーナリングファイルシステムデータの繰り返し読み取りを継続するか否かを決定する。

(もっと読む)

データ転送装置、メモリ制御装置、およびメモリシステム

【課題】誤り訂正が発生したとしてもデータ伝送が待たされる時間を少なくし、データ転送に要する時間を短縮することが可能なデータ転送装置、メモリ制御装置、およびメモリシステムを提供する。

【解決手段】データ転送元の第1メモリ装置200の第1メモリアドレスと、データ転送先の第2メモリ装置の第2メモリアドレスと、転送データに誤りが検出されたか否かを示す誤り信号と、誤り訂正が完了して第2メモリ装置106に格納しているデータが有効であるか否かを示す有効信号を記憶する領域を複数含むデータ情報記憶領域109と、第2メモリ装置に格納しているデータのうち、データが有効であるメモリのアドレスである第2メモリ有効アドレスを出力し、第2メモリ装置の第2メモリ有効アドレスからデータを読出し、読出したデータと共に、第2メモリ有効アドレスに対応する第1メモリ装置のアドレスを転送する制御部108とを有する。

(もっと読む)

メモリシステム

【課題】データ記憶の信頼性を容易に高めることができるメモリシステムを提供する。

【解決手段】実施形態のメモリシステムは、揮発性の第1の記憶部を介してホスト装置と不揮発性の第2の記憶部との間のデータ転送を行うコントローラを備えている。前記コントローラは、前記第2の記憶部に記憶されたデータの格納位置を含む管理情報を前記第1および第2の記憶部で更新しながら前記管理情報に基づいてデータ管理を行う。前記コントローラは、最新状態の管理情報と、当該管理情報の前記第2の記憶部での保存位置を示すポインタと、前記ポインタの書込みが成功したか否かを示すログとを、前記ポインタを多重化して前記第2の記憶部に記憶させる。前記コントローラは、起動時に前記ポインタが所望数だけ多重化されていなければ、前記ポインタおよび/または前記ログに基づいて、前記ポインタの多重化をリカバリ処理する。

(もっと読む)

1 - 20 / 181

[ Back to top ]