Fターム[5B018MA32]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | アドレス回路、アドレス線 (15)

Fターム[5B018MA32]に分類される特許

1 - 15 / 15

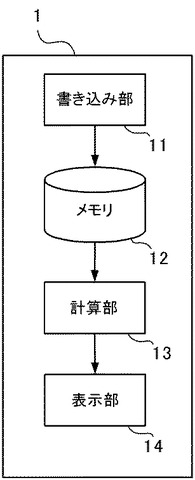

メモリ書き込み確認装置、メモリ書き込み確認方法およびプログラム

【課題】データの正常性だけでなく、書き込みアドレスの正常性も確認する。

【解決手段】書き込み部11は、メモリ12にデータを書き込み、計算部13は、書き込み部11がメモリ12に書き込んだデータのデータ・チェックサム値とデータを書き込んだアドレスのアドレス・チェックサム値とを計算し、データ・チェックサム値とアドレス・チェックサム値を合計したチェックサム合計値を計算する。表示部14は、データ・チェックサム値とチェックサム合計値を表示する。

(もっと読む)

電子装置、及び、これを用いた電動パワーステアリング装置

【課題】アドレスバスおよびデータバスの故障を検出する電子装置において、故障検出に係る処理負荷を低減し処理速度を向上する。

【解決手段】電子装置は、CPUとROMとを接続しアドレスを伝送する4つ以上のバスラインからなるアドレスバス21を備える。電子装置は、アドレスバス検査用アドレスAdによって指定されるROM領域13aから値を読み出し、読み出した値から計算した判定値Vjと予め計算されたアドレスバス検査用正解値Vtとを比較し、一致しない場合、アドレスバス21が故障していると判定する。アドレスバス検査用アドレスAdは、4つ以上のバスラインに対応する4ビット以上の値であって、2ビット以上の0の値と2ビット以上の1の値とを有する値を含み、複数のバスライン間の短絡故障を同時に検出可能である。これにより、故障検出に必要な検査用アドレスAdの数を低減することができる。

(もっと読む)

メモリ回路及びメモリ回路制御方法

【課題】出力するデータ量を増加させることなく、チップ間のアドレスの転送誤りを検出することができるメモリ回路を提供すること

【解決手段】本発明のメモリ回路は、アドレス毎にデータが対応付けられたメモリ103を搭載するメモリチップ102と、メモリチップ102に接続されメモリ103のアドレスを指定してアドレスに対応するデータを読み出すメインチップ101と、を備える。メモリチップ102は、メインチップ101において指定され入力されたアドレスを取得するアドレス情報取得部105と、メモリ103内のデータをアドレスを用いて暗号化し、メインチップ101へ出力する暗号部104を備え、メインチップ101は、暗号部104から出力された暗号化データを、指定したアドレスを用いて復号化する復号部113と、復号化されたデータに誤りがあるか否かを判定する判定部116とを備えるものである。

(もっと読む)

アドレスバスのテスト方法及びテスト装置

【課題】アドレスバスとデータバス夫々のバス幅の相対的な関係に依存せずにアドレスバスのテストをすること。

【解決手段】複数のメモリセルを有するメモリ装置20へ伝送される複数ビットのアドレスパタンの伝送路であるアドレスバス15aのテスト方法は、次のステップを含む。全ビットが第1論理値であるアドレスパタンにより特定されるメモリセルに対して第1論理値を書き込み、あるビットがその他の全てのビットとは異なり第2論理値である複数のアドレスパタン夫々により特定されるメモリセルに対して第1論理値を書き込み(S1)、第1のアドレスパタンにより特定されるメモリセルに対して第1論理値とは異なる値の第2論理値を書き込み(S5)、第2のアドレスパタンにより特定され、かつ第1論理値が読み出されるべきメモリセルからの第2論理値の読み出しに基づいてアドレスバスの不良を検出する(S4)。

(もっと読む)

アドレス線の試験方法及び試験装置

【課題】

試験時間の短縮化を図ったフラッシュメモリのアドレス線及び試験装置の試験方法及び試験装置を提供することを課題とする。

【解決手段】

全ての記憶を第1データ値にする第1工程と、特定のアドレス線を第1アドレス値に、その他のアドレス線を第2アドレス値に設定し、設定されたアドレスが示す記憶単位のうち特定の記憶を第2データ値とし、他の記憶は第1データ値とする書き込みを記憶単位に行う第2工程と、特定のアドレス線以外の他のアドレス線を第1アドレス値に設定し、特定の記憶と記憶単位上の位置が異なる記憶を第2データ値として、第2工程を行う第3工程と、第2工程と第3工程を繰り返し行った後に、全てのアドレス線を第2アドレス値に設定したアドレスが示す記憶単位を検査する第4工程とを有する。

(もっと読む)

メモリの誤り訂正方法,誤り検出方法、及びそれを用いたコントローラ

【課題】

メモリとの接続故障の誤り訂正,検出方法が必要になってきた。

【解決手段】

プロセッサと、メモリ制御装置と、メモリ装置とを備えたコントローラにおいて、アドレスに対して任意のデータをライトアクセスするとき、アドレスと任意のデータから決定される誤り検出符号CRCと、誤り検出符号CRCと任意のデータから決定される誤り訂正符合ECCを生成し、任意のデータと伴に誤り検出符号CRCと誤り訂正符号ECCをメモリ装置に書き込み、プロセッサが任意のアドレスに対してリードアクセスするとき、メモリ装置に書き込まれている誤り訂正符号ECCと、誤り検出符号CRCとデータを読み出し、読み出した誤り訂正符号ECCに基づき読み出した誤り検出符号CRCと読み出したデータの誤りを訂正し、訂正された誤り検出符号CRCと読み出したデータに誤りが有るか検出する。

(もっと読む)

メモリの検査方法

【課題】従来のメモリ検査方法では、異常が生じているアドレス信号線の位置を知ることができても、それが短絡しているのか開放しているのかは判別できないという問題があった。

【解決手段】メモリのアドレスを指定する複数のアドレス信号線を有するメモリの検査方法であって、前記基準アドレスと、検査アドレスと、検査隣接アドレスとを特定するビットを前記第1検査アドレス信号線のビットと、前記第2検査アドレス信号線のビットとの組合せが異なり、前記第1検査アドレス信号線のビット及び前記第2検査アドレス信号線のビットを除く他のビットは共通となるように決定するステップと、前記基準アドレスと、検査アドレスと、検査隣接アドレスにそれぞれ異なるデータを書き込むステップと、前記基準アドレスと、検査アドレスと、検査隣接アドレスからデータを読み取り、書き込んだデータと同一か否かを判断するステップとを有する。

(もっと読む)

メモリコントローラおよびメモリ制御方法

【課題】メモリ2重化システムにおいて、障害情報に対してリアルタイムに対処するとともに、アドレス線のエラーを推定することでシステムダウンを防止することを課題とする。

【解決手段】LDX#1およびLDX#0は、それぞれが所持するECC情報(ECCチェックのための情報)を交換してECCチェックを行い、リクエストデータの一部についてそれぞれECC(Error Correcting Code)チェックを行って、アドレス線にエラーが発生しているか否か推定する。具体的には、例えば、LDX#0は、リクエストデータの一部に関するECCチェック結果であるシンドローム(診断情報)を作成し、このシンドロームから把握されるリクエストデータの一部に関するエラーの状況に応じて、例えば、リクエストデータの大部分がアンコレクタブルエラーを起こしている場合には、アドレス線にエラーが発生しているものと推定する。

(もっと読む)

半導体記憶装置及び半導体記憶装置機能検査方法並びに半導体記憶装置を有する電子機器

【課題】 半導体記憶装置及び半導体記憶装置を有する電子機器のアドレス、データバス、システムバスの検証に乱数で作成したアドレス、データを使用することで、クロストーク、ノイズの影響によるデータ化けを精度よく検出する。

【解決手段】 半導体記憶装置Aー1、Aー2、A―XXX,B−1、B−2、B―XXX,X−1、X−2、X−XXXに擬似乱数発生器2で書込まれた乱数アドレスのデータを書込むと共に半導体記憶装置Aー1、Aー2、A―XXX,B−1、B−2、B―XXX,X−1、X−2、X−XXXに書き込まれた乱数アドレスのデータを読出し、書込みデータと読出しデータは比較手段を介して比較することで特定のビット配列で生ずる機能障害を検出する半導体記憶装置及び半導体記憶装置機能検査方法並びに半導体記憶装置を有する電子機器を提供する。

(もっと読む)

記憶制御回路、記憶制御回路におけるアドレスエラーチェック方法

【課題】 従来の記憶制御回路は、アドレスに関する多ビットエラーを検出することができないでいた。

【解決手段】 アドレスで指定される記憶領域にデータを格納する記憶部を有する記憶制御回路におけるアドレスエラーチェック方法であって、前記アドレスに付与する第1のコードを偶数ビットで符号化し、前記記憶部へ書き込まれるデータに付与する第2のコードを奇数ビットで符号化し、前記第1のコードと前記第2のコードとに基づき、チェックコードを生成して前記記憶部へ書き込まれるデータに対応付けて前記記憶部に格納し、前記記憶部から読み出されるデータと、該読み出されるデータに対応付けられたチェックコードと、読み出しアドレスとに基づき、エラーチェックを行うことにより、アドレスの多ビットエラーを検出する。

(もっと読む)

制御装置

【課題】システム運用中の主記憶装置に固定故障検出データを書き込まずに、かつ効率的にアドレス線の固定故障を特定することができること。

【解決手段】任意のデータは、アドレスの誤り訂正符号を有し、データ読出部101は、複数のアドレス線の0固定故障を検出するアドレスである0固定故障検出アドレスおよび/または複数のアドレス線の1固定故障を検出するアドレスである1固定故障検出アドレスに基づいて主記憶装置30から任意のデータを読み出し、誤り検出/訂正部102は、読み出された任意のデータが有する誤り訂正符号に基づいて0固定故障検出アドレスおよび/または1固定故障検出アドレスのビット誤りをそれぞれ検出/訂正し、固定故障判定部103は、誤り検出/訂正部102による誤り検出/訂正結果に基づいてアドレス線の0固定故障または1固定故障を判定する。

(もっと読む)

メモリアクセスエラーの検出及び/又は訂正方法、並びにこの方法を実行するための電子回路構成

メモリ(4)内に、保護対象のデータ(D)の他に、このデータ(D)を用いて生成したチェックデータ(P)を保存している、プロセッサシステムでのメモリアクセスエラーを検出及び/又は訂正するための方法は、誤り検出及び訂正時において特に高い信頼性を達成可能な形態に改善することが求められている。このために、この発明では、チェックデータ(P)の生成の際に、保護対象のデータ(D)の他に、そのアドレスをも考慮している。  (もっと読む)

(もっと読む)

マージバッファのシステムキルエラーのプロセスキルエラーへの変換技術

【課題】 本発明の課題は、上記問題点に鑑み、マージバッファのシステムキルエラーをプロセスキルエラーに変換する方法、装置及びシステムを提供することである。

【解決手段】 上記課題を解決するため、本発明は、データ及び該データが格納されるアドレスを有し、1以上のプロセスに係るストア命令を収集するバッファと、第1プロセスに係るストア命令を、前記バッファが第2プロセスに係るストア命令を収集する前に前記バッファから常にドレイン処理するバッファ制御とから構成されることを特徴とする装置を提供する。

(もっと読む)

セグメント・レベルの予備化を実現するシステム、方法、およびプログラム

【課題】 セグメント・レベルで予備化したメモリ・システムを提供する。

【解決手段】 このメモリ・システムはセグメント・レベルで予備化した、カスケード型相互接続システムを含んでいる。このカスケード型相互接続システムは少なくとも2つのメモリ・アセンブリとメモリ・バスを備えている。このメモリ・バスは複数のセグメントを備え、このメモリ・アセンブリは当該メモリ・バスを介して相互接続されている。

(もっと読む)

電気機器

【課題】 バックアップメモリの信頼性を向上させることができる電気機器を提供する。

【解決手段】 データ書込部11は、バックアップメモリ40内におけるアドレスデータをバックアップデータに付加してバックアップメモリ40に書き込み、データ読出部12は、バックアップデータを読み出す前にアドレスデータを読み出し、バックアップメモリ40の読み出し先のアドレスと、読み出されたアドレスデータとを比較し、両アドレスが一致する場合、バックアップデータを読み出す。

(もっと読む)

1 - 15 / 15

[ Back to top ]