Fターム[5B033BA01]の内容

Fターム[5B033BA01]に分類される特許

1 - 20 / 49

複数の状態のプロセッサのための命令のキャッシング

演算処理装置および演算処理方法

【課題】命令メモリへのアクセス回数を削減し、消費される電力を低減することができる演算処理装置および演算処理方法の提供を図る。

【解決手段】プロセッサと、予め複数の命令が格納されている命令メモリと、前記プロセッサから命令アドレスを受け取り、命令メモリにアクセスして第1命令を読み取る命令展開装置6と、を有し、前記命令展開装置は、前記第1命令が展開可能な命令か否かを判断する展開判定部64と、前記第1命令が展開可能な命令であれば、同じオペコードでオペランドを同じステップ幅で変化させて2語以上の第2命令に展開する命令展開部65と、を有し、2語以上の前記第2命令を1サイクルごとに前記プロセッサに出力する。

(もっと読む)

プロセッサ、圧縮プログラム、圧縮装置、および圧縮方法

【課題】メモリアクセス回数の低減化を図ること。

【解決手段】圧縮装置101は、命令列ISsを圧縮する。圧縮装置101では、アドレスが連続する2つの命令間において、オペコードが同一であり、オペランド間に連続性がある場合に、圧縮をおこなう。たとえば、連続する命令IS1,IS2間では、オペコードがともにADDで、オペランドが1増加している。このため、命令IS2は圧縮される。同様に、命令IS3も圧縮される。命令IS3,IS4間,命令IS4,IS5間,および命令IS5,IS6間では圧縮はおこなわれない。命令IS6については、命令IS5を無視して、命令IS4との関係で圧縮が行われる。圧縮命令群issには、復元元となる命令と復元元の命令を参照して復元可能な圧縮命令が混在する。プロセッサ102は、圧縮命令群issをフェッチすることで、圧縮命令を復元して命令を実行する。

(もっと読む)

情報処理装置

【課題】 パイプライン処理の停止を低減するとともに、ループ処理が実施されている期間のアクセス効率を向上する。

【解決手段】 情報処理装置は、命令を取得するフェッチ部と、命令を解読するデコード部と、フェッチ部から出力される命令を順次記憶する書き込み動作と、ループ処理の範囲に対応する命令を繰り返し出力する読み出し動作とを切り替えて実施する命令バッファ部と、書き込み動作が実施されているとき、フェッチ部から出力される命令をデコード部に出力し、読み出し動作が実施されているとき、命令バッファ部から出力される命令をデコード部に出力する選択部とを有している。

(もっと読む)

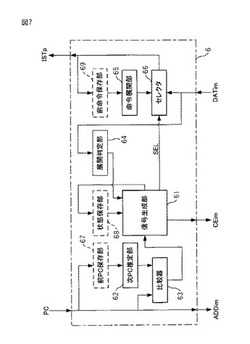

演算装置及びエラー検出方法

【課題】エラーの検出効果を高くする。

【解決手段】演算装置1は、命令制御部100と、第1オペランド制御部200と、第2オペランド制御部300と、演算部400と、NOP検出部500と、エラー検出部600と、を備える。NOP検出部500が出力する制御信号に従って、命令制御部100、第1オペランド制御部200及び第2オペランド制御部300は、直前のクロックサイクルで受信した入力信号を試験信号として演算部400に出力する。エラー検出部600は、演算部400が求めた演算結果データと試験演算結果データとを比較し、エラーが発生しているか否かを判別する。

(もっと読む)

可変長命令のプリデコーディング

【課題】プロセッサにおける可変長命令をプリデコーディングする方法を提供する。

【解決手段】可変命令長プロセッサにおけるプリデコーダは、命令と共に命令キャッシュに格納されたプリデコードビットで命令の属性を表示する。1の長さ命令と関連付けられたプリデコードビットPD0、PD1の全符号化が定義されるとき、その長さの命令の属性は、異なる長さの命令をエミュレートするために命令を変更し、異なる長さの命令と関連付けられたプリデコードビットの属性を符号化することによって表示される。そのように表示される属性の1つの例は未定義命令である。

(もっと読む)

ベクトルマスク設定技術

【課題】本発明の課題は、マイクロプロセッサアーキテクチャの命令セットアーキテクチャにおいて使用される効果的なベクトルマスク生成技術を提供することである。

【解決手段】本発明によると、上記課題は、ベクトルマスクを格納するための第1処理を検出する第1ロジックと、前記第1処理より以前のベクトルマスク値を生成するための最新の第2処理を特定する第2ロジックと、前記第2処理が特定される場合、前記第1処理の実行を回避する第3ロジックとから構成されることを特徴とするプロセッサにより解決される。

(もっと読む)

命令が利用可能な汎用レジスタの数を拡張するための上位ワード・ファシリティ

【課題】 汎用レジスタのようなアーキテクチャ・リソースへの依存を軽減し、新しい命令を用いるソフトウェア・バージョンの機能及び性能を改善する、既存のアーキテクチャと整合性が取れた新しい命令機能を提供する。

【解決手段】 コンピュータが、1組の汎用レジスタ(GPR)を利用する。各々のGPRは、複数の部分を含む。大容量GPRモードで動作するオペレーティング・システム及びアプリケーションのようなプログラムは、GPR全体にアクセスするが、小容量GPRモードで動作するアプリケーションのようなプログラムは、一度に一部分にしかアクセスすることができない。小容量GPRモードにおいて、命令オペコードは、どの部分にアクセスするかを決定することができる。

(もっと読む)

プロセッサ

【課題】実行可能な命令を増やした場合でも、高速に演算が可能なプロセッサを提供する。

【解決手段】プロセッサ1は、命令に応じて行われる処理の内容に基づいて、実行可能な命令を、Mタイプ命令、Rタイプ命令、Jタイプ命令、Bタイプ命令の4つの命令タイプに分類する命令デコーダCTRLを備える。またプロセッサ1は、命令タイプに対応して設けられたパイプラインレジスタ11〜14を備えている。命令デコーダCTRLは、命令に含まれる識別コードに基づいて、実行対象の命令の命令タイプを解読する。また命令デコーダCTRLは、命令の命令タイプに基づいて汎用レジスタブロックREGに格納されたデータや命令内のパラメータを対応するパイプラインレジスタに格納する。

(もっと読む)

マイクロプロセッサ

【課題】用途に応じて同一マイクロプロセッサを使い分ける場合に、命令デコード、命令実行などにより規定される最大動作周波数の制約が発生する。

【解決手段】本発明は、例えば、用途に応じて、最大動作周波数を可変にするために、命令または命令セットの一部を無効化させることを特徴とする。一例として、命令を、メモリから読み出してフェッチする命令フェッチ部と、命令フェッチ部でフェッチした命令に対するデコード処理を行う命令デコード部と、デコード後の命令に対する処理を実行する命令実行部とを有して構成されるマイクロプロセッサにおいて、前記命令デコード部が、外部設定値を入力とし、外部設定値によって、一部の命令をデコード対象から除外すること、または低速化させることを特徴とする。

(もっと読む)

データプロセッサ

【課題】プレフィックス付きの命令を含む命令セットにおいて効率的なスーパースカラ命令発行と低消費電力とを実現する。

【解決手段】命令コードに対して、プレフィックスコードか、それ以外の命令コードかを判定し、その判定結果と前記16ビットの命令コードとを出力する命令フェッチ部(FTC)を採用すると共に、その判別結果に基づいて命令コードデコードするデコーダ(BDYDEC1,BDYDEC2)とプレフィックスコードをデコードするデコーダ(PRFDEC1,PRFDEC2)とを別々に配置する。さらに、プレフィックスはこれが修飾する16ビットのような固定長命令コードよりも先にデコーダに供給される。プレフィックスコードの後続の固定長命令コードは、プレフィックスコードのデコーダと同じパイプライン(Pipe1,Pipe2)のデコーダに供給される。

(もっと読む)

信号処理装置、表示制御装置、及び、信号処理装置のレジスタ設定方法

【課題】ソフトウェアが介在することなく、複数の製品グレード、及び、仕様変更等に柔軟に対応できる信号処理装置、表示制御装置、及び、信号処理装置のレジスタ設定方法を提供する。

【解決手段】外部入力されるオペレーションコードから内部の制御コードへの変換データを保持するレジスタ11と、レジスタ11の値に基づいて前記オペレーションコードを前記制御コードに変換するデコーダ12と、デコーダ12により変換された制御コードに基づいて所定の処理を実行する単一または複数の信号処理部13を備えている信号処理装置1であって、レジスタ11を初期化するリセット回路14を備え、リセット回路14によるリセット解除後にレジスタ11に前記変換データを設定する変換データ設定部15を備えている。

(もっと読む)

パイプライン型プロセッサ

【課題】汎用レジスタの書き込み/読み出し回数の低減および消費電力の低減が可能なパイプライン型プロセッサを提供する。

【解決手段】EステージとWBステージの間に配置されたパイプラインレジスタ1、2が、保持しているデータの有効性を示すデータ有効フラグ(F1、F2)および保持しているデータの前記汎用レジスタへの書き込みを制御する書き込み制御フラグ(W1、W2)を格納する領域を有し、データ有効フラグが「有効」を示すときは、汎用レジスタ100の代わりにパイプラインレジスタ1、2を読み出すバイパス回路3を備え、書き込み制御フラグによる汎用レジスタ100への書き込み終了後も、パイプラインレジスタ1、2に保持されているデータを引き続き保持し、先行命令とデータ依存関係にある後続命令の実行時に、バイパス回路3を介してEステージへ供給する。

(もっと読む)

データ処理装置

【課題】再構成可能な論理回路の再構成時間を短縮し、データ処理の高速化は図ることができるようにしたデータ処理装置を提供する。

【解決手段】回路情報源15に論理回路Bの論理回路Aとの差分回路情報W(A→B)を保持させる。論理再構成制御部16は、再構成可能な論理回路12に論理回路Aを再構成して論理回路Aに任されている処理を実行させた後、再構成化可能な論理回路12に論理回路Bを構成する場合、回路情報源15から論理回路Bの論理回路Aとの差分回路情報W(A→B)を読み出し、再構成可能な論理回路12内の再構成を必要とする番地の情報と、再構成する番地の回路情報とを回路情報保持レジスタ19に転送する。

(もっと読む)

命令キャッシュ・ラインにまたがる命令のためのプレデコード修復キャッシュ

プログラムで混用されることができる少なくとも2つの長さの命令を有する可変長命令を取得し実行することが可能なプロセッサにおけるプレデコード修復キャッシュが説明される。命令キャッシュは、少なくとも、第1の長さを有する命令と第1の長さより長い第2の長さを有する命令とを命令キャッシュ・ラインに格納するように動作可能である。プレデコーダは、命令キャッシュから取得した修復されたプレデコード情報を形成するための、無効プレデコード情報を有する命令をプレデコードするように動作可能である。プレデコード修復キャッシュは、命令キャッシュ内の2つのキャッシュ・ラインにまたがる第2の長さの命令に関係づけられた修復されたプレデコード情報を格納するように動作可能である。また、プレデコード修復キャッシュを満たすための方法、および2つのキャッシュ・ラインにまたがる命令を実行するための方法が説明される。 (もっと読む)

命令ビット長削減方法

【課題】プログラム格納用のメモリサイズを小さくする。

【解決手段】ソースプログラムをオブジェクトプログラムに変換する際に、同一のレジスタを続けて使用する命令コードが複数ある場合に、これらの命令コードが連続するように変換する。また、変換したmビットの命令コードの内で有効ビット数がnビット以下の命令コードに対しては、下位のビット位置に無効ビットを配置すると共にレジスタを指定するオペランドを上位の一定のビット位置に配置する。一方、命令コードの有効ビット数がnビットを越える命令コードに対しては、レジスタを指定するオペランドを削除する。この結果、オブジェクトプログラムを構成する各命令コードの有効ビット数はnビット以下になる。従って、上位nビットをプログラム格納用のメモリに書き込むことで、プログラム格納用のメモリサイズを小さくすることができるという効果がある。

(もっと読む)

マイクロプロセッサ

【課題】特定の命令の実行時の消費電力を低減させることのできるマイクロプロセッサを提供する。

【解決手段】プロセッサコア3は、命令フェッチ部31および命令デコード部32を備え、命令キャッシュ1からフェッチした命令のパイプライン処理を行う。命令解析部2は、命令キャッシュ1へ入力される命令が特定命令格納部21に格納された命令であるかどうかを解析して命令解析情報を出力する。命令キャッシュ1のタグ格納部12内の命令解析情報記憶領域13は、命令解析部2から出力された命令解析情報を記憶する。プロセッサコア3の特定命令実行制御部34は、命令フェッチ部31が命令キャッシュ1から命令をフェッチするときに、その命令に対する命令解析情報を命令解析情報記憶領域13から読み出し、その命令が特定の命令であることを読み出した命令解析情報が示しているときは、命令フェッチ部31および命令デコード部32の動作を制御する。

(もっと読む)

命令コード圧縮方法と命令フェッチ回路

【課題】フェッチ回数とプログラムコードを共に削減することが可能な、命令コード圧縮方法と命令フェッチ回路を提供する。

【解決手段】演算コードOPCODE等を含む上位ビット群と、オペランドOPR2等を含み上位ビット群と同じビット数の下位ビット群とで構成される命令コードの下位ビット郡に再利用フラグRを設け、一連の命令コードの内で上位ビット群が同一である命令コードが2N+1(但し、Nは1以上の整数)個連続するときに、その連続する命令コードの内の2n(但し、nは1以上でN以下の整数)番目の命令コードと2n+1番目の命令コードの下位ビット群の各再利用フラグRを“1”にセットすると共に、これらの2n番目と2n+1番目の命令コードの下位ビット群を統合して1つの圧縮命令コードに置き代える。

(もっと読む)

プロセッサ

【課題】プログラムサイズを削減する。

【解決手段】プロセッサは、複数のレジスタと、メモリから命令を読み出す命令読出回路と、命令読出回路によって読み出された命令が、複数のレジスタに格納されているデータの退避を指示する命令である場合、レジスタごとにデータを所定の記憶領域に退避する命令を生成する命令生成回路と、メモリから読み出された命令、および、命令生成回路によって生成された命令を実行する命令実行回路と、を備える。

(もっと読む)

コンパクト命令セットの符号化

本発明は、プロセッサ内の命令を復号するための復号ユニットを提供する。復号ユニットは、オペレーションコード復号ロジック、オペランド復号ロジック、および16ビット入力を有する。オペレーションコード復号ロジックは、入力の5ビットを使用してオペレーションコードを決定する働きをし、オペランド復号ロジックは、入力の残りの11ビットから、可能な12個の2進値のうちの1つをそれぞれ有する3つの4ビットオペランド要素を決定する働きをする。オペランド復号ロジックは、11ビットの符号化グループを復号して3つのオペランド要素の各オペランド要素の第1の部分を決定し、11ビットの逐語的グループを逐語的に読み出して3つのオペランド要素の各オペランド要素の第2の部分を決定する働きをする。  (もっと読む)

(もっと読む)

1 - 20 / 49

[ Back to top ]