Fターム[5B033DD04]の内容

Fターム[5B033DD04]に分類される特許

1 - 20 / 60

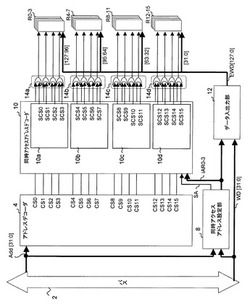

制御装置、及び制御方法

【課題】複数のレジスタへのアクセスを高速に行う。

【解決手段】制御装置は、複数のレジスタのアドレスをそれぞれ保持し、前記複数のレジスタのアドレスとは異なる第1のアドレスの指定に応答して前記複数のレジスタのアドレスを出力するアドレス設定部と、前記アドレス設定部から前記複数のレジスタのアドレスが入力され、当該複数のレジスタを選択する選択信号を同じタイミングで出力する第1のデコーダと、前記第1のアドレスに対する書込みデータを前記選択信号により選択される複数のレジスタに並行して書き込み、また、前記選択信号により選択される複数のレジスタから並行して読み出したデータを前記第1のアドレスからの読出しデータとして出力するデータ入出力部とを有する。複数のレジスタへ同時にアクセスでき、レジスタアクセスが高速化される。

(もっと読む)

スタックド・レジスタ・ファイルのレジスタ・セーブ・エンジンのためのバッキング記憶装置バッファ

【課題】スタックド・レジスタ・ファイル・システムの性能を向上させる。

【解決手段】バッキング記憶装置バッファ30は、物理レジスタファイル28と、スタックド・レジスタ・ファイル・アーキテクチャ内のバッキング記憶装置36との間に挿入される。レジスタ・セーブ・エンジンは、アクティブではないオンチップの手順に割り当てられた物理レジスタファイル内のレジスタからデータを一時的に記憶し、新たな手順に再割当されるためにレジスタをフリーにする。手順が完了し、以前のアクティブではない手順に制御を戻すと、レジスタ記憶エンジンは、アクティブではない手順に関連するデータを、バッキング記憶装置バッファから取り出し、物理レジスタファイル内のレジスタへ戻す。このレジスタは、アクティブではない手順に再割当される。

(もっと読む)

命令が利用可能な汎用レジスタの数を拡張するための上位ワード・ファシリティ

【課題】 汎用レジスタのようなアーキテクチャ・リソースへの依存を軽減し、新しい命令を用いるソフトウェア・バージョンの機能及び性能を改善する、既存のアーキテクチャと整合性が取れた新しい命令機能を提供する。

【解決手段】 コンピュータが、1組の汎用レジスタ(GPR)を利用する。各々のGPRは、複数の部分を含む。大容量GPRモードで動作するオペレーティング・システム及びアプリケーションのようなプログラムは、GPR全体にアクセスするが、小容量GPRモードで動作するアプリケーションのようなプログラムは、一度に一部分にしかアクセスすることができない。小容量GPRモードにおいて、命令オペコードは、どの部分にアクセスするかを決定することができる。

(もっと読む)

複数の命令セットにより使用されるレジスタ間のマッピング

マイクロプロセッサおよびマイクロプロセッサ上での精度が改善された積の和計算のための方法

マイクロプロセッサ(10)は、多数の行先ビットを記憶し、かつ、乗算ユニット(14)に提供するようになされた少なくとも1つの汎用レジスタ(12)と、少なくとも乗算-高位命令(20)および乗算-高位および累算命令(22)を乗算ユニットに提供するように適合された制御ユニット(18)とを備えている。乗算ユニットは、さらに、少なくとも第1および第2の原始オペランド(24、26)を受け取るようになされており、これらの原始オペランドは、それぞれ関連する数の原始ビットを有しており、かつ、該関連する数の原始ビットの和は行先ビットの数より多く、また、乗算ユニットは、多数の精度向上ビットを記憶し、かつ、提供するようになされた少なくとも1つのキャッシュエントリを備えたレジスタ拡張キャッシュ(28)に接続されており、また、結果オペランドの行先部分を汎用レジスタに記憶し、かつ、結果オペランドの精度向上部分をキャッシュエントリに記憶するように適合されている。結果オペランドは、受け取った命令に応じて、乗算-高位演算によって生成され、あるいは乗算-高位および累算演算によって生成される。  (もっと読む)

(もっと読む)

情報処理装置及びベクトル型情報処理装置

【課題】レジスタ・リネーミング機構を実装するプロセッサを備えた情報処理装置におい、プログラムを最適化するだけの手段では回避できないメモリアクセスやレジスタの解放待ち時間を回避すること。

【解決手段】レジスタ・リネーミング機構を実装すると共に、図1(a)に示すレジスタの使用状況の下で、ユーザ(プログラマ等)は、命令セットに導入した専用命令(論理レジスタに割り当てが可能な未使用の仮想レジスタの数を増加または減少させる命令)を発行し、実行させる。これにより、未使用の仮想レジスタの数を図1(b)、図1(c)に示すように変更できるので、ソフトウェアによって、それ自身のプログラム特性に最適化したレジスタの利用を図ることが可能となる。また、レジスタ上のデータをメモリへ退避するようなメモリアクセスの発生や、レジスタの解放待ち時間の発生が抑制されるので、処理性能を向上させることができるようになる。

(もっと読む)

マイクロコンピュータ

【課題】汎用レジスタの使用効率を最適化することが可能なマイクロコンピュータを提供すること。

【解決手段】制御部13は、命令コードのデコード結果に応じて、命令の実行を制御する。GRAレジスタ32は、複数の汎用レジスタのそれぞれに対するアクセス属性を記憶する。モード記憶部31は、CPUの動作を制御するためのモードを記憶する。そして、レジスタアクセス許可判定回路33は、制御部13から汎用レジスタに対してアクセス要求がある場合に、GRAレジスタ32に記憶されるアクセス属性およびモード記憶部31に記憶されるモードに応じて、当該汎用レジスタに対するアクセスを許可するか否かを判定する。したがって、モードに対応して使用される汎用レジスタの本数を変更することができ、汎用レジスタの使用効率を最適化することが可能となる。

(もっと読む)

半導体集積回路及びレジスタアドレス制御装置

【課題】既存の半導体集積回路に対して機能の追加や修正がある場合でも、当該既存の半導体集積回路で作成したソフトウェアを使用可能、かつ、CPUの性能を向上可能な半導体集積回路及びレジスタアドレス制御装置を提供すること。

【解決手段】半導体集積回路110は、モード1からモードN(120、130、140)に対応して、アドレスビットの割り当てを組み換えたレジスタマップ1〜レジスタマップN(121、131、141)を有する。各レジスタマップは、対応するモードによって選択することができ、モードを切替えることで、いずれかのレジスタマップが使用可能となる。

(もっと読む)

命令コード群の実行方法、マイクロコンピュータ及びプログラム

【課題】汎用レジスタの故障時にも、安定動作が要請される命令コード群を確実に実行する。

【解決手段】マイクロコンピュータに内蔵された汎用レジスタの故障検出の結果、故障が検出された場合に、対象とする命令コード群に含まれる各命令コードが必要とする数以上の正常な汎用レジスタを確保する。次に、前記命令コード群が格納された第1の記憶装置から命令コードを読み出し、汎用レジスタを使用する命令コードを、前記必要数確保した汎用レジスタ群を使用するよう書き換えて、第2の記憶装置に再配置(展開)する。以後、前記第2の記憶装置から前記命令コードを読み出して実行する。

(もっと読む)

情報処理装置

【課題】マイコンなどの情報処理装置のレジスタ拡張を行う場合、拡張レジスタにアクセスするには、命令コードの追加・変更やレジスタ切り替えのための操作が必要になる。

【解決手段】命令メモリ1と、データメモリ9と、命令メモリから読み出された命令に従って制御信号を生成する命令制御部4と、命令制御部による制御信号に従ってデータメモリに対してアクセスを行うロード・ストアユニット10と、命令制御部による制御信号に従って演算を行う演算器5,6と、演算器5で用いるデータを格納する標準レジスタ群7と、演算器6で用いるデータを格納する拡張レジスタ群8と、選択信号A3により標準レジスタ群7と拡張レジスタ群8とのいずれかを選択する選択手段12と、選択手段12に対し選択信号A3を出力する選択条件判定手段13とを備え、選択条件判定手段13は、装置内部の特定の状態信号に基づいて選択信号A3を生成する。

(もっと読む)

分岐予測における使用のためのマルチモードレジスタファイル

マルチスレッドシステムの各スレッドについてのマルチモードレジスタファイルが記述される。1つの実施形態では、マルチモードレジスタファイルは第1のモード内のスレッドについてのオペランドを含む。マルチモードレジスタファイルは第2のモード内のオペランドを置換する分岐予測情報をさらに含む。  (もっと読む)

(もっと読む)

単精度浮動小数点データの格納方法およびプロセサ

【課題】単精度浮動小数点データおよび倍精度浮動小数点データを扱うプロセサにおいて、新しい単精度浮動小数点データの格納方式を提案し、バイパス機能のための依存関係検出回路を構成するハードウェア量を可能な限り低減すること。

【解決手段】倍精度浮動小数点データを格納可能な大きさを有する、倍精度浮動小数点データと単精度浮動小数点データとが格納されるレジスタを備えるプロセサにおいて、単精度浮動小数点データ処理が指定された場合、前記レジスタの上位半分に入力した単精度浮動小数点データを書き込むとともに、前記レジスタの下位半分にオールゼロを書き込む、単精度浮動小数点データ格納方式。

(もっと読む)

データ処理装置

【課題】処理の高速化を図ることができるデータ処理装置を提供すること。

【解決手段】演算器と、当該演算器にて処理されるデータを格納するレジスタと、当該レジスタに格納されているデータの退避先となるキャッシュメモリよりもレジスタに対して高速にアクセス可能なレジスタキャッシュと、演算器がキャッシュメモリに対してアクセスしていないときにレジスタキャッシュに記憶されたデータをキャッシュメモリに記憶するメモリバスアービタと、レジスタに対するデータの入出力を制御する制御部と、を備え、上記レジスタキャッシュは、レジスタに格納されているデータの書き出し要求に応じて当該レジスタから出力されたデータを記憶する機能を有すると共に、レジスタへのデータの復元要求に応じてレジスタキャッシュ内に記憶されたデータのうち当該復元要求されたデータを選択してレジスタに復元する機能を有する。

(もっと読む)

パイプライン型プロセッサ

【課題】汎用レジスタの書き込み/読み出し回数の低減および消費電力の低減が可能なパイプライン型プロセッサを提供する。

【解決手段】EステージとWBステージの間に配置されたパイプラインレジスタ1、2が、保持しているデータの有効性を示すデータ有効フラグ(F1、F2)および保持しているデータの前記汎用レジスタへの書き込みを制御する書き込み制御フラグ(W1、W2)を格納する領域を有し、データ有効フラグが「有効」を示すときは、汎用レジスタ100の代わりにパイプラインレジスタ1、2を読み出すバイパス回路3を備え、書き込み制御フラグによる汎用レジスタ100への書き込み終了後も、パイプラインレジスタ1、2に保持されているデータを引き続き保持し、先行命令とデータ依存関係にある後続命令の実行時に、バイパス回路3を介してEステージへ供給する。

(もっと読む)

演算処理装置及び命令の拡張方法

【課題】本発明は、固定長のまま命令を拡張する演算処理装置を提供することを課題とする。

【解決手段】命令拡張情報を格納するXARレジスタ1を設ける。実行演算器5は、XARレジスタ1に情報を設定する命令に続く命令を、XARレジスタ1内の命令拡張情報に基づいて命令拡張する。

(もっと読む)

半導体デバイス及び半導体デバイスのレジスタの動的変更方法

【課題】半導体デバイスのレジスタの構成を動的に変更する。

【解決手段】半導体デバイス1のレジスタ100を、半導体デバイス1が使用するアドレス領域である通常エリア101と、通常エリア101のアドレスに対応する仮想アドレスを複数定義するアドレス領域である変換エリア102と、仮想アドレスのビット毎に対応する通常エリア101のアドレスとビット位置を定義したデータ列を複数含む変換テーブル103と、に分け、仮想アドレスのレジスタには、仮想アドレスに対応するデータ列のアドレスが設定され、外部から入力されたアドレス値とデータを含む命令コードに対し、アドレス値が変換エリアのアドレス領域に含まれる場合、アドレス値が示すレジスタに設定された変換テーブルのアドレスのデータ列に基づき、データをビット毎に対応する通常エリアのアドレスのビット位置に書き込む。

(もっと読む)

マイクロプロセッサおよびレジスタ退避方法

【課題】マイクロプロセッサにおいて、サブルーチンの呼び出しに伴うレジスタの退避・復元を高速に実行すると共に、プログラムの規模の増大を抑制する。

【解決手段】レジスタファイル20は、演算処理に用いるデータを格納する1以上のレジスタを備える。退避メモリ30は、レジスタから退避されたデータを格納する。退避制御部40は、サブルーチン内でのレジスタへの書き込み命令の実行時に、書き込み先のレジスタに格納されているデータを退避メモリ30に退避させる。また、退避制御部40は、サブルーチンからの復帰命令の実行時に、退避メモリ30に退避されたデータを対応するレジスタに書き戻す。

(もっと読む)

データ処理装置

【課題】メモリに格納されたリングバッファのデータ構造を持つ系列データであるリングバッファ系列データの転送を高速化することができるデータ処理装置を提供する。

【解決手段】リングバッファ系列データを格納するメモリ2と、1または複数のデータを対象として演算を行う演算器5と、前記演算器5の演算対象データまたは前記演算器5の演算結果データを格納するレジスタ8と、前記メモリ2と前記レジスタ8との間のデータ転送を制御するデータ転送制御部1とを有するデータ処理装置100であって、前記リングバッファ系列データのデータ転送に関する制御情報を格納するリングバッファ転送制御レジスタ3を有し、前記データ転送制御部1は、前記リングバッファ転送制御レジスタ3の内容に従い前記リングバッファ系列データのデータ転送を行う。

(もっと読む)

演算処理装置

【課題】複数の演算による条件コードに基づいて行われるオペランドの供給を高速化する。

【解決手段】実行ユニット群500の4つの演算ユニットにおける演算により生成された条件コードは、設定レジスタ320の書込みモードレジスタ(Reg_WRMODE)の値に従って、フラグ書込み部330によりレジスタファイル310の条件コードセットレジスタrFに書き込まれる。条件コードセットレジスタの各フラグは、設定レジスタ320のマスクレジスタ(Reg_MASK)、反転レジスタ(Reg_XOR)、比較パターンレジスタ(Reg_MATCH)および機能レジスタ(Reg_FUNC)の各値に従って、フラグ変換部340によって変換されて、変換条件コードセットrF_outとして出力される。この変換条件コードセットに基づいて、他の命令のオペランドが供給される。

(もっと読む)

選択演算を実行する方法および装置

【課題】パックドデータおよび非パックドデータに選択演算を実行する命令の提供。

【解決手段】プロセッサに結合されるメモリ中に、ソースオペランド内の第1のパックドデータと、デスティネーションオペランド内の第2のパックドデータが格納される。プロセッサは、ソースオペランドの制御ビットが「1」に設定される場合に第1のパックドデータを選択し、そのデータをデスティネーションオペランド内に格納する。制御ビットが「1」に設定されない場合、プロセッサはデスティネーションオペランド内のデータを保持する。デスティネーションオペランドの最終値がメモリ内に格納される。

(もっと読む)

1 - 20 / 60

[ Back to top ]