Fターム[5B045DD07]の内容

マルチプロセッサ (2,696) | メモリシステム、ファイル管理 (299) | アドレス変換 (16)

Fターム[5B045DD07]の下位に属するFターム

プリフィックス変換 (1)

Fターム[5B045DD07]に分類される特許

1 - 15 / 15

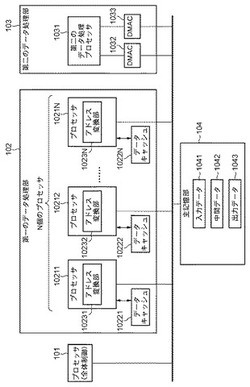

データ処理装置及びデータ処理方法

【課題】 データ処理の領域を分割して複数のプロセッサに並列処理させる際に、分割の最小単位を小さくする。

【解決手段】 データ処理装置が、第一のデータ処理を複数のプロセッサに並列処理させ、並列処理されたデータを記憶部に格納する際に、複数のプロセッサのデータキャッシュのサイズに基づいて記憶部のアドレスを変換して格納する。そして、記憶部に格納されたデータを読み出し、読み出したデータに対して第二のデータ処理を行う。

(もっと読む)

サイクリック通信同期方式

【課題】 この発明は、サイクリックメモリに書き込まれた新しい情報を、速やかに送信できるサイクリック通信同期方式を提供することである。

【解決手段】 この発明のサイクリック通信同期方式は、ネットワークを介して接続されている複数の端末間で仮想的に共有するメモリ空間を設け、それぞれの端末が予め書き込む位置を決定しておき、その領域のデータを定周期で他の端末に送信することによりネットワーク全体で共有メモリを実現するサイクリック通信同期方式であって、各端末101は、共有メモリの自端末領域201を分割した単位毎にアドレスを指定してデータを読み込みネットワークへ送信するデータ送信部200と、分割した単位毎にアドレスを指定し、該アドレスが読み込みアドレスと不一致の時にバッファメモリ400のデータを共有メモリに書き込み、該アドレスが読み込みアドレスと一致した時は書き込まない更新手段とを備えるものである。

(もっと読む)

ヘテロジニアス処理ユニット間での不均一メモリアクセスのためのチップセットサポート

【課題】第2のプロセッサに関連付けられたメモリに第1のプロセッサがアクセスすることを可能にするための方法を提供すること。

【解決手段】この方法は、第1のプロセッサから、NUMAデバイスのためのMMIOアパーチャを含む第1のアドレスマップを受け取るステップと、第2のプロセッサから、ハードウェアデバイスのためのMMIOアパーチャを含む第2のアドレスマップを受け取るステップと、第1のアドレスマップと第2のアドレスマップを組み合わせることによってグローバルアドレスマップを生成するステップと、第1のプロセッサからNUMAデバイスに送られたアクセス要求を受け取るステップと、第1のアクセス要求と変換テーブルとに基づいて、メモリアクセス要求を生成するステップと、グローバルアドレスマップに基づいて、メモリアクセス要求をメモリにルーティングするステップとを含む。

(もっと読む)

ハードウェアデバイスをヘテロジニアス処理ユニット間でバインドし移行するためのチップセットサポート

【課題】コンピュータシステム内に含まれる他のプロセッサとの競合を引き起こすことなしにハードウェアデバイスに対する、プロセッサによるアクセスを可能とする方法をていきょうすること。

【解決手段】この方法は、第1のプロセッサから第1のアドレスマップを、また第2のプロセッサから第2のアドレスマップを受け取るステップであり、各アドレスマップは、プロセッサがアクセスするように構成されているハードウェアデバイスのセットのためのメモリマップド入出力アパーチャを含む、ステップと、第1と第2のアドレスマップを組み合わせることによってグローバルアドレスマップを生成するステップと、第1のプロセッサから第1のアクセス要求を受けるステップと、グローバルアドレスマップ内に含まれるアドレスマッピングに基づきハードウェアデバイスに第1のアクセス要求をルーティングするステップとを含む。

(もっと読む)

マルチプロセッサシステム及びそれを搭載した流体吐出装置

【課題】第1制御部と第2制御部とによるコヒーレンシをより容易且つ確実に実現する。

【解決手段】マルチプロセッサシステム30は、リクエストの出力先としてDMAコントローラ35が予め対応付けられているDMAメッセージボックス37を備えており、このDMAメッセージボックス37へのリクエストをメインプロセッサ31からブリッジ32が入力すると、メモリ34に対する先のリクエストのAck信号を入力したあとリクエストをDMAメッセージボックス37へ出力し、このリクエストをDMAメッセージボックス37が対応付けられたDMAコントローラ35へ出力する。このように、複数あるプロセッサのうち、DMAコントローラ35へのリクエストは、先のリクエスト、例えばメモリ34へのデータの書込などが完了した回答を得たあとに出力される。

(もっと読む)

プロセッサ間通信システム、プロセッサ、プロセッサ間通信方法、および、通信方法

【課題】プロセッサ間通信の高速化が可能なプロセッサ間通信システムを提供する。

【解決手段】プロセッサ間通信システムは、複数のプロセッサと、複数のプロセッサのいずれかからマルチキャストパケットを受信するとそのパケットを複数のプロセッサのうちそのパケットに宛先として指定された複数のプロセッサに転送する転送装置を含む。各プロセッサは、記憶手段、記憶手段内の基準書込み位置を示す位置情報を保持する保持手段、基準書込み位置を基準にして自プロセッサ用に予め設定された書込み領域を表した調整値とデータが記載されたマルチキャストパケットを転送装置に送信する送信手段、および、送信されたマルチキャストパケットを転送装置を介して受信すると、そのパケットに記載された調整値と保持手段内の位置情報とに基づいて記憶手段における書込み位置を決定しその書込み位置にパケットに記載されたデータを格納する受信手段を含む。

(もっと読む)

情報処理装置、および情報処理方法、並びにコンピュータ・プログラム

【課題】NUMA構成を持つ情報処理装置におけるメモリアクセスコストの削減を実現する。

【解決手段】共有メモリ型マルチプロセッサシステムのアーキテクチャであるNUMA構成を持つ情報処理装置において、デバイスが接続されたノード内のシステムバス上のメモリを、デバイスのアクセスメモリとし、さらに、デバイスの接続されたシステムバス上のプロセッサを、デバイスドライバの設定プロセッサとする。本構成により、デバイス、プロセッサ、デバイスとプロセッサのアクセスメモリが同一のシステムバスに設定され、デバイス利用処理におけるメモリアクセスを1つのシステムバスを介して実行可能となり、メモリアクセスコストの削減が実現する。

(もっと読む)

コンピュータシステム

【課題】コンピュータシステムを構成するCPUや記憶装置などを異なる物理パーティションに割り当て、限られたリソースを効率良く利用する。

【解決手段】ネットワークを介して相互に接続されるCPUと記憶装置が複数の物理パーティションに割り当てられ得るシステムにおいて、CPUとネットワークの間に、物理パーティションの分割を制御するパーティション制御装置を配置する。パーティション制御装置は、CPU又は記憶装置が何れの物理パーティションに属するかを管理するパーティション番号マッピングテーブルと、CPUからのメモリアクセス要求に含まれるシステムアドレスをデコードして、要求中のシステムアドレスがアドレッシングされている記憶装置を特定するアドレスデコーダと、要求元を示す情報にパーティション制御装置を識別するIDを関係付け、システムアドレスを記憶装置内のアドレスに変換するメモリアクセス要求変換部とを有する。

(もっと読む)

マイクロコンピュータ

【課題】負荷分散のためCPU間でタスクを移行する場合の演算性能の低下を回避する。

【解決手段】マイクロコンピュータ(1)は、第1CPU(10)と、第1バス(70)と、第1メモリ(50)と、第2CPU(20)と、第2バス(80)と、第2メモリ(60)とを含む。上記第1メモリ及び上記第2メモリは、それぞれ対応する上記第1CPU及び上記第2CPUによって個別的に管理されるアドレス空間に配置される。そして、上記第1メモリ内にデータ領域を持つようにプログラムされたタスクが上記2メモリに転送されて上記第2CPUで実行される場合、上記タスクによる上記第1メモリへのアクセスが上記第2メモリへのアクセスとなるように、上記第2CPUから出力されたアドレスを変換するためのアドレス変換回路(160)を設ける。アクセスサイクル数を削減して、負荷分散のためCPU間でタスクを移行する場合の演算性能の低下を回避する。

(もっと読む)

マルチCPU装置及びそのブート処理方法

【課題】マルチCPU装置及びそのブート処理方法に関し、汎用性の高いマルチCPU構成のブート方式を可変にし、安価で汎用性の高いブート処理を可能にする。

【解決手段】CPU11,12の起動順序を含むCPUのブート方式の情報をブートパターンとして複数種類ブートパターンテーブルに格納し、ブート方式切替え設定部15により1つのブートパターンを選択してブート方式制御部14に設定し、CPUバス制御部13は該ブートパターンにより指定される起動順序で、ブートプログラムを不揮発性メモリ18から読み出すバスアクセス権をCPUに与える。アドレス変換部17はCPUから出力されるアドレス信号をブートパターンに従って不揮発性メモリのブートプログラム格納領域のアドレス信号に変換する。データ幅変換部16は不揮発性メモリから読み出したデータ信号をブートパターンに従うデータバス幅に変換してCPU11,12に出力する。

(もっと読む)

ノード間データ転送制御装置、ノード間データ転送制御方法、及びプログラム

【課題】ノード間で共有する分散共有メモリに効率的に領域を割り当てるとともに、割り当て時の効率を維持しながら割り当て解除を行う。

【解決手段】ノード番地対応手段1−Bは、メモリ番地をノード番地に変換する手段と、メモリ番地とノード番地とが対応付けられたテーブルとを備えているか、或いは、メモリ番地とノード番地を対応付ける演算に相当する手段を備えており、このテーブルを検索するか、あるいは、メモリ番地のシフトや、一部のマスク、あるいは演算といった所定の規則に基づいてメモリ番地をノード番地に変換する。ノード番地対応手段1−Bは、ローカルメモリ上に、分散共有メモリ1−C用に割り当てられたメモリ領域の一部または全部を、分散共有メモリ1−Cとしての割当を解除する場合、分散共有メモリ1−Cの領域内の初期的割り当てとは異なる番地にある領域を、先に割り当て解除することにより、ローカルメモリ領域の使用効率を高める。

(もっと読む)

アドレス変換装置及びプロセッサシステム

【課題】シングルプロセッサ用のソフトウェアを使用可能なアドレス変換装置及びプロセッサシステムを提供すること。

【解決手段】第1アドレスA1を保持する第1アドレス保持部11と、前記第1アドレスA1と異なる第2アドレスA2を保持する第2アドレス保持部12と、前記第1アドレスA1のうち、変換対象となるビットの情報Bを保持する第1対象保持部13と、第3アドレスA3と前記第1アドレスA1とを比較する比較部15と、前記比較部において前記第3アドレスA3が前記第1アドレスA1に一致する場合に、前記第3アドレスA3において、前記第1対象保持部13に保持される前記情報に相当するビットを、前記第2アドレスA2に一致するように変換して第4アドレスA4を得る変換部16とを具備する。

(もっと読む)

ノード間データ転送制御装置

【課題】 オーバヘッドが少なく、送信データ発生と並行した高速な通信が可能なノード間データ転送制御装置を提供する。

【解決手段】 分散共有メモリ1a−3−2領域は、ノード間通信路2に接続された全てのノード1a、1bでメモリ番地が同一である。ノード番地対応手段1a−6は、メモリ番地を入力されると、該メモリ番地を含むデータバッファ1a−3−2a〜nと対応づけられたノード番地を出力する。転送制御手段1a−5は、データバッファ1a−3−2a〜nに書込まれるデータと、該データが書込まれるメモリ番地とを取得し、該メモリ番地をノード番地対応手段1a−6に問い合わせてノード番地を取得し、前述のデータとメモリ番地を併せて、取得したノード番地に送信する。また、転送制御手段1a−5は、データを受信すると、該データからメモリ番地と受信データを抽出し、該メモリ番地の分散共有メモリ領域1a−3−2に、該受信データを書込む。

(もっと読む)

対称型マルチプロセッサ・フォルトトレラントコンピュータシステム

対称型マルチプロセッシング・フォルトトレラントコンピュータシステムは、対称型マルチプロセッシングコンピュータシステムにおいてメモリアクセスを制御する。これを行うために、仮想ページ構造が作成され、該仮想ページ構造は対称型マルチプロセッシングコンピュータシステム内のプロセッサに対して共有メモリへの物理ページアクセス権限を反映する。共有メモリへのアクセスは、仮想ページング構造内に反映された物理ページアクセス権限に基づいて制御されて、対称型マルチプロセッシングコンピュータシステム内のプロセッサ間で決定論的共有メモリアクセスを調整する。対称型マルチプロセッシング・フォルトトレラントコンピュータシステムは、複写又は連続再生を用いることができる。 (もっと読む)

パーティション化可能コンピュータにおけるパーティションへの資源割り振り

【課題】 パーティション化可能コンピュータシステムにおいてパーティションにコンピュータ資源を割り振る改良された技法を提供する。

【解決手段】 本発明にかかるコンピュータシステムは、複数のパーティション(504a、504b、704a、704b)にパーティション化されたパーティション化可能コンピュータシステム(100)であって、集積回路(104a、602)を備え、前記集積回路は、前記複数のパーティションの中の第1のパーティション(504a、704a)に割り振られた第1のハードウェア資源(206a、628a)と、前記複数のパーティションの中の前記第1のパーティション(504a、704a)と異なる前記複数のパーティションの中の第2のパーティション(504b、704b)に割り振られた第2のハードウェア資源(206b、628b)とを備える。

(もっと読む)

1 - 15 / 15

[ Back to top ]