Fターム[5B046BA02]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 基本設計(システム設計) (562) | アーキテクチャ設計(機能設計、論理設計) (477)

Fターム[5B046BA02]に分類される特許

1 - 20 / 477

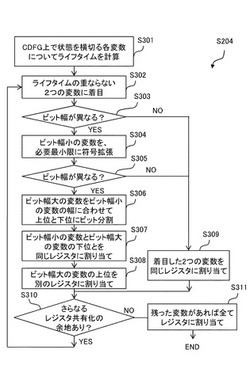

動作合成方法、動作合成プログラム及び動作合成装置

【課題】動作合成により共有化するレジスタのビット幅を小さくすることが可能な動作合成方法、動作合成プログラム及び動作合成装置を提供する。

【解決手段】動作合成方法は、動作記述情報に基づいてスケジューリングしたCDFGを生成し、スケジューリングされたCDFGに基づいてライフタイムを変数毎に生成し(S301)、ライフタイム情報が時間軸上で重ならないm個の変数を選択し(S302)、第1のビット幅の第1の変数と、その他の変数内の第1のビット幅のビットとに、第1のレジスタを割り当て(S307)、その他の変数内の第1のビット幅のビット以外のビットに、第2のレジスタを割り当て(S308)、第1及び第2のレジスタを有する合成回路の回路情報を出力する。

(もっと読む)

活動センサでデジタル回路を設計するシステム及び方法

【課題】SoC回路の場合であっても、機能記述ファイルに基づいてデジタル回路がそれ自体の出力変数(温度など)を計算できるようにする。

【解決手段】デジタル回路の機能記述を含むファイル14に基づいたデジタル回路シミュレータ12とシミュレータ12に供給されるテストベンチ26を実行する時にデジタル回路から出力変数30’を予想する手段28とイベントカウンタ34’とを含み、イベントは、テストベンチ26を実行する時にシミュレータ12によって提供された制御信号を用いて検出される。システムは、イベントカウンタからの出力データを用いてデジタル回路の出力変数30’を計算するモデルを反復して最適化することによって、イベントカウンタ34’の一部を選択する手段40、44とイベントカウンタの選択された部分及び最適化された計算モデルを登録する手段40、44とを更に含む。

(もっと読む)

回路検証装置および回路検証方法

【課題】半導体デバイスのシミュレーションに必要なパラメータを読み出すための構成を簡素化する。

【解決手段】ハードウェア記述言語に基づく論理回路が形成された半導体デバイス(102)のエミュレーションのための信号をデバイスへ入力する手段(140)と、論理回路に対応したハードウェア記述言語によりシミュレーションを実行する手段(110)と、シミュレーションに係るパラメータをデバイスから取得する手段(107)と、取得したパラメータをシミュレーションに適用する手段(111)と、パラメータ取得前に論理回路を修正する手段(130)とを備える。論理回路を修正するとき、その論理回路にてパラメータを記憶する記憶素子がリング型のシフトレジスタとして動作するためのバイパス配線(101A)と、バイパス配線を介して各記憶素子のパラメータを読み出す読出部(101B)とを付加する。

(もっと読む)

遅延ライブラリの生成方法及び遅延ライブラリ生成装置

【課題】静的タイミング解析ツールの処理結果に対する後処理時間を短くすること。

【解決手段】本発明にかかる遅延ライブラリの生成方法は、入力クロック信号を内部で分周するマクロの遅延ライブラリの生成方法であって、マクロの設計情報に基づいて、入力クロック信号を内部で分周する分周回路を抽出するステップと、抽出された分周回路が静的タイミング解析においてクロックラインの一部とみなされるように設計情報を修正する修正ステップと、修正された設計情報を用いて遅延ライブラリを生成する生成ステップと、を有する。

(もっと読む)

半導体装置および半導体装置の制御方法並びに半導体装置の設計支援方法

【課題】本発明の課題は、組み込みシステムのアーキテクチャに左右されることなく、DVFSの実行に必要なサイクル数を容易に取得することである。

【解決手段】ファームウェア(21)は、サイクル数概算ルーチン(213)と、動作電圧・周波数算出ルーチン(213)とを有する。サイクル数概算ルーチンは、サイクル数概算関数を備える。サイクル数概算関数は、ユーザ回路(6)の処理内容を決定づける属性パラメータの入力でタスクのサイクル数を概算する。動作電圧・周波数算出ルーチンは、サイクル数概算ルーチンの実行によって得られたサイクル数に基づいて、ユーザ回路(6)の目標動作電圧・周波数を算出する。

(もっと読む)

論理シミュレーション装置および論理シミュレーション方法

【課題】トランスポートモデルを用いた論理シミュレータにおいて、スパイクの影響を論理動作の結果から確認できるようにする。

【解決手段】この論理シミュレーション装置では、2つの標準遅延フォーマット(SDF)ファイルを用いて論理シミュレーションを実行し、その結果を比較することにより、スパイクが被シミュレーション回路に及ぼす影響を確認することができる。一方のSDFファイルは、被シミュレーション回路を構成する論理ゲートと配線の理想的な遅延時間情報を記述したものである。そして、他方のSDFファイルは、論理ゲートの立ち上がりおよび立ち下がりの遅延時間が、互いに同一の値に設定されており、配線の立ち上がりおよび立ち下がりの遅延時間が、互いに同一の値に設定されている。すなわち、スパイクのパルス幅が変化したり、スパイク自体が消滅したりしないように設定されている。

(もっと読む)

シミュレーション装置及びシミュレーション方法

【課題】処理負担を軽減させることができるシミュレーション装置及びシミュレーション方法を提供する。

【解決手段】シミュレーション装置のコンピュータ11は、メモリ111と、遅延除去部112と、波形比較部113と、を備える。メモリ111は、対象回路を構成する素子の遅延情報を格納する。遅延除去部112は、素子による遅延を考慮した対象回路のシミュレーション結果である遅延シミュレーション波形から、遅延情報に基づいて、素子による遅延を除去した遅延除去済み波形を生成する。波形比較部113は、遅延除去済み波形と、素子による遅延を考慮しない対象回路のシミュレーション結果である無遅延シミュレーション波形と、を比較し、比較結果を出力する。

(もっと読む)

協調検証方法及び協調検証装置

【課題】 本発明の課題は、設計回路が性能要件を満たしているか否かを判定することを目的とする。

【解決手段】 上記課題は、コンピュータによって実行される設計回路のソフトウェア及びハードウェアによる協調検証方法であって、前記設計回路の協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行うことにより達成される。

(もっと読む)

データフロー検証支援装置およびデータフロー検証支援方法

【課題】所定のデータフローについてシミュレーションを実施したかどうかを自動的に確認する。

【解決手段】プログラミング言語やハードウェア記述言語等により記述されたシステムの動作検証を支援する装置であって、前記システムの構造を表現するためのブロック図を作成してブロック図情報を生成するブロック図作成手段と、前記ブロック図に対して前記システムにおけるデータの流れる経路を示すデータフローの表記を受け付け、データフロー情報を生成するデータフロー表記手段と、入力パターンに基づいて前記システムの動作をシミュレーションしてシミュレーション結果情報を生成するシミュレーション手段と、前記データフロー情報のデータフローの示す経路が前記シミュレーション結果情報の示す経路と同じであるかをチェックするデータフローチェック手段とを備える。

(もっと読む)

シミュレーション装置、シミュレーション方法、及びプログラム

【課題】IOレジスタを用いた周辺機器の呼び出しに対応し、シミュレーション速度を向上させたシミュレーション装置、シミュレーション方法、及びプログラムを提供すること

【解決手段】CPUシミュレーション部20は、CPUを模擬してシミュレーションを実行する。周辺機器シミュレーション部50は、IOレジスタへのアクセスにより動作させる周辺機器を模擬してシミュレーションを実行する1つ以上のコンポーネント(タイマシミュレーション部51等)を備える。検出部60は、シミュレーション実行時に前記周辺機器に対応するIOレジスタへのアクセスを検出する。接続管理部70は、検出部60の検出結果に応じてシミュレーション実行時に動作させるコンポーネントを設定する。

(もっと読む)

モデル変換装置、モデル変換方法、およびプログラム

【課題】煩雑な手間や時間をかけることなく、シミュレーション用インターフェースモデルと動作合成用インターフェースモデルとを等価性を保ったまま相互に変換することが可能なモデル変換装置、モデル変換方法、およびプログラムを提供する。

【解決手段】固定された記述スタイルのシミュレーション用インターフェースモデルおよび固定された記述スタイルの動作合成用インターフェースモデルの各代数表現を変形し変形後の代数表現の双方が一致すれば数学的にモデルに等価性があるとして、モデルの相互変換を行う処理部を有し、処理部は、代数的に等価性を保つ以下の3つの操作a,b,cによる階層チャネルおよび集約チャネルモデル変換の相互等価変換を行う。a:ペイロード公開、およびペイロード隠蔽操作の相互等価変換、b:インターフェースおよびチャネル分解、およびインターフェースおよびチャネル集約、c:プロセスリマッピング操作。

(もっと読む)

ソフトウェアシミュレーション装置、シミュレーション方法、及びプログラム

【課題】不定値を適切に扱うことができるソフトウェアシミュレーションを実現するシミュレーション装置、シミュレーション方法、及びプログラムを提供すること

【解決手段】所定回路シミュレータ90は、所定の回路(たとえばフリップフロップ回路、メモリ回路)の動作を模擬(シミュレーション)する。不定値変換手段30は、所定回路シミュレータ90からの出力が不定値である場合に"0"または"1"に変換して後段のシミュレータに出力する。

(もっと読む)

消費電力解析装置及び方法

【課題】 本発明の課題は、組み合せ回路を含めた電力解析を効率的かつ高速に行うことを目的とする。

【解決手段】 上記課題は、回路の動作記述の抽象度が異なる概要回路モデルと、該概要回路モデルより抽象度が低い詳細回路モデルとを含む回路データと、該回路の電力検証方法に係る動作シーケンス・データとを記憶する記憶部と、論理回路の動作シミュレーションを行う論理シミュレーション部に、前記前記概要回路モデルと前記詳細回路モデルとを含む前記回路データをロードし、該記憶部に記憶されている前記動作シーケンス・データに従って、該概要回路モデルによって前記動作シミュレーションを行わせる概要モードと、該詳細回路モデルによって該動作シミュレーションを行わせる詳細モードとを切り替えて、該論理シミュレーション部に該動作シミュレーションを行わせるシミュレーション制御部とを有することを特徴とする消費電力解析装置により達成される。

(もっと読む)

オープンソースソフトウェアを利用したハードウェア・ソフトウェア協調検証方法

【課題】 初期導入コストを安く抑えたハードウェアエミュレータを提供し、ハードウェアモデルとハードウェアエミュレータとを容易に接続する技術を提供することを目的とする。

【解決手段】 オープンソースソフトウェアを利用したハードウェア・ソフトウェア協調検証方法であって、オープンソースソフトウェアであるQemuを改変することにより、Qemuとハードウェアモデルの接続するTLMインターフェースを介して、ハードウェアモデルに対してデータI/Oを行う手段と、ハードウェアモデルをQemu上でエミュレートしているPCIバスに接続されているPCIデバイスとして見せる手段と、SystemCシミュレータからQemuを起動する手段とを備えたオープンソースソフトウェアのPCエミュレータを実現する。

(もっと読む)

言語変換処理方法及び言語変換処理プログラム

【課題】プログラム記述言語によるハードウェアのアルゴリズム記述をベースに高位合成のためのハードウェアモデルの設計工数を短縮する。

【解決手段】並行処理及び時間の概念を持たないプログラム記述言語を用いてハードウェアのアルゴリズムを記述したアルゴリズム記述のデータを並行処理及び時間の概念を持つシステムレベル記述によるハードウェアモデルのデータに変換するとき、アルゴリズム記述に含まれるハードウェア要素としてのパラメータについてのアルゴリズム記述上でのデータの依存関係をシステムレベル記述において維持するデータ依存関係維持記述を生成する。アルゴリズム記述からシステムレベル記述に変換されたハードウェアモデルには、アルゴリズム記述に対して既に評価及び検証された結果が反映されることになり、変換されたハードウェアモデルに対して、使用言語が相違されていても、重ねて評価検証を行うことを要しない。

(もっと読む)

ネットリスト変換装置、論理合成装置及びコンピュータプログラム

【課題】半導体集積回路の開発期間を短縮し、且つ、レイアウトエラー確率を低減する。

【解決手段】本発明の実施形態のネットリスト変換装置は、半導体集積回路を構成する複数のセルであって、第1遅延時間だけスキャン用データ信号を遅延させる第1スキャンフリップフロップを含む複数のセルの接続関係を示すネットリストを変換する。そのようなネットリスト変換装置は、論理ライブラリ30と、ネットリスト変換部18と、を備える。論理ライブラリ30は、半導体集積回路を構成する複数のセルの論理的機能を示す情報を含むセル論理情報であって、第1スキャンフリップフロップの論理的機能を示す情報と、第1遅延時間より大きいスキャン用第2遅延時間だけデータ信号を遅延させる第2スキャンフリップフロップの論理的機能を示す情報と、を含むセル論理情報を記憶する。ネットリスト変換部18は、セル論理情報を参照して、ネットリストの第1スキャンフリップフロップを第2スキャンフリップフロップに置換する。

(もっと読む)

検証装置、検証プログラム、および、検証方法

【課題】非同期回路の活性化回数を選択的に測定して検証時間を短縮する。

【解決手段】検証装置1は、検証対象2から非同期パスの構造タイプを抽出する抽出部1aと、抽出した非同期パスの構造タイプに基づいて、検証対象2に対する第1および第2の測定箇所を含む複数の測定箇所を特定する特定部1bと、特定した第1および第2の測定箇所間の信号伝播所要サイクル数を検証対象2から検出する検出部1cと、検出した信号伝播所要サイクル数を用いて、特定した複数の測定箇所の活性化回数を所定のタイミングで測定するアサーションを生成するアサーション生成部1dと、非同期シミュレーションの実行中、生成したアサーションを用いて、特定した複数の測定箇所の活性化回数を測定する測定部1eと、測定結果を期待値と比較する比較部1fと、を有する。

(もっと読む)

検証装置、検証方法及び検証プログラム

【課題】動作記述と抽象インタフェイスの組み合わせによって起こり得る設計間違いを効率的に検出することができる検証装置、検証方法及び検証プログラムを提供する。

【解決手段】検証装置100の入力手段101は、動作記述と、抽象インタフェイスが正常に動作するための条件を記述した第1のプロパティであって、抽象インタフェイスに対応して予め用意された前記第1のプロパティとの入力を受ける。動作合成手段102は、動作記述をRTL記述に変換する。対応関係記述生成手段103は、動作記述とRTL記述との対応関係を記述した対応関係記述を生成する。プロパティ変換手段104は、第1のプロパティを、対応関係記述に従って第2のプロパティに変換する。プロパティ検証手段105は、第2のプロパティに基づき、RTL記述が正常に動作するか否かを検証する

(もっと読む)

回路生成装置

【課題】誤接続や未接続のないRTLを生成することが可能な回路生成装置を提供すること。

【解決手段】RTLファイル25は、複数のモジュールの回路記述を格納する。RTL読み込み部22は、上位のRTLで使用されるモジュール名およびそのモジュール数が記述されたパラメータ21を参照して、RTLファイル25から該当するモジュールのRTLを読み込む。端子名抽出部23は、RTL読み込み部22によって読み込まれたモジュールのRTLから端子名を抽出する。そして、RTL生成部24は、端子名抽出部23によって抽出された端子名に該当する端子属性情報を参照して、上位のRTLで使用されるモジュールを接続して上位のRTLを生成する。したがって、誤接続や未接続のないRTLを生成することが可能となる。

(もっと読む)

ハイブリッドシステムの検証方法、検証装置、及び検証コンピュータプログラム、並びに、ハイブリッドシステムのモデル変換方法、変換装置、及び変換コンピュータプログラム

【課題】ハイブリッドシステムの検証を、ソフトウェア検証の手法で行えるようにする。

【解決手段】 連続値と離散値とが相互に影響を与えながら動作するハイブリッドシステムの検証方法であって、前記ハイブリッドシステムの動作を、プログラミング言語によってコーディングしたモデルを作成する作成ステップと、モデルのコードを、形式的検証を行うプログラム検証器45によって検証することで、ハイブリッドシステムの検証を行う検証ステップと、を含んでいる。プログラミング言語は、無限小を記述可能なプログラミング言語である。モデルは、ハイブリッドシステムにおける連続値の変化が、前記無限小を用いてコーディングされている。

(もっと読む)

1 - 20 / 477

[ Back to top ]