Fターム[5B047EA09]の内容

Fターム[5B047EA09]に分類される特許

1 - 20 / 129

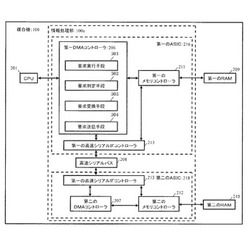

情報処理装置及び情報処理方法

【課題】シリアルバスを介してデータが転送される場合であっても、メモリを増加することなく、レイテンシの発生を防止することが可能な情報処理部100aを提供する。

【解決手段】前記CPU201からの要求が、前記第一のDMAコントローラ206に前記第二のRAM210のデータを読み取らせて前記第一のRAM209に書き込ませる間接リード要求であるか否かを判定する要求判定手段302と、前記要求が前記間接リード要求である場合に、当該間接リード要求を、前記第二のDMAコントローラ207に前記第二のRAM210のデータを前記第一のRAM209に書き込ませる直接ライト要求に変換する要求変換手段303と、前記直接ライト要求を前記第二のDMAコントローラ207に送信する要求送信手段304とを備える情報処理部100aを提供する。

(もっと読む)

画像回転装置及び画像形成装置

【課題】画像の回転に利用される記憶部の容量を小さく抑えることが可能な画像回転装置及び画像形成装置を提供する。

【解決手段】画像回転装置1は、画像データの書込み方向と画像データの読み出し方向が同一の方向であり、且つ、第1方向における所定のバースト長に対応する画素数と、第1方向に直交する第2方向の画素数とが同一である第1記憶部11と、第3方向の画素数が第1記憶部11における第1方向の画素数と同一であると共に、第3方向に直交する第4方向の画素数が第1記憶部11における第2方向の画素数よりも少ない第2記憶部12と、第1記憶部11に記憶される画像データを所定のバースト長に対応する画素数のデータ毎に読み出して第2記憶部12に書き込むことと、第2記憶部12に記憶されるデータを所定のバースト長に対応する画素数のデータ毎に読み出して第1記憶部11に書き込むことと、を行う読出書込部20と、を備える。

(もっと読む)

画像変形装置および命令付加装置

【課題】キャッシュミスのないアクセスを可能にする。

【解決手段】画像変形装置10は、画像を格納するフレームメモリ12と、フレームメモリ12に格納された画像に施す変形処理パラメータP1にプリフェッチ命令P2が付加されたプリフェッチ命令付変形処理パラメータP3を格納するパラメータメモリ13と、フレームメモリ12に格納された画像の画素データの一部を一時的に格納することで、フレームメモリ12からの画素データ読み込み効率を向上させるキャッシュメモリ14と、パラメータメモリ13に格納されたプリフェッチ命令P2に従ってフレームメモリ12からキャッシュメモリ14に画素データをロードするプリフェッチ制御部15と、パラメータメモリ13に格納された変形処理パラメータP1を使用してキャッシュメモリ14に格納された画像に変形処理を施す変形処理部16とを備える。

(もっと読む)

データ処理装置

【課題】分割ブロック毎の処理に必要なデータが、データ転送の切れ目をまたいでいる場合でも、バッファの記憶容量を増大させることなく、各ブロックの処理間のロス時間を低減することができるデータ処理装置を提供する。

【解決手段】予め定められたデータ取得単位毎にデータを取得するデータ取得部と、1つのデータ取得単位よりも少ない記憶容量の複数の分割バッファを具備し、合計の記憶容量が2つのデータ取得単位以上であるバッファ部と、データが有効であるか否かの有効データ情報を出力する有効データ領域判定部と、分割バッファにデータが格納されているか否かの管理情報を出力するバッファ状態管理部と、管理情報に基づいて、少なくとも有効データ情報に示された有効なデータを含む、分割バッファの記憶容量の単位のデータを分割バッファに書き込むデータ書き込み制御部と、管理情報に基づいて有効なデータを読み出すデータ読み出し制御部とを備える。

(もっと読む)

データ形式変換方法、集積装置

【課題】回路規模と性能のトレードオフをより高次元に両立するデータ形式変換方法を提供すること。

【解決手段】処理回数をs、ラインの一方をH、他方をL、HとLの2つの記憶装置を1カラムとしてカラムの端から各カラムの番号をkとし、各記憶装置をH[k],L[k]で表す場合、s回目の処理では、L[s-1]とH[n/2-s]内のデータはカラム方向へ(S1,S3)、L[s]乃至L[n/2-s]及びH[s-1]乃至H[n/2-s-1]内のデータはライン方向へ移動し(S4)、その他の記憶装置はデータ移動を行わず(S5)、L[k]内のデータがライン方向へ移動する場合はL[k-1]へ、カラム方向へ移動する場合はH[k]へ移動し、H[k]内のデータがライン方向へ移動する場合はH[k+1]へ、カラム方向へ移動する場合はL[k]へ移動し、処理数がn/4になるまで前記s回目の処理を繰り返す、ことを特徴とする。

(もっと読む)

データ転送制御装置

【課題】データ転送量とメモリ使用量の削減、及び画像処理装置における負荷を軽減してシステム全体の処理スループットの向上を実現できるデータ転送制御装置を提供すること。

【解決手段】データ転送制御装置400は、転送制御部401で受信された画像データを記憶するデータ記憶部402と、設定部200によって設定されたデータ処理の内容に従って、データ記憶部402に記憶された前記画像データに対して演算を施すデータ演算部4032と、データ演算部4032で演算された画像データを転送制御部404に出力するように制御するか、データ記憶部402に帰還させるように制御する内部制御部4033とを備える。データ記憶部402に画像データが帰還された場合、データ演算部4032は、データ記憶部402に帰還された画像データに対してさらに演算を施す。

(もっと読む)

画像処理装置及び画像処理システム

【課題】キャッシュメモリの利用効率及び外部メモリへのアクセスレイテンシを改善する。

【解決手段】画像処理装置10は、外部メモリ30及びキャッシュメモリ20に接続される。画像処理装置10は、カウンタ11と、座標計算部12と、タグチェッカ13と、画素参照部15と、画素値計算部16と、出力部17と、を備える。カウンタ11は、所定の実行順に従って変換後座標を決定する。座標計算部12は、変換後座標に位置する変換後画素の変換後画素値を計算するための変換前座標を計算する。タグチェッカ13は、変換前画素を参照して変換後画素値を計算することを要求する変換要求を生成する。画素参照部15は、変換要求に基づいて、変換前座標に位置する変換前画素がキャッシュメモリ20に記憶されている場合に、変換前画素をキャッシュメモリ20から読み出す。画素値計算部16は、読み出された変換前画素を参照して、変換後画素値を計算する。出力部17は、変換後画素を外部メモリ30に書き込む。

(もっと読む)

画像処理装置及びその制御方法

【課題】ダイレクトメモリアクセスを用いてメモリから画像処理モジュールへデータを転送するにおいて、メモリに要求される容量と転送帯域を小さくする。

【解決手段】

画像処理装置は、自身に設定された設定値に応じて画像データを処理する複数の画像処理部を有する。画像処理装置は、この画像処理部で処理される画像データおよび当該画像データの処理に用いる設定値を第1のアドレス空間に格納し、ダイレクトメモリアクセスにより、第1のアドレス空間から読み出した設定値および画像データのそれぞれを画像処理部に伝達するためのヘッダ情報と対応づけてコマンドとして画像処理部へ転送する。また、画像処理装置は、画像処理部から出力された処理済のコマンドからその画像処理部によって処理された画像データを抽出し、抽出した画像データをダイレクトメモリアクセスにより第2のアドレス空間へ転送する。

(もっと読む)

スキャナ装置

【課題】 RAMの記憶容量が比較的に少ない場合でも、ハッシュ値を迅速に算出し得る技術を提供すること。

【解決手段】 多機能機は、1枚のスキャン対象物を表わす画像データを構成する複数個の部分画像データ112c,114c,116cを、RAM26内に順次生成する。また、多機能機は、各部分画像データ112c,114c,116cの高さ情報を、RAM26内に順次生成する。即ち、多機能機は、各部分JPEGデータ112,114,116を、RAM26内に順次生成する。多機能機は、各部分JPEGデータ112,114,116を順次用いて、最終ハッシュ値を算出するための算出処理を順次実行する。さらに、多機能機は、各部分JPEGデータ112,114,116を、USBメモリ内に順次書き込む。

(もっと読む)

ビット並べ替え回路およびそれを用いた試験装置

【課題】データビットの並べ替え回路の小型化および/または低消費電力化にある。

【解決手段】入力フリップフロップ10は、(m×n)ビットを単位とする入力データDINのうち、連続するmビットを含むワードデータDWDを順次保持する。複数のデコーダ回路DEC1〜mは、ワードデータDWDの各ビットごとに設けられ、それぞれがワードデータの対応するビットおよびその並べ替え後の位置を示す格納先データを受け、(m×n)ビットを有するデコードデータDDECを生成する。デコードデータDDECは、対応するビットが0のとき全ビットが0、対応するビットが1のとき、その並べ替え後の位置に対応するビットが1、残りのビットが0である。メモリ回路20は、(m×n)ビットの記憶領域を含み、m個のデコードデータDDEC1〜mを受け、各デコードデータの1が格納されているビットに対応する記憶領域のビットに1を書き込む。

(もっと読む)

汎用使用のための処理ユニット内部メモリ

【解決手段】

汎用使用のための内部メモリを有するグラフィクス処理ユニット(GPU)及びそのアプリケーションがここに開示される。そのようなGPUは、第1の内部メモリと、第1の内部メモリに結合される実行ユニットと、第1の内部メモリを他の処理ユニットの第2の内部メモリに結合するように構成されるインタフェースと、を含む。第1の内部メモリは積層ダイナミックランダムアクセスメモリ(DRAM)又は埋め込みDRAMを備えていてよい。インタフェースは第1の内部メモリをディスプレイデバイスに結合するように更に構成されていてよい。GPUは第1の内部メモリを中央処理ユニットに結合するように構成される別のインタフェースを含んでいてもよい。またGPUはソフトウエアにおいて具現化され且つ/又はコンピューティングシステム内に含まれていてよい。

(もっと読む)

画像処理ボード、画像処理装置、及び画像処理方法

【課題】傾いた状態で検査対象物をカメラで撮像したとしても、リアルタイムで検査対象物の傾きを補正することができる画像処理ボードを提供する。

【解決手段】画像処理ボード104は、ラインセンサカメラ(不図示)で検査対象物の画像を取り込む画像取込処理を実行する画像取込部161と、検査対象物の傾きを正す方向に回転するように、検査対象物の画像を補正する画像補正処理を実行する画像補正部162と、補正後の画像をメインメモリ(不図示)に転送する画像転送処理を実行する画像転送部163と、撮像命令をCPU(不図示)から受けると、画像取込部161に画像取込処理を実行させて、補正開始ライン数以上のラインを取り込むと、画像取込処理に並行して、画像補正部162に画像補正処理を実行させて、転送開始ライン数以上のラインを取り込むと、画像取込処理に並行して、画像転送部163に画像転送処理を実行させる制御部160とを備える。

(もっと読む)

画像処理装置

【課題】パターンメモリとして安価なメモリを使用する場合でも、効率的にパターンメモリからデータを読み出して処理を行うことができる画像処理装置を提供する。

【解決手段】キャッシュ制御回路52は、キャッシュメモリ51内のデータを対象とするリードリクエストが与えられた場合には、そのリードリクエストの対象であるデータをキャッシュメモリ51から読み出して出力し、キャッシュメモリ51に格納されていないデータを対象とするリードリクエストが与えられた場合には、当該データを含む1ページ分のデータをパターンROM204から読み出して、キャッシュメモリ51内の書き換え対象の記憶エリアに格納する。その際、リードリクエストの対象であるデータに連続するデータがキャッシュメモリ51内に格納されている場合に、その連続するデータが格納された記憶エリアを書き換え対象とする。

(もっと読む)

画像取得装置

【課題】標本とセンサーとの間にレンズ系を配置しているため、画像取得装置が大型化し高価になっていたため、レンズ系を使用しないで小型で安価な画像取得装置を提供する。

【解決手段】標本11を載置するステージ12と、前記標本に対向する位置の近傍に配置され前記標本からの光をレンズを介さずに前記標本の画像を撮像する撮像素子18と、前記ステージと前記撮像素子の少なくとも一方を移動する移動手段14と、前記撮像素子の画像信号から前記標本の画像を形成する画像生成手段と、を有する画像取得装置1。

(もっと読む)

データ入出力制御装置

【課題】機器全体にかかるコストを低減させ、記憶装置に格納された画素に対し効率よくアクセスできるデータ入出力制御装置を提供する。

【解決手段】本発明のメモリコントローラ3は、原画像を回転させて入出力させるか否かを判定するアドレス変換指示部34と、回転後の画像を構成する各画素データの原画像メモリ2におけるアドレスを求めるアドレス変換部35と、ラスタスキャン方式の走査順に、画素データを、原画像メモリ2からデータバス6を通じて出力させるデータ入出力部31とを備え、原画像を回転させずに入出力させる場合、データ入出力部31は、原画像メモリ2から、データバス6のバス幅に応じた個数ずつ画素データを入出力し、原画像を回転させて入出力させる場合、この回転角度と求めたアドレスとに基づき、回転後の画像の画素データを走査順にアクセスし、データバスのバス幅に応じた個数ずつ入出力する。

(もっと読む)

画像データ検査装置

【課題】画像データ要求コマンドなしに自動でデータ処理部から操作表示部への画像データ転送を実現し、かつ、画像データの取得機能をもつ手段と画像データの転送機能をもつ手段間で画像データに対する排他区間を確保して画像データへの同時アクセスを回避すること。

【解決手段】画像処理通信手段12は、画像データ管理インデックス記憶手段157の画像データ管理インデックスを読み込み、その値に1加えた値を欠陥画像データのファイル名に付加し、そのファイル名で画像データ記憶手段16に保管し、画像データ管理インデックスを+1する。操作表示通信手段13は、画像データ管理インデックス記憶手段157の画像データ管理インデックスを読み込み、その値以下の値をファイル名にもつ欠陥画像データのファイルを操作表示部3に転送する。

(もっと読む)

画像処理装置および画像処理方法

【課題】デバイスドライバからアプリケーションプログラムへの不要な通知を減らすことにより、性能の低下を防ぐことを可能とする。

【解決手段】複数の入力側のディスクリプタ情報を参照してDMA読み出しする入力側DMAC161と、DMA読み出しされた複数のブロックに回転処理を実施する回転処理部162aと、複数の出力側ディスクリプタ情報を参照してDMA書き込みする出力側DMAC163と、を含むASIC16を備え、各ディスクリプタ情報は、当該ディスクリプタ情報を参照して行われたDMA読み出しまたはDMA書き込みが完了したことを表す信号がASIC16からデバイスドライバに出力されたときに、そのことをデバイスドライバプログラムからアプリケーションプログラムへ通知することが必要であるか否かを表す情報を含むテンポラリ領域を有する。

(もっと読む)

画像処理装置および表示用画像メモリアクセス方法

【課題】画像データおよび文字データの表示用画像メモリへの書込みおよび読出しの高速化および効率化を図る。

【解決手段】CPUと表示用画像メモリ・インタフェースの間に書込み用FIFOを設け、該CPUは該書込み用FIFOに画像データ、文字データまたは文字データ読出しコマンドを書込む。表示用画像メモリ・インタフェースは、該書込み用FIFOに蓄積されているデータ等を読んで、表示用画像メモリからの画像データ若しくは文字データのバースト読出し、画像データ若しくは文字データの表示用画像メモリへのバースト書込みまたは編集のための表示用画像メモリからの文字データ読出しを調停する機能を備える。

(もっと読む)

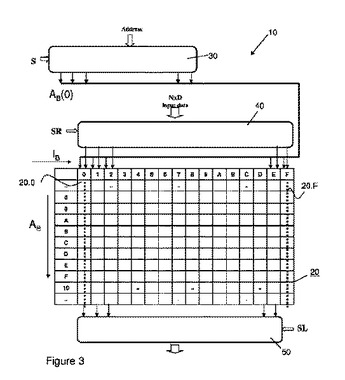

マルチモードアクセス可能な記憶装置

ブロックアクセスモードでのブロックアクセスおよび行アクセスモードでの行アクセスを可能にするマルチモードアクセス可能な記憶装置(10)を開示する。記憶装置は、各々がそれぞれのバンクインデックス(0、…、F)を有する複数のメモリバンク(20.0、…、20.F)を備えるメモリユニット(20)と、前記メモリバンクの各々について入力アドレスおよびシフトパラメータの関数として回転されたバンクアドレスを生成するアドレス発生器(30)と、入力ベクトルを回転させ、回転された入力ベクトルのベクトル要素をメモリユニットのそれぞれのバンクに供給する入力ベクトルデータ回転器(40)と、メモリユニットのそれぞれのバンクから取得されるベクトル要素を含むベクトルを逆回転させ、回転した出力ベクトルを供給する出力ベクトル回転器(50)と、を備える。  (もっと読む)

(もっと読む)

メモリ制御装置およびカメラシステム

【課題】カメラシステムにおいてアクセス先アドレスが頻繁に切り替わるデータの処理に関しては、データの先読み機能が有効に発揮されない。最小限のメモリ追加によるシステム構成で、アクセスアドレスを随時切り替える必要のある特定のアクセスパターンにおいても、高速なアクセスを実現し、高いアクセス効率を確保する。

【解決手段】メモリ制御部7が外部メモリ30にアクセスする際のアドレスを取得するアドレス取得手段10と、順次取得されるアドレスの差分情報を一時記憶するアドレスメモリ部11と、差分情報を基に順次アクセスのアドレスが一定周期をもつかを認識する周期認識手段12と、一定周期の連続回数が閾値を超えるか否かを判定する一定周期判定手段14とを備える。メモリ制御部7は、一定周期の連続回数が閾値を超えると判定されたときに先読み機能をアクティブにし、次回アクセスが予想されるアドレスに従って外部メモリに対し先読みのアクセスを行って、その先読みデータをバッファ部9にバッファリングする。

(もっと読む)

1 - 20 / 129

[ Back to top ]