Fターム[5B047EB02]の内容

Fターム[5B047EB02]に分類される特許

1 - 20 / 51

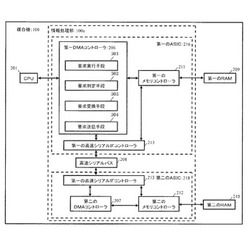

情報処理装置及び情報処理方法

【課題】シリアルバスを介してデータが転送される場合であっても、メモリを増加することなく、レイテンシの発生を防止することが可能な情報処理部100aを提供する。

【解決手段】前記CPU201からの要求が、前記第一のDMAコントローラ206に前記第二のRAM210のデータを読み取らせて前記第一のRAM209に書き込ませる間接リード要求であるか否かを判定する要求判定手段302と、前記要求が前記間接リード要求である場合に、当該間接リード要求を、前記第二のDMAコントローラ207に前記第二のRAM210のデータを前記第一のRAM209に書き込ませる直接ライト要求に変換する要求変換手段303と、前記直接ライト要求を前記第二のDMAコントローラ207に送信する要求送信手段304とを備える情報処理部100aを提供する。

(もっと読む)

画像処理装置および画像処理プログラム

【課題】並列処理される画像処理の一部をハードウェア処理する複数のアクセラレータを用いて画像処理を行う際に、複数設けられたアクセラレータの利用効率を向上させる。

【解決手段】DMAバッファ50の実アドレスを連続した論理アドレス空間上の共通バッファ領域70にマッピングし、RIP処理部90は共通バッファ70にて空いたDMAバッファをDMA転送制御ライブラリ30に問い合わせて獲得し、任意のアクセラレータ80に処理を引き継ぐ中間データを書き込み続く処理をデバイス選択部20に要求する。デバイス選択部20は、RIP処理部90から通知される論理DMAバッファ33の共通バッファ領域70におけるオフセットを任意の空いているアクセラレータ80を制御するドライバ60に通知してアクセラレータ80に対する中間データのDMA転送および転送した中間データの処理を指示する。

(もっと読む)

画像回転装置及び画像形成装置

【課題】画像の回転に利用される記憶部の容量を小さく抑えることが可能な画像回転装置及び画像形成装置を提供する。

【解決手段】画像回転装置1は、画像データの書込み方向と画像データの読み出し方向が同一の方向であり、且つ、第1方向における所定のバースト長に対応する画素数と、第1方向に直交する第2方向の画素数とが同一である第1記憶部11と、第3方向の画素数が第1記憶部11における第1方向の画素数と同一であると共に、第3方向に直交する第4方向の画素数が第1記憶部11における第2方向の画素数よりも少ない第2記憶部12と、第1記憶部11に記憶される画像データを所定のバースト長に対応する画素数のデータ毎に読み出して第2記憶部12に書き込むことと、第2記憶部12に記憶されるデータを所定のバースト長に対応する画素数のデータ毎に読み出して第1記憶部11に書き込むことと、を行う読出書込部20と、を備える。

(もっと読む)

データ形式変換方法、集積装置

【課題】回路規模と性能のトレードオフをより高次元に両立するデータ形式変換方法を提供すること。

【解決手段】処理回数をs、ラインの一方をH、他方をL、HとLの2つの記憶装置を1カラムとしてカラムの端から各カラムの番号をkとし、各記憶装置をH[k],L[k]で表す場合、s回目の処理では、L[s-1]とH[n/2-s]内のデータはカラム方向へ(S1,S3)、L[s]乃至L[n/2-s]及びH[s-1]乃至H[n/2-s-1]内のデータはライン方向へ移動し(S4)、その他の記憶装置はデータ移動を行わず(S5)、L[k]内のデータがライン方向へ移動する場合はL[k-1]へ、カラム方向へ移動する場合はH[k]へ移動し、H[k]内のデータがライン方向へ移動する場合はH[k+1]へ、カラム方向へ移動する場合はL[k]へ移動し、処理数がn/4になるまで前記s回目の処理を繰り返す、ことを特徴とする。

(もっと読む)

画像形成装置およびその制御方法

【課題】画像形成手段(プロッタ)に不正な画像データが転送されるのを防止する。

【解決手段】出力バッファ(24b)にバッファ容量分の画像データが記憶されたことを通知するバッファフル通知部24eと、出力バッファ(24b)に記憶されている画像データの出力バッファ(32a)への読み出し命令が発生し、且つ、バッファフル通知部24eからの通知があった場合に、出力バッファ(24b)に記憶されている画像データを汎用バスB2を介して取得して出力バッファ(32a)に記憶するリード制御部32dとを備える。

(もっと読む)

多次元データをデータ競合なしで同時検索するための処理システム、データ構造およびデータ処理方法

【課題】多次元データをデータ競合なしで同時検索する。

【解決手段】1個のデータポートを有する単一の方形データアレイは、多次元ピクセルアレイを表すデータ要素セットを記憶できる。ロード/記憶ユニットはデータ要素セットを受取り、各別のアドレスポートを有する複数の個別アドレス指定可能データアレイの間で分割記憶できる。個別アドレス指定可能データアレイは、ピクセルアレイの多次元サブアレイを表すデータ要素サブセットからのデータ要素を記憶する単一行を含んでよい。1回の計算サイクルでデータ要素の完全なサブセットを検索するプロセッサは、個別アドレス指定可能データアレイのそれぞれに対応するそれぞれのアドレスポートにアクセスすることで、複数のアドレス指定可能データアレイそれぞれの単一行に同時アクセスできる。実行ユニットは、データ要素サブセットで命令実行できる。

(もっと読む)

画像処理装置

【課題】メインメモリに格納されたバンドディスクリプタへのアクセス時間を短くできる画像処理装置を提供する。

【解決手段】画像処理装置はブロックディスクリプタ処理部及びバンドディスクリプタ処理部を備える。複数のブロックディスクリプタBLDが主走査方向及び副走査方向に並ぶ複数のブロック領域のそれぞれに割り当てられている。複数のバンドディスクリプタBADが副走査方向に並ぶ複数のバンド領域にそれぞれ割り当てられている。ブロックディスクリプタ処理部はメインメモリに画像データが格納される際に、ブロック領域の先頭の画素を含むバンド領域に割り当てられたバンドディスクリプタBADのメインメモリ上のアドレスをバンドディスクリプタ関係付けアドレスとした場合、バンドディスクリプタ関係付けアドレスの情報を含むブロックディスクリプタBLDをメインメモリに格納する処理を、複数のブロックディスクリプタBLDのそれぞれにおいて実行する。

(もっと読む)

画像処理装置、休止方法および復帰方法

【課題】休止状態への移行および休止状態からの復帰を迅速に実現することができる画像処理装置、休止方法および復帰方法を提供する。

【解決手段】画像処理装置100は、休止状態への移行要求に応答して、実行中のアプリケーション手段132,134に対して停止を通知する通知手段130と、休止状態への移行要求に対応して、主記憶装置の退避可能な1以上の区画内の情報をディスク型記憶装置26に退避するメモリ管理手段124と、主記憶装置のスナップショットであってディスク型記憶装置26に退避された情報による情報量が削減された当該スナップショットを、不揮発性記憶装置24が提供する領域を含む記憶領域に作成する作成手段122と、スナップショットの作成が完了した後、主記憶装置への電力供給を切断するリレー手段とを含む。

(もっと読む)

指紋・掌紋照合処理装置、そのデータ・キャッシング方式及びそのプログラム

【課題】照合処理時間を短縮する。

【解決手段】照合命令並びにサーチ・バイナリ・データ及びファイル・バイナリ・データを格納する共有メモリバッファ領域SD1と、これを管理するキャッシュ領域管理モジュールCM1とを備え、共有メモリバッファ領域SD1は、照合命令及びサーチ・バイナリ・データを格納するバイナリ・データ格納領域と、サーチ・バイナリ・データ及びファイル・バイナリ・データを複数の照合プログラムが照合可能なようにデコード化されたデータを登録するキャッシュ・データ格納領域とを有し、キャッシュ領域管理モジュールCM1は、照合プログラムから問い合わせのあったデコード化されたデータがキャッシュ・データ格納領域に存在する場合に、自身が備えるアクセス・カウント情報を更新し、かつ一定時間内にアクセス頻度の多い順にキャッシュ・データ格納領域内のデータの並び替えを行う。

(もっと読む)

画像処理装置、および画像処理装置の動作方法

【課題】画像データの転送によって生じる不具合を軽減させることが可能な技術を提供する。

【解決手段】画像処理装置1Aは、出力画像における所定画素の、入力画像上での対応位置を取得する相対座標取得部301と、対応位置の位置情報を記憶する第1記憶手段と、入力画像における入力画素の画素値を順次に読み出させる読出制御部303と、読み出された入力画素の画素値を入力とし、入力された入力画素の中から、入力画素による格子点の組を編成する編成手段と、上記位置情報に基づいて、所定画素の画素値の算出に用いる対応位置周辺の周辺画素の画素値が読み出されたか否かを判定する判定手段と、周辺画素が読み出されたと判定された場合に、格子点の組を構成する画素の画素値を、所定画素に関する周辺画素の画素値として記憶するローカルメモリと、上記周辺画素の画素値を用いた補間によって、所定画素の画素値を算出する画素値算出部306と備える。

(もっと読む)

画像読取装置及び画像形成装置

【課題】原稿の重送が生じたときにユーザにかかる手間を軽減し、簡単に重送した原稿の読み取りを行わせること。

【解決手段】超音波センサ252からの出力信号に基づいて重送判断部が重送を判断すると、制御部が分岐ガイド253を切り換えて、重送状態にある原稿を第2排出トレイ255に排出させる。超音波センサ252が原稿の重送を検知しても残りの原稿の読み取りは引き続き行われる。そして、ユーザが重送された原稿ごとに原稿トレイ211に載置して原稿の読み取り再開の操作を行うと、制御部は重送された原稿から取得した画像データを画像メモリの正しいページ位置に挿入して記憶する。

(もっと読む)

画像処理装置および画像処理方法

【課題】画像メモリのアクセス回数を削減することができる画像処理装置および画像処理方法を提供する。

【解決手段】

画像処理部10に搭載されていた画像データ処理部33を画像メモリコントローラ30に搭載させ、併せてアドレス変換部32、制御部31を搭載する構成とする。また、画像メモリ20の仮想読み出しアドレスエリアを定義することによって、メモリ使用量を減らし、メモリアクセス回数を減らすことができ、通信速度の向上を図る。

(もっと読む)

メモリコントローラ、画像処理システムおよびメモリアクセスの制御方法

【課題】 画像データを読み書きする半導体メモリのアクセス効率を向上する。

【解決手段】 アクセスコスト計算部は、読み出しアクセスおよび書き込みアクセスの少なくともいずれかに必要なサイクル数をアクセスコストとして複数のメモリマップ毎に計算する。メモリマップ選択部は、メモリマップの中からアクセスコストが最も低いメモリマップを選択する。パラメータ変換部は、メモリマップ選択部が選択したメモリマップに基づいて、アクセスアドレスを変換する。アクセス制御部は、変換されたアクセスアドレスに基づいて半導体メモリにアクセスするための制御信号を生成する。アクセスコストの低いメモリマップを用いて半導体メモリにアクセスすることで、半導体メモリのアクセス効率を向上できる。

(もっと読む)

画像処理装置および画像処理方法

【課題】画像変形処理に要するメモリ量を低減する技術を提供する。

【解決手段】画像処理装置は、変形前画像から画像領域内に変形後画像を生成する処理部を備える。この処理部は、画像領域の一部を構成する対象ブロックを設定する。そして、対象ブロックに対応づけられた変形前画像内の参照ブロックの画像を参照して対象ブロック内に画像を生成する。変形後画像の全体は、対象ブロックを画像領域内で順次移動して、移動後の対象ブロック内の画像を生成することにより生成される。この対象ブロックの画像の生成に先立って、参照ブロックの最大ブロックサイズが算出され、その大きさの画像を格納しうるように、メモリ領域が確保される。対象ブロックの画像は、対象ブロックに対応づけられた参照ブロックの画像をメモリ領域に格納するとともに、メモリ領域に格納された参照ブロックの画像を参照して生成される。

(もっと読む)

画像処理装置

【課題】フレーム画像の分割後の各ブロック画像に対してそれぞれ巡回型の画像処理を行うことが可能な画像処理装置を提供することを目的とする。

【解決手段】画像生成部2から出力されるフレーム画像を記憶部3に書き込む書込み部4と、記憶部3に書き込まれたフレーム画像を複数のブロック画像に分割して読み出す読出し部7と、画像処理後の複数のブロック画像を記憶部3に書き込む書込み部5と、記憶部3に書き込まれた複数のブロック画像を順次読み出す読出し部8と、読出し部7からのブロック画像と、読出し部8からのブロック画像とに基づいて、画像処理を行う巡回型画像処理部10と、書込み部4、5のそれぞれの書込み動作を制御する書込み制御部6と、読出し部7、8のそれぞれの読出し動作を制御する読出し制御部9とを備えて画像処理装置1を構成する。

(もっと読む)

検査システム、および検査システムにおける検出画像の処理方法

【課題】

半導体ウェハを検査する検査システムにおいて、取得した画像の検査方向を考慮した回路を追加しなくても、画像の比較検査を行うことができる検査システムを提供する。

【解決手段】

検査対象を電子ビームまたは光で走査して画像データを生成する検出部,画像データを格納する検査処理用メモリ,検査処理用メモリに格納された画像データを読み出して検査処理を行う検査処理部,画像データに制御情報を付加する制御情報付加部を備え、検査処理部は、付加された制御情報に基づいて画像データを読み出す構成とした。

(もっと読む)

フィルタマトリクス生成装置およびこれを用いたフィルタ装置

【課題】 フィルタマトリクス生成装置を構成するマトリクス生成部とラインメモリ部間のリード、ライト動作を減少させ、省電力効果を高める。

【解決手段】 マトリクス生成部9は、メモリ要素ラインが複数段配列される。第1〜第N−1のラインメモリ部11〜15は、ライン毎の画像データを入力し、最下位段からライン移行させながら格納してマトリクスデータを生成する。第1〜第N−1のラインメモリ部11〜15は、ライン毎の画像データをラインバッファ11a〜15aに格納し、画像データの同一値を検出設定し、1ライン分が同一値であれば、この同一値をマトリクス生成部9のラインに格納制御する。第1〜第N−1のラインメモリ部11〜15は同一値を次段の第2〜第N−1ラインメモリ部13〜15に設定する。

(もっと読む)

画像処理装置

【課題】低コストで処理性能を向上することができる画像処理装置を提供すること。

【解決手段】画像処理装置100は、ビデオ入力部140と描画部150とビデオ出力部160がアクセスするバンクを複数のフレームメモリ120,130に分けて割り当て、ビデオ入力部140と描画部150とビデオ出力部160といったマスタ部からのアクセス要求を調停し、それぞれのフレームメモリ120,130に複数のマスタ部が並行にアクセスできるようにデータ転送を制御するメモリコントローラ部190を備える。

(もっと読む)

メモリ制御装置、メモリ制御装置の制御方法、プログラム及び記憶媒体

【課題】メモリアクセス効率に優れたメモリ制御技術を提供すること。

【解決手段】メモリ制御装置は、バスマスタから入力された読出しの対象となるデータのアドレス情報と、予め設定されているメモリのデータ領域のアドレスを定義する複数のディスクリプタ情報との比較を行う比較部と、比較に基づき、読出しの対象となるデータの格納領域にアクセスするためのディスクリプタ情報を取得する取得部と、取得されたディスクリプタ情報に基づき、メモリにアクセスし、メモリの格納領域からデータを読出す第1の読出し部と、取得されたディスクリプタ情報に基づき、次のアクセスに対応したデータを事前にメモリからデータを読出すための次ディスクリプタ情報を生成する生成部と、生成された次ディスクリプタ情報に基づき、メモリにアクセスし、メモリの格納領域からデータを読出す第2の読出し部と、第2の読出し部により読出されたデータを格納する格納部とを備える。

(もっと読む)

画像処理回路

【課題】画像処理回路における演算処理を高速化する。

【解決手段】画像処理モジュール10は、起動信号STAに従って動作を開始し、2ポートメモリ30中の画像データの所定のライン(例えば、3ライン目)に対する細線化処理が終了したときに、終了信号FIN1を出力する。画像処理モジュール20は、終了信号FIN1に従って動作を開始し、1画面分の細線化処理が終了したときに、所定の条件を満たす細線化が完了したか否かを判定し、完了していればその旨の判定信号RESを出力する。完了していなければ、終了信号FIN2を出力する。画像処理モジュール10は、終了信号FIN2が与えられたときには、次の回の画面処理を開始する。これにより、画像処理モジュール10によって1,3,5,…画面目の画像処理が行われ、これにほぼ並行して、画像処理モジュール20によって2,4,6,…画面目の画像処理が行われる。

(もっと読む)

1 - 20 / 51

[ Back to top ]